自适应数字预失真技术可提高无线回传通道中的频谱效率

时间:12-17

来源:互联网

点击:

Strategy Analytics公司在最近发表的调查报告中指出,到2017年回传投资尚缺少920万美元的资金缺口。这个数字表明为了维持由于移动智能设备的普及而呈指数增长的数字业务所计划的投资和实际要求投资之间的差异。鉴于成千上万的小蜂窝正被连接到宏网络从而进一步提高对带宽的要求,回传对提高用户满意度而言将显得越来越重要。

在无线回传领域,为了实现最高的频谱效率,人们竞相提高调制速率。然而,提高调制速率不是一个简单的解决方案,问题的根源还在于现有的网络架构,而且必须以最友好的运营成本(OpEx)和资本支出(CaPex)方式持续演进。如果基础系统没有作好准备,从工业标准的256QAM过渡到1024QAM甚至更高阶的调制是不可行的。每一代调制的升级都需要链路预算额外改善3dB。在模拟领域,这个3dB可以来自倍增发射机的输出功率或提高天线增益来实现。

由于运营商的运营成本与天线尺寸和重量紧密关联,因此更高天线增益并不是一个理想的路线。更大的天线通常意味着更高的购买和安装成本。提高发射功率也许是一个值得考虑的解决方案,但同样需要在成本和功率放大器线性度、相位噪声和散热等方面的改进之间做出权衡。

这些挑战可以在数字领域得到有效解决。使用功能更强的前向纠错技术、进而实现更高的接收信号电平是迄今支持向更高阶调制发展的方法之一。在点到点无线回传中较少使用的另外一种方法是数字预失真,它的主要目的是线性化功放(PA)的特性。线性化可以通过功率回退(back-off)增加操作某级QAM所需的增益,从而有效提升调制电平。

功放具有非线性属性,而这种属性在近饱和区域更加明显。功放的非线性可以用许多参数表征,其中重要的一些参数有:

● 三阶截取点:三阶截取点定义为三阶互调产物超过有用的一阶分量时的那个点。

● 1dB压缩点:1dB压缩点定义为放大器输出下降至低于理想线性输出1dB的那个点。

● 饱和点:饱和点是指最大输入功率被超过的点。这个点的输出被钳制为最大电压,从而导致增益压缩,直到达到最大功率。

平均输入功率和饱和输入功率之差(单位为分贝)被称为回退。这个点的位置取决于放大器特征和调制特性。由功放非线性造成的失真可以分成两大类型:

● AM/AM失真:AM/AM失真是由于不同输入功率时放大器的增益变化所引起的。

● AM/PM失真:AM/PM失真是指放大器输入信号和输出信号之间的相位变化。

为了使预失真算法生效,关键是要有一个好的模型来捕获功放中的非线性效应。放大器的线性化通常是应用被称为预失真的非线性传输函数反函数实现的。这些非线性传输函数可以被测量或近似。也可以用自适应算法会聚到合适非线性系数,并做多项式近似。举例来说,如果不能设计多项式的精确反函数,可以设计一个不同的多项式作为近似反函数。

转到下一页

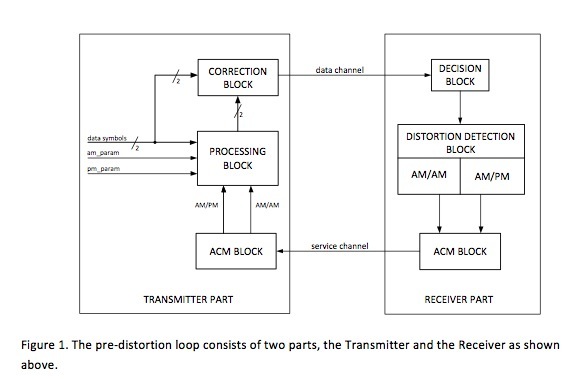

在基于赛灵思现场可编程门阵列(FPGA)的点到点无线回传调制解调器中实现的数字预失真(DPD)算法被称为硬件嵌入式自适应数字预失真。调制解调器的接收部分包含残留AM/AM和AM/PM估算器,而发射部分包含处理和校正模块,非线性传输反函数的计算在这里完成,并应用于输出信号。

闭环自适应数字预失真算法如图1所示。在数字预失真算法方案中,信号在经过功放之前必须先经过预失真器。

图1:预失真环路包括两个部分——发送部分和接收部分,如上图所示。

失真检测模块接收来自判决模块的数据/信息,并使用私有算法连续计算接收符号中的残留AM/AM和AM/PM电平。接收部分的ACM模块接收估算的AM/AM和AM/PM值,然后通过受高度保护的服务通道将它们发送给发送部分的ACM模块。接收部分的ACM模块将解码后的AM/AM和AM/PM值传送给处理模块,由处理模块逐个计算非线性失真反函数中的自变量。

自适应数字预失真性能可以在测量不同射频系统中的直接链路衰落余量的基础上进行评估。为了实现更高阶的调制,高效的功放设计可以填充3dB互调步距来提升到下个调制等级,从而允许更高的频谱效率和数据吞吐量。如果不想转到更高的调制阶数,那么这个增益可以用来降低功耗以优化功放成本。

自适应数字预失真的其它优势表现在:减少相邻通道辐射或带外失真,减少带内失真,提高功率效率,进而增加直接链路衰落余量。

作为背景介绍,赛灵思在1024QAM点到点微波调制解调器IP解决方案中使用了自适应数字预失真算法。这种解决方案独立于所使用的任何特殊类型的功放。设计采用完全硬件嵌入式,因此不需要基于软件的CPU子系统参与处理。Xilinx Artix-7、Kintex-7 FPGA和Zynq-7000所有可编程SoC都能提供大容量的千兆位级微波调制解调器IP。

原文作者:Tarmo Pihl,Manishh Sinha,赛灵思公司

放大器 电压 赛灵思 FPGA 嵌入式 射频 Xilinx SoC 相关文章:

- FPGA中嵌入式存储器模块的设计(03-28)

- FPGA高速收发器设计原则(03-11)

- 基于CPLD的CCD信号发生器的研究(04-08)

- FPGA在锁相频率合成中的应用(06-23)

- 基于CPLD的智能宽带去边沿抖动技术(07-24)

- 关于CPLD和接触式图像传感器的图像采集系统(07-26)