FPGA研发之道(11)-设计不是凑波形(一)FIFO(上)

时间:12-04

来源:互联网

点击:

作者:阿昏豆

FIFO是FPGA内部一种常用的资源,可以通过FPGA厂家的的IP生成工具生成相应的FIFO。FIFO可分为同步FIFO和异步FIFO,其区别主要是,读写的时钟是否为同一时钟,如使用一个时钟则为同步FIFO,读写时钟分开则为异步FIFO。一般来说,较大的FIFO可以选择使用内部BLOCK RAM资源,而小的FIFO可以使用寄存器资源例化使用。

一般来说,FIFO的主要信号包括:

实际使用中,可编程满的信号(XILINX 的FIFO)较为常用,ALTERA的FIFO中,可以通过写深度(即写入多少的数据值)来构造其可编程满信号。通过配置threshold(门限)的值可以设定可编程满起效时的FIFO深度。

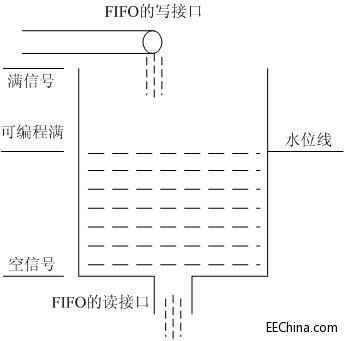

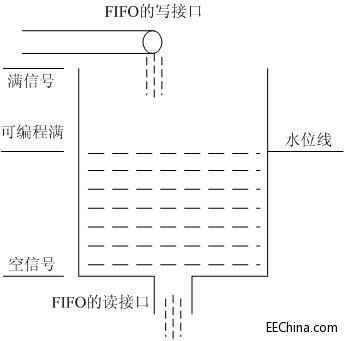

上图所示为FIFO的模型,可以看做一个漏桶模型,其中输入、输出、满信号、空信号、可编程满等信号如图所示,一目了然。 其中threshold信号可以看做水位线,通过此信号可以设置可编程满信号。FIFO的其他的信号也大都与其深度相关,如有特殊需求,可通过厂商提供的IP生成工具的图形界面进行选择使用。

FIFO的使用场景有多种,其中主要如下所示:

(1) 数据的缓冲,如模型图所示,如果数据的写入速率高,但间隔大,且会有突发;读出速率小,但相对均匀。则通过设置相应深度的FIFO,可以起到数据暂存的功能,且能够使后续处理流程平滑,避免前级突发时,后级来不及处理而丢弃数据。

(2) 时钟域的隔离。对于不同时钟域的数据传递,则数据可以通过FIFO进行隔离,避免跨时钟域的数据传输带来的设计与约束上的复杂度。

FIFO设计中有两个需要注意事项,首先,不能溢出,即满后还要写导致溢出,对于数据帧的操作来说,每次写入一个数据帧时,如果每写一个宽度(FIFO的宽度)的数据,都要检查满信号,则处理较为复杂,如果在写之前没满,写过程不检查,则就容易导致溢出。因此可编程满的设定尤为必要,通过设置可编程满的水位线,保证能够存储一个数据帧,这样写之前检查可编程满即可。

其次,另一更容易出错的问题,就是空信号。对于FIFO来说,在读过程中出现空信号,则其没有代表该值没有被读出,对于读信号来说,如设定读出一定长度的值,只在一开始检测非空,如状态机的触发信号,容易出现过程中间也为空的信号,会导致某些数据未读出,特别是写速满而读速快的场景下。 因此rden与!empty信号要一起有效才算将数据读出。

空信号处理相对容易出错,懒人自有笨方法,下面介绍一种应用于数据帧处理的FIFO使用方式,只需在读开始检测空信号即可,可以简化其处理读数据的流程:

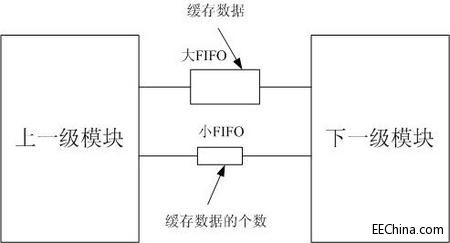

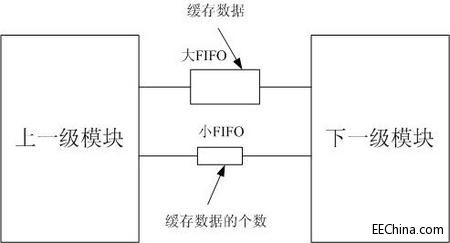

其处理结构如上图所示,数据缓存以大FIFO(BLOCK RAM实现)为主,而每存储完毕一个数据帧向小FIFO(寄存器实现)内写入值。当小FIFO标示非空时,则标示大FIFO中已存储一个整帧。则下一级模块可以只需检测小FIFO非空时,从而读出一个整帧,过程中大FIFO一直未非空,可以不用处理非空信号,从而简化设计和验证的流程。

此外还有FIFO其他应用方式,下节接着介绍。

FIFO是FPGA内部一种常用的资源,可以通过FPGA厂家的的IP生成工具生成相应的FIFO。FIFO可分为同步FIFO和异步FIFO,其区别主要是,读写的时钟是否为同一时钟,如使用一个时钟则为同步FIFO,读写时钟分开则为异步FIFO。一般来说,较大的FIFO可以选择使用内部BLOCK RAM资源,而小的FIFO可以使用寄存器资源例化使用。

一般来说,FIFO的主要信号包括:

| 信号 | 数据信号 |

| 读信号 | rd_en |

| 读数据 | dout |

| 读空信号 | empty |

| 写信号 | wr_en |

| 写数据 | din |

| 写满信号 | full |

实际使用中,可编程满的信号(XILINX 的FIFO)较为常用,ALTERA的FIFO中,可以通过写深度(即写入多少的数据值)来构造其可编程满信号。通过配置threshold(门限)的值可以设定可编程满起效时的FIFO深度。

上图所示为FIFO的模型,可以看做一个漏桶模型,其中输入、输出、满信号、空信号、可编程满等信号如图所示,一目了然。 其中threshold信号可以看做水位线,通过此信号可以设置可编程满信号。FIFO的其他的信号也大都与其深度相关,如有特殊需求,可通过厂商提供的IP生成工具的图形界面进行选择使用。

FIFO的使用场景有多种,其中主要如下所示:

(1) 数据的缓冲,如模型图所示,如果数据的写入速率高,但间隔大,且会有突发;读出速率小,但相对均匀。则通过设置相应深度的FIFO,可以起到数据暂存的功能,且能够使后续处理流程平滑,避免前级突发时,后级来不及处理而丢弃数据。

(2) 时钟域的隔离。对于不同时钟域的数据传递,则数据可以通过FIFO进行隔离,避免跨时钟域的数据传输带来的设计与约束上的复杂度。

FIFO设计中有两个需要注意事项,首先,不能溢出,即满后还要写导致溢出,对于数据帧的操作来说,每次写入一个数据帧时,如果每写一个宽度(FIFO的宽度)的数据,都要检查满信号,则处理较为复杂,如果在写之前没满,写过程不检查,则就容易导致溢出。因此可编程满的设定尤为必要,通过设置可编程满的水位线,保证能够存储一个数据帧,这样写之前检查可编程满即可。

其次,另一更容易出错的问题,就是空信号。对于FIFO来说,在读过程中出现空信号,则其没有代表该值没有被读出,对于读信号来说,如设定读出一定长度的值,只在一开始检测非空,如状态机的触发信号,容易出现过程中间也为空的信号,会导致某些数据未读出,特别是写速满而读速快的场景下。 因此rden与!empty信号要一起有效才算将数据读出。

空信号处理相对容易出错,懒人自有笨方法,下面介绍一种应用于数据帧处理的FIFO使用方式,只需在读开始检测空信号即可,可以简化其处理读数据的流程:

其处理结构如上图所示,数据缓存以大FIFO(BLOCK RAM实现)为主,而每存储完毕一个数据帧向小FIFO(寄存器实现)内写入值。当小FIFO标示非空时,则标示大FIFO中已存储一个整帧。则下一级模块可以只需检测小FIFO非空时,从而读出一个整帧,过程中大FIFO一直未非空,可以不用处理非空信号,从而简化设计和验证的流程。

此外还有FIFO其他应用方式,下节接着介绍。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)