如何在FPGA中实现状态机

时间:04-03

来源:互联网

点击:

作者:EADS Astrium公司首席工程师 Adam Taylor

FPGA常常用于执行基于序列和控制的行动,比如实现一个简单的通信协议。对于设计人员来说,满足这些行动和序列要求的最佳方法则是使用状态机。状态机是在数量有限的状态之间进行转换的逻辑结构。一个状态机在某个特定的时间点只处于一种状态。但在一系列触发器的触发下,将在不同状态间进行转换。

理论上讲,状态机可以分为Moore状态机和Mealy状态机两大类。它们之间的差异仅在于如何生成状态机的输出。Moore状态机的输出仅为当前状态的函数。典型的例子就是计数器。而Mealy状态机的输出是当前状态和输入的函数。典型的例子就是Richards控制器。

定义状态机

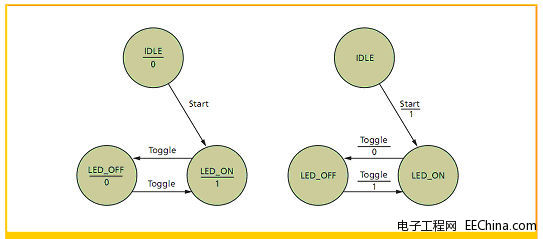

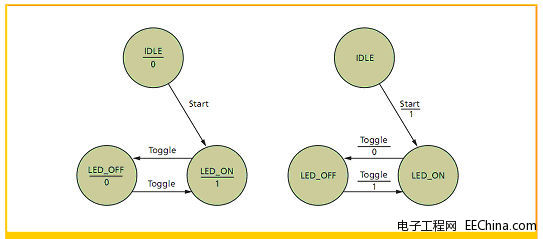

当需要定义一个状态机时,首先要绘制一张状态图。状态图可用来显示状态、状态间的转换和状态机的输出。图1显示了Moore状态机的状态图(左)和Mealy状态机的状态图(右)。

图1,用于开/关LED的Moore状态机(左)和Mealy状态机(右)的状态图。

如果您要在物理组件中实现这些状态图(工程师在FPGA问世之前就是这么做的),首先就得生成当前状态和后续状态表,然后生成实现状态机所需的逻辑。不过由于我们将使用FPGA来实现设计,因此我们可以直接从状态转换图开始工作。

算法状态图

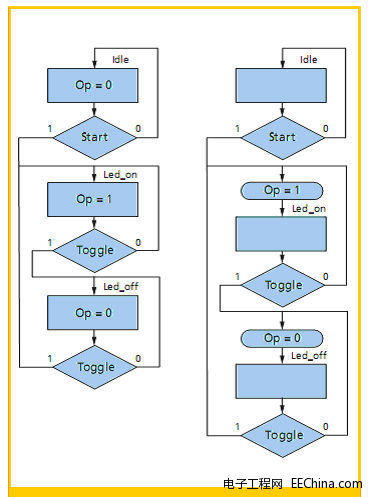

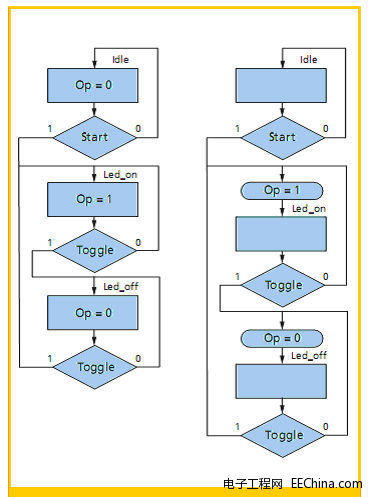

虽然有许多状态机是使用图1所示的状态图方法进行设计的,但另外还有一种描述状态机行为的方法,这就是算法状态图法。ASM图(图2)在外观上更加接近软件工程流程图。它由三个基本部分构成:

1. 状态框。它与状态名称有关,并包含Moore状态输出列表。

2. 决策框。如果检验某条件为真,则进行下一状态的判断。

3. 条件输出框。让状态机根据当前状态和输入描述Mealy输出。

一些工程师认为,如果使用VHDL等硬件描述语言,则采用ASM格式进行描述的状态机更易于映射到实现方案中。

图2,用于图1所示的状态机(Moore状态机(左),Mealy状态机(右))的算法状态图。

Moore和Mealy:应该选择哪个?

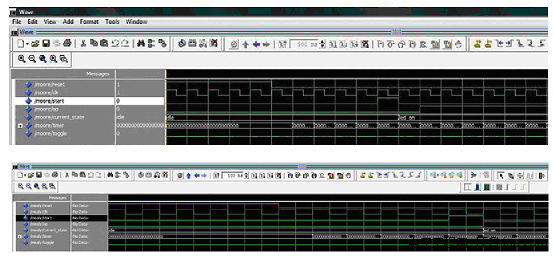

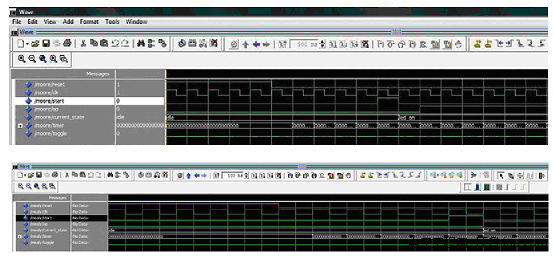

实现Moore状态机还是Mealy状态机,取决于状态机需要实现的功能,以及特定的反应次数要求。两种状态机之间的最大差别在于状态机如何对输入做出反应。在输入和设置的适当输出之间,Moore状态机一般有一个时钟周期的延迟。这就意味着Moore状态机无法对输入变化立即做出反应,这点在图3中可以清楚地看到。而Mealy状态机则能够立即对输入做出反应,这通常意味着:实现相同的函数,Mealy状态机比Moore状态机需要更少的状态。Mealy状态机的不足之处就是在与另一个状态机进行通信时,如果输出出乎意料地严重依赖于其它事件的序列或时序,就可能会发生紊乱情况。

图3,截屏显示了Moore状态机(上)和Mealy状态机(下)输出的仿真结果。

当然,并非只能使用单纯的Moore状态机或Mealy状态机,也可以将这两种状态机混合使用,从而更有效地实现所需的函数。比如说,用于接收RS232串行数据的状态机就可以是混合机。

实现状态机

使用VHDL这样的高级语言,可以轻松地直接从状态图实现状态机。VHDL支持多种枚举类型,方便您定义实际的状态名称。举例如下:

TYPE state IS (idle, led_on, led_off) ;

上面的类型定义对应的是图1中所示的状态图,即用于在按下按钮时切换发光二极管开/关的状态机。

实现状态机有许多种方法,可分为两类基本方法。第一类基本方法就是一次性将所有内容集成到单个进程中。第二类基本方法是双进程法,将组合逻辑和顺序逻辑分开。

一般来说,大多数工程师都倾向于实现单进程状态机。与传统上讲授的双进程法相比,这种方法具有以下优势:

●可以避免组合过程中信号覆盖不完全造成的闭锁风险。

●状态机的输出与时钟保持同步。

●通常比双进程实现方案更容易调试。

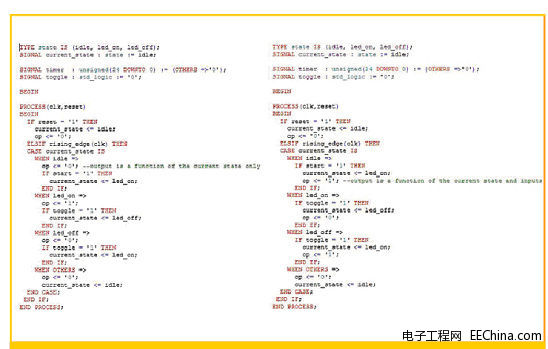

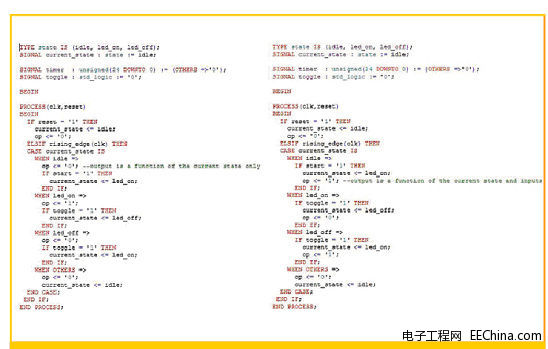

无论您决定采用哪一种方法来实现状态机,都需要使用CASE语句来评估下一状态的判定和任何输出,如图4所示。该图并行比较了使用单进程法的Moore状态机(左)和Mealy状态机(右)。

图4,使用VHDL语言的Moore状态机(左)和Mealy状态机。

状态机编码

状态变量存储在触发器中,使用下一时钟边缘上的下一状态进行更新(即使没有状态变化也是如此)。如何使用触发器来表示状态值具体取决于状态的数量和是否选择用某种特定的方法来管理综合工具。状态编码最常见的三种类型是:

●顺序码——状态编码遵循传统的状态二进制序列。

●格雷码——除了状态编码使用格雷码,且状态编码串之间只有一个位变化外,其它基本与顺序编码方法类似。

●独热码——这种方法在状态机中为每一种状态分配一个触发器。只有一个触发器当前设置为高位,其余均设置为低位。故称为“独热”。

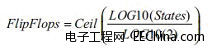

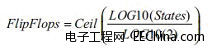

顺序编码和格雷编码都需要一定数量的触发器,可以通过下列等式来确定:

相比之下,独热编码法所需的触发器数量和状态数量一样多。

状态编码的自动分配取决于状态机所包含的状态数量。同时还需要考虑您选择使用的综合工具。您可以根据下列经验法则来选取编码方法:

●顺序:少于5种状态。

●独热:5-50种状态。

●格雷:多于50种状态。

一般情况下您不必去考虑使用哪一种状态编码方法,而是让综合引擎工具确定合适的实现方案,只在选择的方法出现问题时进行考虑。但是,如果您要全盘自行掌控,并定义状态编码方法,也没必要手动操作,只需使用状态编码为每一种状态设定常数即可。相反地,可以使用代码中的一个属性来驱动综合工具,从而选择特定的编码方法。具体如下所示:

TYPE state IS (idle, led_on, led_off) ;

SIGNAL current_state : state := idle;

ATTRIBUTE syn_encoding STRING;

ATTRIBUTE syn_encoding OF current_state :

SIGNAL IS “sequential”;

其中“sequential”也可以是“gray”和“onehot”。您还可以通过结合使用“safe”属性来确保在状态机进入非法状态时能够恢复到有效状态。

另外,您也可以使用syn_encoding属性直接定义状态编码的值。例如,假设您想要使用下列状态编码法来对三态状态机进行编码:Idle = “11,”led_on = “10,” led_off = “01(与较传统的顺序“00”、“01”和“10”不同):

TYPE state IS (idle, led_on, led_off) ;

SIGNAL current_state : state := idle;

ATTRIBUTE syn_encoding STRING;

ATTRIBUTE syn_encoding OF current_state :

SIGNAL IS “sequential”;

工程师负责在综合工具中使用正确的设置,以确保该工具不会忽略任何属性。例如,赛灵思XST工具要求将FSM选项设置为USER,而Synopsys的Synplify则要求关闭FSM编译器。

前面给出的等式可确定状态机实现方案所需的触发器数量。由于不是所有的状态机都是2的幂次方,因此某些状态在设计中将不会用到。实现状态机的工程师必须负责确保未使用的状态在设计中得到妥善处理。可以采用几种适用于多种设计的基本技巧来实现这一目标。对于高度可靠的安全关键型设计,则需要采用其它更高级的技巧。

不过对于大多数应用来说,只需要确保状态机能够妥善地处理未使用的状态并在进入非法状态时能够正确地恢复。要做到这一点有两种主要的方法。第一种方法是使用综合工具实现一个安全的状态机。综合工具通常会插入额外的逻辑,用于检测非法状态并将状态机返回到有效状态。第二种方法是加强对实现逻辑的控制,声明所有2的幂次方状态机的状态,并使用另一属性来确保即便是在没有入口条件下,2的幂次方状态机的状态也不会被优化掉。这意味着除非出错(单粒子翻转等),状态机内部的任何条件都不会进入状态。下面的代码显示了通过使用属性以防止清除未使用的状态。

TYPE state IS (idle, led_on, led_off) ;

SIGNAL current_state : state := idle;

ATTRIBUTE syn_keep BOOLEAN;

ATTRIBUTE syn_keep OF current_state :

SIGNAL IS TRUE”;

简而言之,安全高效的状态机设计对于任何使用FPGA的工程师而言都是一项重要技能。选择Moore状态机、Mealy状态机还是混合机取决于整个系统的需求。无论选择哪种类型的状态机,充分掌握实现方案所需的工具和技巧,将确保您实现最佳解决方案。

FPGA常常用于执行基于序列和控制的行动,比如实现一个简单的通信协议。对于设计人员来说,满足这些行动和序列要求的最佳方法则是使用状态机。状态机是在数量有限的状态之间进行转换的逻辑结构。一个状态机在某个特定的时间点只处于一种状态。但在一系列触发器的触发下,将在不同状态间进行转换。

理论上讲,状态机可以分为Moore状态机和Mealy状态机两大类。它们之间的差异仅在于如何生成状态机的输出。Moore状态机的输出仅为当前状态的函数。典型的例子就是计数器。而Mealy状态机的输出是当前状态和输入的函数。典型的例子就是Richards控制器。

定义状态机

当需要定义一个状态机时,首先要绘制一张状态图。状态图可用来显示状态、状态间的转换和状态机的输出。图1显示了Moore状态机的状态图(左)和Mealy状态机的状态图(右)。

图1,用于开/关LED的Moore状态机(左)和Mealy状态机(右)的状态图。

如果您要在物理组件中实现这些状态图(工程师在FPGA问世之前就是这么做的),首先就得生成当前状态和后续状态表,然后生成实现状态机所需的逻辑。不过由于我们将使用FPGA来实现设计,因此我们可以直接从状态转换图开始工作。

算法状态图

虽然有许多状态机是使用图1所示的状态图方法进行设计的,但另外还有一种描述状态机行为的方法,这就是算法状态图法。ASM图(图2)在外观上更加接近软件工程流程图。它由三个基本部分构成:

1. 状态框。它与状态名称有关,并包含Moore状态输出列表。

2. 决策框。如果检验某条件为真,则进行下一状态的判断。

3. 条件输出框。让状态机根据当前状态和输入描述Mealy输出。

一些工程师认为,如果使用VHDL等硬件描述语言,则采用ASM格式进行描述的状态机更易于映射到实现方案中。

图2,用于图1所示的状态机(Moore状态机(左),Mealy状态机(右))的算法状态图。

Moore和Mealy:应该选择哪个?

实现Moore状态机还是Mealy状态机,取决于状态机需要实现的功能,以及特定的反应次数要求。两种状态机之间的最大差别在于状态机如何对输入做出反应。在输入和设置的适当输出之间,Moore状态机一般有一个时钟周期的延迟。这就意味着Moore状态机无法对输入变化立即做出反应,这点在图3中可以清楚地看到。而Mealy状态机则能够立即对输入做出反应,这通常意味着:实现相同的函数,Mealy状态机比Moore状态机需要更少的状态。Mealy状态机的不足之处就是在与另一个状态机进行通信时,如果输出出乎意料地严重依赖于其它事件的序列或时序,就可能会发生紊乱情况。

图3,截屏显示了Moore状态机(上)和Mealy状态机(下)输出的仿真结果。

当然,并非只能使用单纯的Moore状态机或Mealy状态机,也可以将这两种状态机混合使用,从而更有效地实现所需的函数。比如说,用于接收RS232串行数据的状态机就可以是混合机。

实现状态机

使用VHDL这样的高级语言,可以轻松地直接从状态图实现状态机。VHDL支持多种枚举类型,方便您定义实际的状态名称。举例如下:

TYPE state IS (idle, led_on, led_off) ;

上面的类型定义对应的是图1中所示的状态图,即用于在按下按钮时切换发光二极管开/关的状态机。

实现状态机有许多种方法,可分为两类基本方法。第一类基本方法就是一次性将所有内容集成到单个进程中。第二类基本方法是双进程法,将组合逻辑和顺序逻辑分开。

一般来说,大多数工程师都倾向于实现单进程状态机。与传统上讲授的双进程法相比,这种方法具有以下优势:

●可以避免组合过程中信号覆盖不完全造成的闭锁风险。

●状态机的输出与时钟保持同步。

●通常比双进程实现方案更容易调试。

无论您决定采用哪一种方法来实现状态机,都需要使用CASE语句来评估下一状态的判定和任何输出,如图4所示。该图并行比较了使用单进程法的Moore状态机(左)和Mealy状态机(右)。

图4,使用VHDL语言的Moore状态机(左)和Mealy状态机。

状态机编码

状态变量存储在触发器中,使用下一时钟边缘上的下一状态进行更新(即使没有状态变化也是如此)。如何使用触发器来表示状态值具体取决于状态的数量和是否选择用某种特定的方法来管理综合工具。状态编码最常见的三种类型是:

●顺序码——状态编码遵循传统的状态二进制序列。

●格雷码——除了状态编码使用格雷码,且状态编码串之间只有一个位变化外,其它基本与顺序编码方法类似。

●独热码——这种方法在状态机中为每一种状态分配一个触发器。只有一个触发器当前设置为高位,其余均设置为低位。故称为“独热”。

顺序编码和格雷编码都需要一定数量的触发器,可以通过下列等式来确定:

相比之下,独热编码法所需的触发器数量和状态数量一样多。

状态编码的自动分配取决于状态机所包含的状态数量。同时还需要考虑您选择使用的综合工具。您可以根据下列经验法则来选取编码方法:

●顺序:少于5种状态。

●独热:5-50种状态。

●格雷:多于50种状态。

一般情况下您不必去考虑使用哪一种状态编码方法,而是让综合引擎工具确定合适的实现方案,只在选择的方法出现问题时进行考虑。但是,如果您要全盘自行掌控,并定义状态编码方法,也没必要手动操作,只需使用状态编码为每一种状态设定常数即可。相反地,可以使用代码中的一个属性来驱动综合工具,从而选择特定的编码方法。具体如下所示:

TYPE state IS (idle, led_on, led_off) ;

SIGNAL current_state : state := idle;

ATTRIBUTE syn_encoding STRING;

ATTRIBUTE syn_encoding OF current_state :

SIGNAL IS “sequential”;

其中“sequential”也可以是“gray”和“onehot”。您还可以通过结合使用“safe”属性来确保在状态机进入非法状态时能够恢复到有效状态。

另外,您也可以使用syn_encoding属性直接定义状态编码的值。例如,假设您想要使用下列状态编码法来对三态状态机进行编码:Idle = “11,”led_on = “10,” led_off = “01(与较传统的顺序“00”、“01”和“10”不同):

TYPE state IS (idle, led_on, led_off) ;

SIGNAL current_state : state := idle;

ATTRIBUTE syn_encoding STRING;

ATTRIBUTE syn_encoding OF current_state :

SIGNAL IS “sequential”;

工程师负责在综合工具中使用正确的设置,以确保该工具不会忽略任何属性。例如,赛灵思XST工具要求将FSM选项设置为USER,而Synopsys的Synplify则要求关闭FSM编译器。

前面给出的等式可确定状态机实现方案所需的触发器数量。由于不是所有的状态机都是2的幂次方,因此某些状态在设计中将不会用到。实现状态机的工程师必须负责确保未使用的状态在设计中得到妥善处理。可以采用几种适用于多种设计的基本技巧来实现这一目标。对于高度可靠的安全关键型设计,则需要采用其它更高级的技巧。

不过对于大多数应用来说,只需要确保状态机能够妥善地处理未使用的状态并在进入非法状态时能够正确地恢复。要做到这一点有两种主要的方法。第一种方法是使用综合工具实现一个安全的状态机。综合工具通常会插入额外的逻辑,用于检测非法状态并将状态机返回到有效状态。第二种方法是加强对实现逻辑的控制,声明所有2的幂次方状态机的状态,并使用另一属性来确保即便是在没有入口条件下,2的幂次方状态机的状态也不会被优化掉。这意味着除非出错(单粒子翻转等),状态机内部的任何条件都不会进入状态。下面的代码显示了通过使用属性以防止清除未使用的状态。

TYPE state IS (idle, led_on, led_off) ;

SIGNAL current_state : state := idle;

ATTRIBUTE syn_keep BOOLEAN;

ATTRIBUTE syn_keep OF current_state :

SIGNAL IS TRUE”;

简而言之,安全高效的状态机设计对于任何使用FPGA的工程师而言都是一项重要技能。选择Moore状态机、Mealy状态机还是混合机取决于整个系统的需求。无论选择哪种类型的状态机,充分掌握实现方案所需的工具和技巧,将确保您实现最佳解决方案。

FPGA LED VHDL 仿真 二极管 赛灵思 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)