应用串行NOR闪存提升内存处理能力

时间:12-13

来源:互联网

点击:

Improve Memory Throughput with SPI NOR Flash

■ Spansion公司

在嵌入式系统中,NOR闪存一直以来仍然是较受青睐的非易失性内存,NOR器件的低延时特性可以接受代码执行和数据存储在一个单一的产品。虽然NAND记忆体已成为许多高密度应用的首选解决方案,但NOR仍然是低密度解决方案的首选之一。

未来闪存产品具有快速发展的趋势,可以发现,闪存产品从低密度、低性能、低功能的发展特点转变为高密度、高性能、高功能的发展特点。Spansion的NOR闪存广泛运用于汽车电子、医疗设备、通讯设备、机顶盒等。

SPI Flash特性

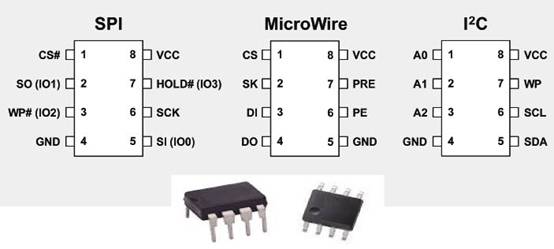

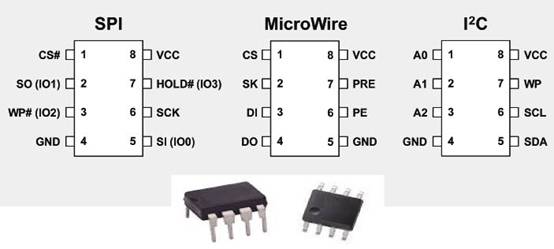

SPI串行结构的EEPROM最早出现于20世纪80年代中期,由摩托罗拉在其MC68HC系列中首先引入,MicroWire是由国半制定的总线标准,它和SPI非常相似,只是MicroWire的时钟极性CPOL和时钟相位CPHA是固定的,均为0。I2C也是出现在80年代,由Philips制定,它通过一条数据线和一条时钟线实现半双工通信,I2C总线接口实现了最简单的总线接口方式。三种标准如图1所示。

SPI和MicroWire很相近,速度非常快,且在设计中无需上拉电阻,可以支持全双工通信操作,抗干扰能力强,缺点是需要占用较多的数据总线,且需要为设备分配单独的片选信号,没有接收数据的硬板机制。对I2C总线来说,它占用的总线较少,可以多个设备共同用一根总线,支持接收数据的硬板机制,缺点是速度较低,为3.4MHz以下,只支持半双工的操作,设计时需要上拉电阻,且对噪声的干扰相对敏感。

图1 三种总线标准

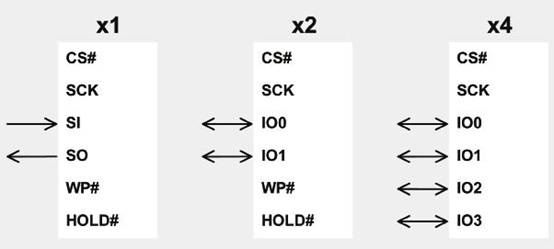

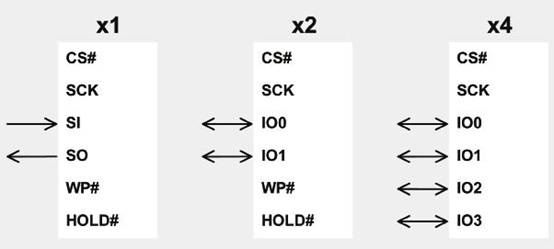

SPI的接口从传统的单进单出已经提升到双进双出或者四进四出。如图2所示,通过单向输入SI,输出SO变为双向的传输,同时将WP引脚和HOLD引脚复用为双向的IO口来实现多IO口的接口通信,其协议及基本的读写操作和原始EEPROM兼容,同时硬件上实现简单的完全兼容。

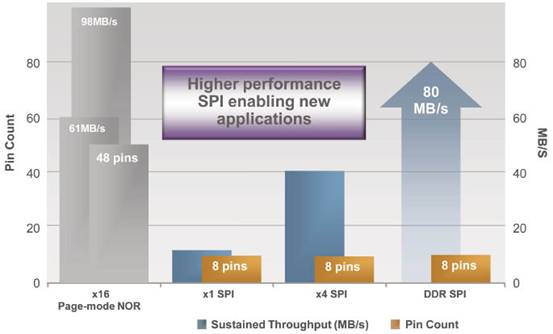

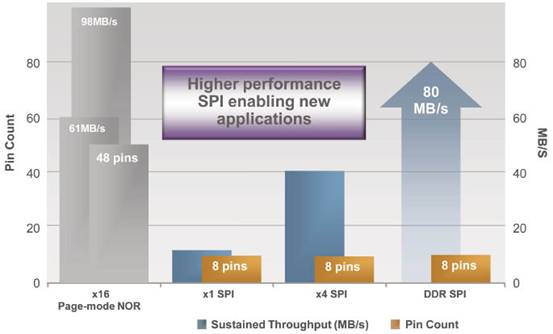

相对于传统的并行NOR Flash而言,SPI NOR Flash只需要6个引脚就能够实现单I/O,双I/O和4个I/O口的接口通信,而并行的NOR Flash则至少需要40个引脚。人们普遍使用的是标准NOR Flash异步读模式,而ADM及地址数据信号复用,这种并行NOR Flash引脚数相对较少,通过实现突发读模式,其数据输出最快可超过120MB/s,SPI具有较少的引脚,同时,通过采用DDR的方式读操作,在80MHz的时钟下,其数据输出可以达到80MB/s,甚至超过并行NOR Flash的异步读速度。

图2 SPI的接口转变

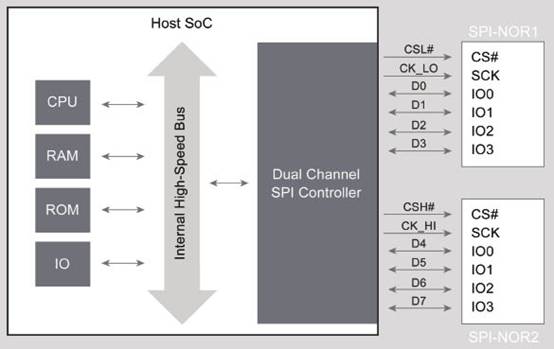

在过去的几年中,随着直接CPU 内存映射功能的支持, SPI的读操作取得了极大的进步,而传统的SPI外设控制器仍然在用于传统的SPI的读或别的操作,相比之下,通过CPU的直接读取操作,速度比通过SPI控制器来的更快,延迟低。

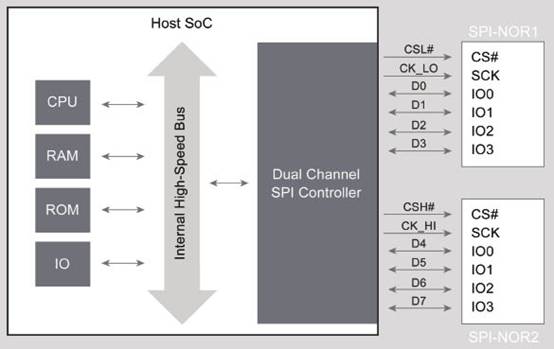

SPI双通道控制器示意图如图3所示,双通道可以使SPI的数据输出增加一倍,硬件上将片选和时钟共用的话,只需要10个引脚就能实现SPI Flash所有功能。可以考虑,实现一片SPI Flash 8bits数据的传输,从而提升SPI Flash的数据输出能力。

图3 SPI双通道控制器

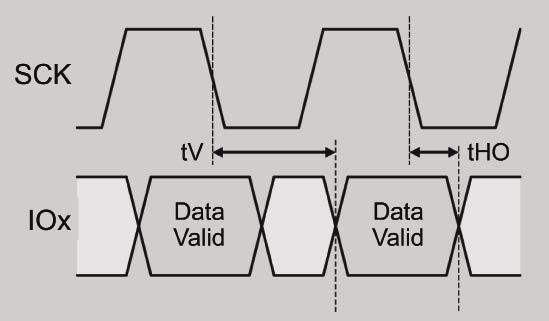

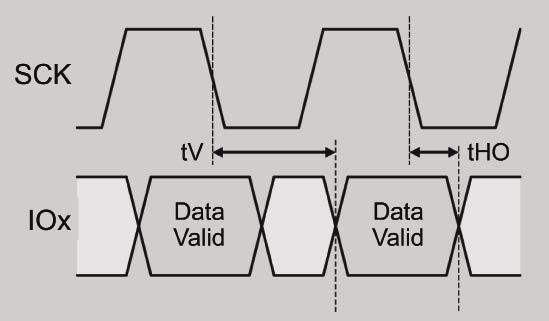

关于SPI时序对读速度的影响,如图4所示。tV是指时钟的下降沿到有效数据输出所需要的时间,一般最大为8ns。tHO是数据输出后到下一个时钟下降沿可持续的时间,一般最小值0ns。这两个参数和时钟频率一起决定了SPI Flash的最大数据输出速度。事实上,tHO在实际应用中并不能像时钟周期一样可以无限压缩,而往往都会大于0ns。

早期的4个I/O口输出协议需要对地址和数据分别串行传送。如,8个命令周期加上24个地址周期至少需要32个时钟周期完成一个读操作命令周期,如果Flash的寻址超过128Mbits,仅地址周期就需要32个时钟周期,非常耗时。

图4 SPI时序对读速度的影响

新的4个I/O口输出模式,其地址可以通过4个I/O口同时传送,如,24位地址信号仅需要6个时钟周期就可以完成,加上8个命令周期共需要14个周期完成命令,其速度比早期的4个I/O口的传输要快很多。

模式bit的应用用于通知SPI Flash下一个命令和前一个命令是同样的命令。使我们在需要重复进行读操作的时候,可以减少命令周期带来的总线开销,从而进一步提高SPI Flash的读取性能。

DDR的4 I/O口读模式由一个8bits的命令开始,而输入地址和输出的数据按照DDR的模式进行,这种模式需要协议的开销,需要8个命令时钟周期,加上3个地址时钟周期,一共11个时钟周期可以完成一个读命令操作。

通过模式bit消除可以节省重复输入相同命令时的时钟周期,完成一个DDR口的读操作仅需要3个时钟周期。

数据总线上的数据会由于时钟频率太高而出现歪斜或失真,导致数据的读错误,而DLP(data learning pattern)的功能在DDR多I/O口协议中的使用可以使Flash在时钟频率高时同样稳定地工作。DLP的功能是通过利用真实数据输出前的假数据周期,它不会影响整个命令的时钟周期,DLP的数据采用可以使主机端明确什么时候可以采用到正确的目标数据,从而提高系统在高频率SPI数据在读操作时的可靠性及稳定性。

4 I/O口的DDR读模式增加了DLP和模式bit消除模式后,只需要3个时钟周期的协议开销,目前的器件在80MHz频率下,数据输出可以达到80MB/s。

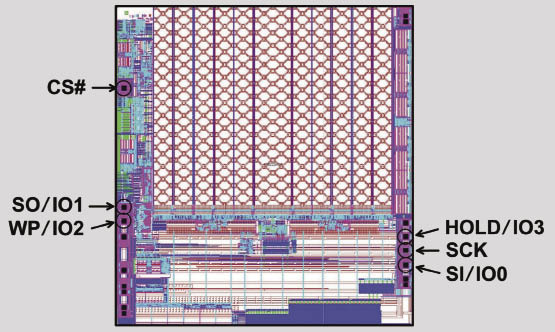

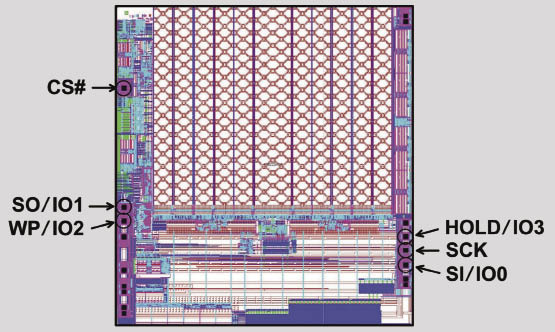

从设计的角度来说,如图5所示。芯片内部的引脚连接点的放置同样会影响到SPI Flash的数据输出速度,时钟和I/O口信号的紧凑设计会减少芯片的数据失真,从而提高SPI Flash芯片的工作速度。

图5 芯片内部的引脚连接点设计

SPI Flash未来发展

未来SPI Flash的发展需要一种简单、高效和高速接口。随着传统的应用越来越多地转向SPI Flash的存储接口,人们希望传统的一些并行NOR Flash的功能也能出现在SPI Flash中,比如Reset复位功能、宽电压功能,及以扇区为单位的写保护等功能。同时随着DDR接口被越来越多广泛地运用,低电压总线操作的支持等,数据SPI Flash将会提供更高的读性能。

低成本存储器解决方案

Spansion的FL-S是65nm工艺的产品,它具有增强的性能和丰富的功能。从产品性能上说,擦除速度快5倍以上,写速度快3倍以上,同时,最快速读功能快20%以上。从产品功能上说,容量覆盖了主流的128 Mbits~1Gbits,其封装是工业标准封装,并能实现老产品到下一代新产品的兼容。产品在安全性方面也有很大的提高,除了支持OTP以外,部分型号支持读保护功能。

目前,人们普遍使用的并行NOR Flash,如图6所示,通过异步读取的方式操作Flash,理想的时序设计基本上输出速度是达到61MB/s。而Spansion的SPI Flash页读取模式可以达到98MB/s,和传统的异步读模式不同,第一个读取周期地址时序和异步读相同,但后续的读取速度可以递增25ns,从而大大提高Flash的读取速度。总的来说,DDR的读取模式可以在极少的引脚基础上可以实现超过传统的读取速度,未来会被越来越多地被采用。

图6 Page-mode NOR读取速度优势

Spansion的FL-S性能较高,对于SPI Flash来说,成本的节省来源于三个主要方面,第一,主芯片成本降低,从传统的40个引脚或以上并行NOR Flash的支持到仅需要6个引脚的SPI Flash支持,成本会大大降低,但是如果主芯片各种芯片接口都支持的话,成本也不会明显降低。第二,SPI Flash自身的封装生产成本降低,同时从生产的成本来说,SPI由于引脚的减少会降低成本,测试成本也会降低。第三,Flash的速度提升对于客户体验会有很大的改善,会给最终客户端产品带来竞争力,如开机时间、运行速度等等。

随着竞争的国际化和知识产权保护意识的提高,工程师们对Flash芯片及芯片存储的代码安全性要求越来越高。Spansion的新系列Flash提供了非常丰富的保护功能。首先,普通的Flash可以支持扇区的写保护功能,这种保护可以是动态的也可以是永久性的,动态的就是指Flash的保护设置在掉电的时候或者复位时保护功能失效,在上电或者复位后重新需要设置。而永久性的则不会因为掉电或者复位而使保护的状态失效。大部分的Flash还提供了OTP的一次性的写入功能。部分产品特别是针对高安全性的机顶盒产品可以支持将Flash扇区的操作OTP的功能,以扇区为单位,通过设置OTP可以防止任何的写操作命令从而实现Flash存储内容的保护。另外,Spansion的65nm产品部分型号还可以实现读加密的要求,客户可以通过设置读保护密码防止Flash的内容被读取,从而保护产品的软件不会被轻易地抄袭。

在线座谈(Online Seminar)是中电网于2000年推出的创新服务,通过“视频演示+专家解说+在线问答”三位一体相结合的形式,充分发挥网络平台的便捷性,实现了先进半导体技术提供商与系统设计工程师的实时互动交流,其形式和内容都广受电子行业工程师的好评。本刊每期将挑选一些精华内容整理成文,以飨读者。欲了解更多、更详细的内容,敬请登录http://seminar.eccn.com。

问答选编

问:存储器接口可以和现在的CPUSPI接口完全兼容吗?

答:可以的,CPI所带的SPI接口可以专门用来连接SPI接口的Flash。

问:是否可以实现多I/O口技术?

答:以SPI为例, 目前有x1/x2/x4三种I/O方式,并行NOR Flash和NAND Flash 有x8/x16两种I/O方式。

问:可不可以用串行NOR Flash做程序存储器,和并行NOR Flash相比,应该注意些什么?

答:当然可以,串行Flash和传统的并行NOR Flash相比,只是接口不同(当然这种接口的不同需要控制端芯片的支持),其可靠性和稳定性和并行NOR Flash相同。存储代码的应用中,需要注意硬件上可能因为时钟频率高带来的单板干扰,软件设计中可以采用一些写保护功能体改代码存储的安全性,另外Spansion的新系列串行Flash产品还支持了硬件复位RESET功能,在一些特殊的应用中可以考虑采用。

问:产品现在应用情况如何,容量怎么样?

答:现在已经有很多的机顶盒客户,网通客户,工业类客户在使用,最新FL-S flash是业界速度(读写擦除)较快的,容量从128Mbits~512Mbits都已经量产,当然Spansion公司有全系列的嵌入式的Flash提供给客户,串型的容量从4Mbits~512Mbits,并行的容量从8Mbits~2Gbits。

问:安全性怎么样啊?

答:串行的Flash和传统的并行NOR Flash相类似,只是接口不一样。另外,65nm技术的产品Spansion公司去年上半年已经量产,工艺本身非常成熟。从应用的角度来说,如果需要进一步提高其安全性,可以采用Spansion非常丰富的各种写保护方式来保护代码,同时部分产品且支持密码加密的读保护方式,提高产品的安全性。

问:Spansion的SPI闪存目前的存取速度可到多快?

答:单I/O是fast read是133Mhz,多I/O每个是80Mhz。如果是四I/O那就是320Mhz。如果能支持DDR SPI,double data rate,最快是66MB/s。

问:产品的性价比如何?

答:由于市场竞争的关系,目前各家厂商的Flash价格相差不大,但是Spansion NOR Flash容量组合全,与其他家的产品相比,读写擦性能更高,尤其是目前的65nm系列产品FL-S和GL-S。

问:产品的寿命有多长?

答:具体的使用寿命要看具体的使用方法,对Flash而言,基本上可以做到单个扇区10万次的擦写次数。应用中建议考虑到损耗均衡,以提高在一些需要频繁擦写的应用中的使用寿命。

问:NOR闪存的性能优势主要有哪些?

答:NOR Flash主要性能优势有:(1)可靠性高,没有坏块,位翻转的几率低;(2)读速度快能够支持片上执行代码,也就是XIP,一般代码存储,产品的生命周期长的产品,推荐使用NOR闪存。

问:NOR Flash与NAND Flash的不同点有哪些?

答:(1)NOR flash没有坏扇区,而NAND有;(2)引脚,数据通信不一样,NOR有串行并行之分,NAND主要是I/O通信,地址数据复用;(3)应用领域不太一样,NOR主要用于存储程序代码,需要高可靠性的应该,NAND主要保存数据用的。

问:除了SPI,还支持何种通信方式?

答:Flash有分NOR和NAND。NAND Flash主要是用I/O通信,数据地址复用,NOR又分串行并行,串行就只有SPI,但SPI有单I/O或多I/O,还可以支持DDR SPI。并行就有分ADP, ADM, AADM等等。

问:SPI NOR的最主要优点是什么?

答:引脚少,封装小,价格好,兼容性大,速度已经可以跟普通的并行Flash比了。

问:Spansion产品采用的是通用引脚吗?

答:是的。都是满足JEDEC标准的。不管是串行还是并行的NOR Flash而且容量增大引脚依然是兼容的。

问:Spansion闪存产品是否具有写保护功能?

答:是的,Spansion的产品提供非常丰富的写保护,可以是动态的(掉电或者复位之后失去保护,需要使用的时候重新设置),也可以是永久性的,可以按照单个扇区任意大小保护,且无需传统的12V操作。另外,部分产品且支持读保护功能。

GEC

(中电网、《世界电子元器件》)

■ Spansion公司

在嵌入式系统中,NOR闪存一直以来仍然是较受青睐的非易失性内存,NOR器件的低延时特性可以接受代码执行和数据存储在一个单一的产品。虽然NAND记忆体已成为许多高密度应用的首选解决方案,但NOR仍然是低密度解决方案的首选之一。

未来闪存产品具有快速发展的趋势,可以发现,闪存产品从低密度、低性能、低功能的发展特点转变为高密度、高性能、高功能的发展特点。Spansion的NOR闪存广泛运用于汽车电子、医疗设备、通讯设备、机顶盒等。

SPI Flash特性

SPI串行结构的EEPROM最早出现于20世纪80年代中期,由摩托罗拉在其MC68HC系列中首先引入,MicroWire是由国半制定的总线标准,它和SPI非常相似,只是MicroWire的时钟极性CPOL和时钟相位CPHA是固定的,均为0。I2C也是出现在80年代,由Philips制定,它通过一条数据线和一条时钟线实现半双工通信,I2C总线接口实现了最简单的总线接口方式。三种标准如图1所示。

SPI和MicroWire很相近,速度非常快,且在设计中无需上拉电阻,可以支持全双工通信操作,抗干扰能力强,缺点是需要占用较多的数据总线,且需要为设备分配单独的片选信号,没有接收数据的硬板机制。对I2C总线来说,它占用的总线较少,可以多个设备共同用一根总线,支持接收数据的硬板机制,缺点是速度较低,为3.4MHz以下,只支持半双工的操作,设计时需要上拉电阻,且对噪声的干扰相对敏感。

图1 三种总线标准

SPI的接口从传统的单进单出已经提升到双进双出或者四进四出。如图2所示,通过单向输入SI,输出SO变为双向的传输,同时将WP引脚和HOLD引脚复用为双向的IO口来实现多IO口的接口通信,其协议及基本的读写操作和原始EEPROM兼容,同时硬件上实现简单的完全兼容。

相对于传统的并行NOR Flash而言,SPI NOR Flash只需要6个引脚就能够实现单I/O,双I/O和4个I/O口的接口通信,而并行的NOR Flash则至少需要40个引脚。人们普遍使用的是标准NOR Flash异步读模式,而ADM及地址数据信号复用,这种并行NOR Flash引脚数相对较少,通过实现突发读模式,其数据输出最快可超过120MB/s,SPI具有较少的引脚,同时,通过采用DDR的方式读操作,在80MHz的时钟下,其数据输出可以达到80MB/s,甚至超过并行NOR Flash的异步读速度。

图2 SPI的接口转变

在过去的几年中,随着直接CPU 内存映射功能的支持, SPI的读操作取得了极大的进步,而传统的SPI外设控制器仍然在用于传统的SPI的读或别的操作,相比之下,通过CPU的直接读取操作,速度比通过SPI控制器来的更快,延迟低。

SPI双通道控制器示意图如图3所示,双通道可以使SPI的数据输出增加一倍,硬件上将片选和时钟共用的话,只需要10个引脚就能实现SPI Flash所有功能。可以考虑,实现一片SPI Flash 8bits数据的传输,从而提升SPI Flash的数据输出能力。

图3 SPI双通道控制器

关于SPI时序对读速度的影响,如图4所示。tV是指时钟的下降沿到有效数据输出所需要的时间,一般最大为8ns。tHO是数据输出后到下一个时钟下降沿可持续的时间,一般最小值0ns。这两个参数和时钟频率一起决定了SPI Flash的最大数据输出速度。事实上,tHO在实际应用中并不能像时钟周期一样可以无限压缩,而往往都会大于0ns。

早期的4个I/O口输出协议需要对地址和数据分别串行传送。如,8个命令周期加上24个地址周期至少需要32个时钟周期完成一个读操作命令周期,如果Flash的寻址超过128Mbits,仅地址周期就需要32个时钟周期,非常耗时。

图4 SPI时序对读速度的影响

新的4个I/O口输出模式,其地址可以通过4个I/O口同时传送,如,24位地址信号仅需要6个时钟周期就可以完成,加上8个命令周期共需要14个周期完成命令,其速度比早期的4个I/O口的传输要快很多。

模式bit的应用用于通知SPI Flash下一个命令和前一个命令是同样的命令。使我们在需要重复进行读操作的时候,可以减少命令周期带来的总线开销,从而进一步提高SPI Flash的读取性能。

DDR的4 I/O口读模式由一个8bits的命令开始,而输入地址和输出的数据按照DDR的模式进行,这种模式需要协议的开销,需要8个命令时钟周期,加上3个地址时钟周期,一共11个时钟周期可以完成一个读命令操作。

通过模式bit消除可以节省重复输入相同命令时的时钟周期,完成一个DDR口的读操作仅需要3个时钟周期。

数据总线上的数据会由于时钟频率太高而出现歪斜或失真,导致数据的读错误,而DLP(data learning pattern)的功能在DDR多I/O口协议中的使用可以使Flash在时钟频率高时同样稳定地工作。DLP的功能是通过利用真实数据输出前的假数据周期,它不会影响整个命令的时钟周期,DLP的数据采用可以使主机端明确什么时候可以采用到正确的目标数据,从而提高系统在高频率SPI数据在读操作时的可靠性及稳定性。

4 I/O口的DDR读模式增加了DLP和模式bit消除模式后,只需要3个时钟周期的协议开销,目前的器件在80MHz频率下,数据输出可以达到80MB/s。

从设计的角度来说,如图5所示。芯片内部的引脚连接点的放置同样会影响到SPI Flash的数据输出速度,时钟和I/O口信号的紧凑设计会减少芯片的数据失真,从而提高SPI Flash芯片的工作速度。

图5 芯片内部的引脚连接点设计

SPI Flash未来发展

未来SPI Flash的发展需要一种简单、高效和高速接口。随着传统的应用越来越多地转向SPI Flash的存储接口,人们希望传统的一些并行NOR Flash的功能也能出现在SPI Flash中,比如Reset复位功能、宽电压功能,及以扇区为单位的写保护等功能。同时随着DDR接口被越来越多广泛地运用,低电压总线操作的支持等,数据SPI Flash将会提供更高的读性能。

低成本存储器解决方案

Spansion的FL-S是65nm工艺的产品,它具有增强的性能和丰富的功能。从产品性能上说,擦除速度快5倍以上,写速度快3倍以上,同时,最快速读功能快20%以上。从产品功能上说,容量覆盖了主流的128 Mbits~1Gbits,其封装是工业标准封装,并能实现老产品到下一代新产品的兼容。产品在安全性方面也有很大的提高,除了支持OTP以外,部分型号支持读保护功能。

目前,人们普遍使用的并行NOR Flash,如图6所示,通过异步读取的方式操作Flash,理想的时序设计基本上输出速度是达到61MB/s。而Spansion的SPI Flash页读取模式可以达到98MB/s,和传统的异步读模式不同,第一个读取周期地址时序和异步读相同,但后续的读取速度可以递增25ns,从而大大提高Flash的读取速度。总的来说,DDR的读取模式可以在极少的引脚基础上可以实现超过传统的读取速度,未来会被越来越多地被采用。

图6 Page-mode NOR读取速度优势

Spansion的FL-S性能较高,对于SPI Flash来说,成本的节省来源于三个主要方面,第一,主芯片成本降低,从传统的40个引脚或以上并行NOR Flash的支持到仅需要6个引脚的SPI Flash支持,成本会大大降低,但是如果主芯片各种芯片接口都支持的话,成本也不会明显降低。第二,SPI Flash自身的封装生产成本降低,同时从生产的成本来说,SPI由于引脚的减少会降低成本,测试成本也会降低。第三,Flash的速度提升对于客户体验会有很大的改善,会给最终客户端产品带来竞争力,如开机时间、运行速度等等。

随着竞争的国际化和知识产权保护意识的提高,工程师们对Flash芯片及芯片存储的代码安全性要求越来越高。Spansion的新系列Flash提供了非常丰富的保护功能。首先,普通的Flash可以支持扇区的写保护功能,这种保护可以是动态的也可以是永久性的,动态的就是指Flash的保护设置在掉电的时候或者复位时保护功能失效,在上电或者复位后重新需要设置。而永久性的则不会因为掉电或者复位而使保护的状态失效。大部分的Flash还提供了OTP的一次性的写入功能。部分产品特别是针对高安全性的机顶盒产品可以支持将Flash扇区的操作OTP的功能,以扇区为单位,通过设置OTP可以防止任何的写操作命令从而实现Flash存储内容的保护。另外,Spansion的65nm产品部分型号还可以实现读加密的要求,客户可以通过设置读保护密码防止Flash的内容被读取,从而保护产品的软件不会被轻易地抄袭。

在线座谈(Online Seminar)是中电网于2000年推出的创新服务,通过“视频演示+专家解说+在线问答”三位一体相结合的形式,充分发挥网络平台的便捷性,实现了先进半导体技术提供商与系统设计工程师的实时互动交流,其形式和内容都广受电子行业工程师的好评。本刊每期将挑选一些精华内容整理成文,以飨读者。欲了解更多、更详细的内容,敬请登录http://seminar.eccn.com。

问答选编

问:存储器接口可以和现在的CPUSPI接口完全兼容吗?

答:可以的,CPI所带的SPI接口可以专门用来连接SPI接口的Flash。

问:是否可以实现多I/O口技术?

答:以SPI为例, 目前有x1/x2/x4三种I/O方式,并行NOR Flash和NAND Flash 有x8/x16两种I/O方式。

问:可不可以用串行NOR Flash做程序存储器,和并行NOR Flash相比,应该注意些什么?

答:当然可以,串行Flash和传统的并行NOR Flash相比,只是接口不同(当然这种接口的不同需要控制端芯片的支持),其可靠性和稳定性和并行NOR Flash相同。存储代码的应用中,需要注意硬件上可能因为时钟频率高带来的单板干扰,软件设计中可以采用一些写保护功能体改代码存储的安全性,另外Spansion的新系列串行Flash产品还支持了硬件复位RESET功能,在一些特殊的应用中可以考虑采用。

问:产品现在应用情况如何,容量怎么样?

答:现在已经有很多的机顶盒客户,网通客户,工业类客户在使用,最新FL-S flash是业界速度(读写擦除)较快的,容量从128Mbits~512Mbits都已经量产,当然Spansion公司有全系列的嵌入式的Flash提供给客户,串型的容量从4Mbits~512Mbits,并行的容量从8Mbits~2Gbits。

问:安全性怎么样啊?

答:串行的Flash和传统的并行NOR Flash相类似,只是接口不一样。另外,65nm技术的产品Spansion公司去年上半年已经量产,工艺本身非常成熟。从应用的角度来说,如果需要进一步提高其安全性,可以采用Spansion非常丰富的各种写保护方式来保护代码,同时部分产品且支持密码加密的读保护方式,提高产品的安全性。

问:Spansion的SPI闪存目前的存取速度可到多快?

答:单I/O是fast read是133Mhz,多I/O每个是80Mhz。如果是四I/O那就是320Mhz。如果能支持DDR SPI,double data rate,最快是66MB/s。

问:产品的性价比如何?

答:由于市场竞争的关系,目前各家厂商的Flash价格相差不大,但是Spansion NOR Flash容量组合全,与其他家的产品相比,读写擦性能更高,尤其是目前的65nm系列产品FL-S和GL-S。

问:产品的寿命有多长?

答:具体的使用寿命要看具体的使用方法,对Flash而言,基本上可以做到单个扇区10万次的擦写次数。应用中建议考虑到损耗均衡,以提高在一些需要频繁擦写的应用中的使用寿命。

问:NOR闪存的性能优势主要有哪些?

答:NOR Flash主要性能优势有:(1)可靠性高,没有坏块,位翻转的几率低;(2)读速度快能够支持片上执行代码,也就是XIP,一般代码存储,产品的生命周期长的产品,推荐使用NOR闪存。

问:NOR Flash与NAND Flash的不同点有哪些?

答:(1)NOR flash没有坏扇区,而NAND有;(2)引脚,数据通信不一样,NOR有串行并行之分,NAND主要是I/O通信,地址数据复用;(3)应用领域不太一样,NOR主要用于存储程序代码,需要高可靠性的应该,NAND主要保存数据用的。

问:除了SPI,还支持何种通信方式?

答:Flash有分NOR和NAND。NAND Flash主要是用I/O通信,数据地址复用,NOR又分串行并行,串行就只有SPI,但SPI有单I/O或多I/O,还可以支持DDR SPI。并行就有分ADP, ADM, AADM等等。

问:SPI NOR的最主要优点是什么?

答:引脚少,封装小,价格好,兼容性大,速度已经可以跟普通的并行Flash比了。

问:Spansion产品采用的是通用引脚吗?

答:是的。都是满足JEDEC标准的。不管是串行还是并行的NOR Flash而且容量增大引脚依然是兼容的。

问:Spansion闪存产品是否具有写保护功能?

答:是的,Spansion的产品提供非常丰富的写保护,可以是动态的(掉电或者复位之后失去保护,需要使用的时候重新设置),也可以是永久性的,可以按照单个扇区任意大小保护,且无需传统的12V操作。另外,部分产品且支持读保护功能。

GEC

(中电网、《世界电子元器件》)

嵌入式 汽车电子 机顶盒 总线 电阻 电压 半导体 电子 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)