基于FPGA的快速9/7整形离散小波变换系统

时间:11-09

来源:互联网

点击:

美国空间数据系统咨询委员会(简称CCSDS)于2005年推出一套适用于空间领域的图像压缩标准,标准使用了离散小波变换为核心算法,推荐使用9/7整数离散小波变换实现无损图像压缩,由于该算法结构简单,易于硬件设计实现,因此可以用FPGA来实现提升小波算法。

1 CCSDS图像压缩标准中的小波变换

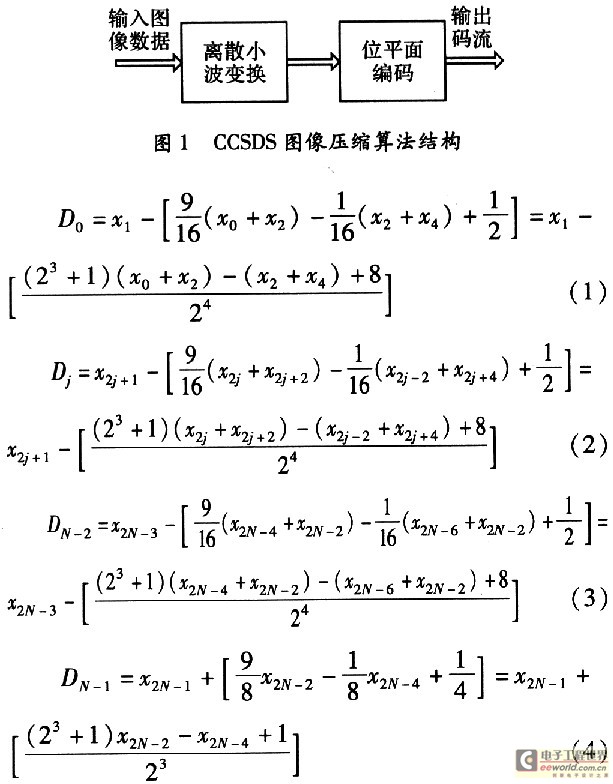

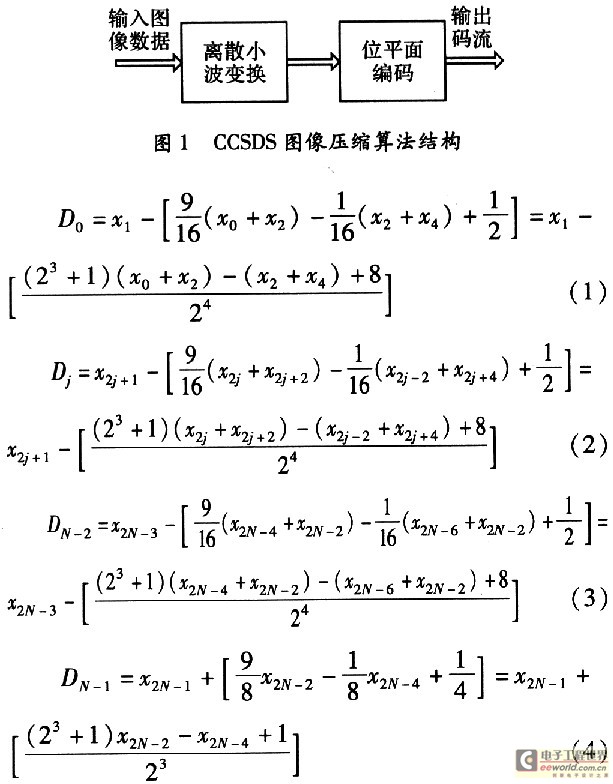

CCSDS图像压缩算法主要包括两个功能模块:前一部分是对遥感图像数据进行离散小波变换,去除图像数据之间的冗余;后一部分是对去相关后的图像数据进行位平面压缩编码,如图1所示。

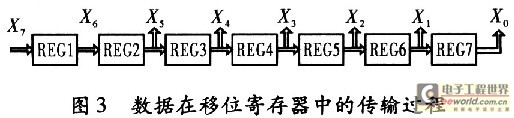

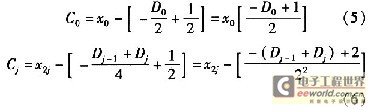

CCSDS标准推荐使用9/7离散小波滤波器对图像数据进行变换,即滤波器的低通系数为9个,滤波器的高通系数为7个。对于长度为2N待变换图像的原始数据Xk(k=0,1,2,…,2N-1),其整形小波变换公式如式(1)~式(6)所示。

其中,[]为对数据进行下取整操作;Cj为低通小波系数输出;Dj为高通小波系数输出。为了避免乘法器运算的繁琐,对公式进行了变形,采用加法器和移位操作实现公式的运算,提高了运算速度。

2 9/7二维离散小波变换的系统设计过程

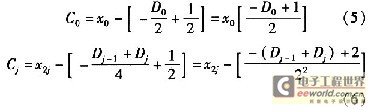

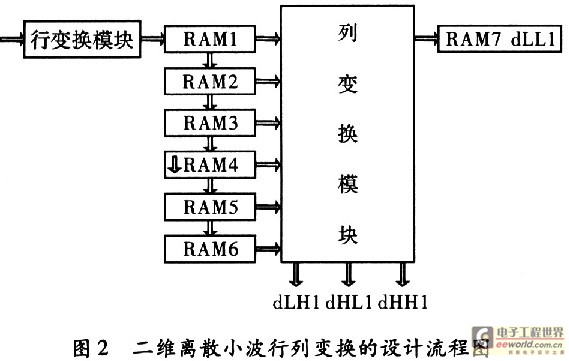

本文在Xilinx公司提供的ISE7.1集成设计软件环境下,采用VHDL语言设计实现9/7二维离散小波变换系统,首先进行小波行变换,行变换后的数据按照行数输入内部RAM缓存,然后对行变换后的数据再进行列变换,最后将低频系数dLLl输入RAM缓存,其余高频系数dLHl,dHLl,dHHl输出到外挂RAM中缓存,系统设计流程,如图2所示。

2.1 行变换过程

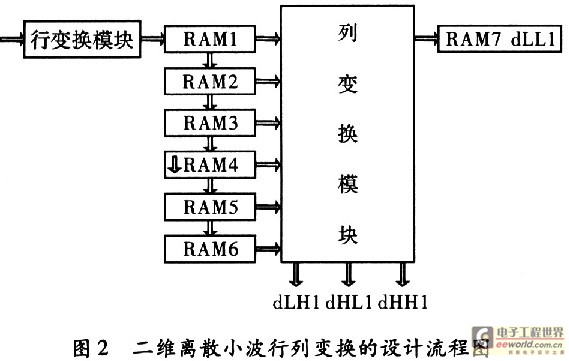

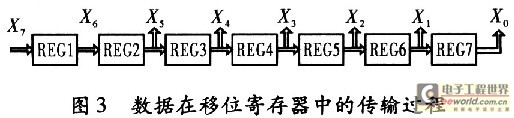

首先,使用7个移位寄存器来实现对数据的读写传输,每到来一个时钟控制信号(clk),就往移位寄存器中读写一个数据,数据在移位寄存器中的传输过程,如图3所示。

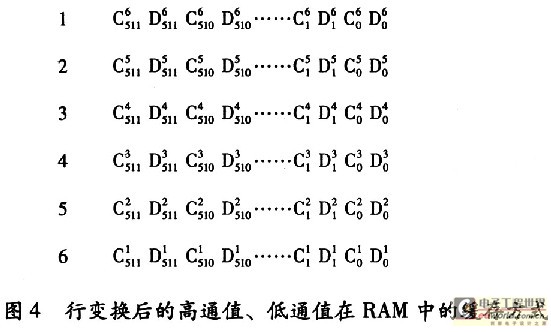

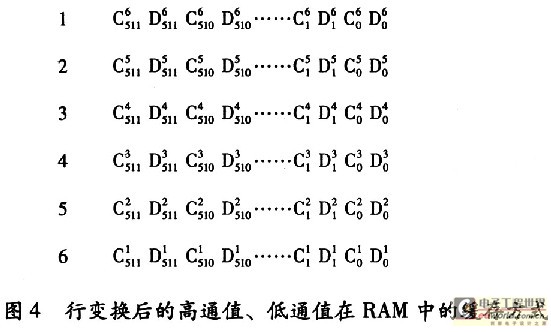

当输入第5个数据时,就可以根据式(1)和式(5)分别计算出第一个高通系数值D0和第一个低通系数值C0,下一个时钟控制信号读入第6个数据时,不进行操作,当控制读入第7个数据时,根据式(2)和式(6)分别计算出第2个高通系数值Dj和第2个低通系数值Cj,小波行变换后的高通系数D和低通系数C采用地址传输的方式交叉存储到6个内部RAM当中,如图4所示。

2.2 列变换过程

由于列变换是针对行变换后的数据进行的,即对上面6片RAM中存储的行变换后的数据进行列变换,为了提高运行速度,本文采用基于行的列变换方法,即当小波变换进行到第5行时,列变换也同时进行,第5行行变换结束时,也完成了针对第5行数据的列变换,当第6行进行小波变换时,不进行列变换操作,直到第7行小波行变化数据输入时,再同时进行列变换计算操作,依次完成小波列变换。对于列小波变换后的低频数据dLLl,要输入RAM缓存以进行下一级变换,对于其他的高频数据(dLHl,dHLl,dHHl)可以直接输出到片外存储器中。

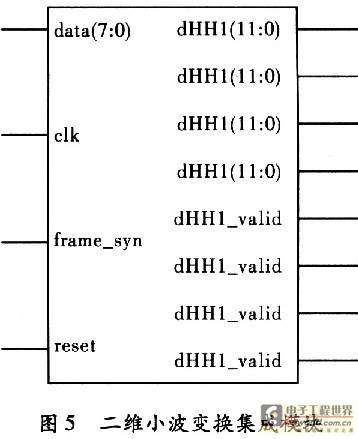

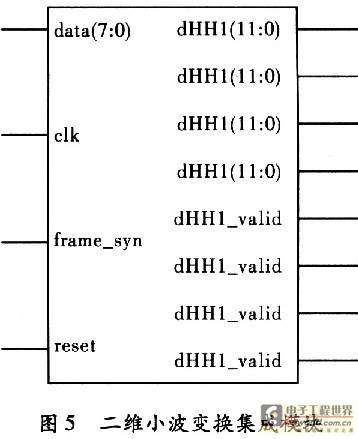

下面是设计的一级二维小波变换的集成模块,如图5所示。

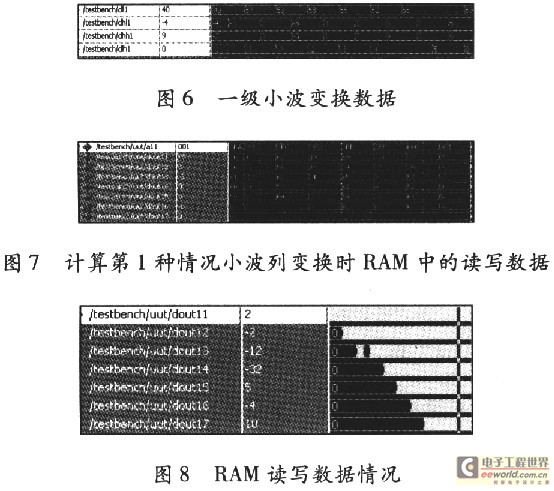

3 仿真与综合

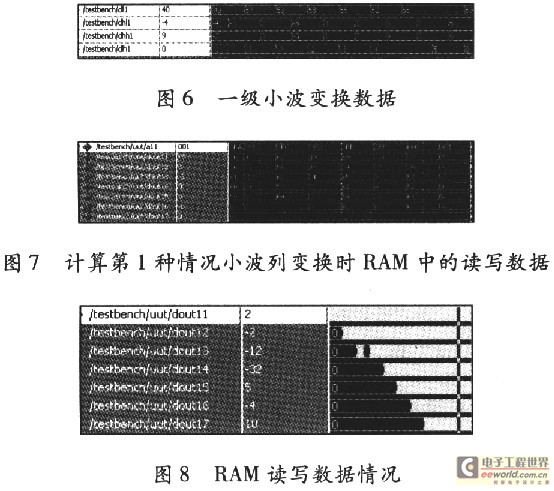

为了验证本文设计系统的性能,使用Modlesim6.3仿真软件对系统进行了仿真测试,下面是采用大小为1 024×1 024,图像数据为8位的测试图像进行测试仿真的部分波形图。

在Xilinx提供的ISE7.1仿真软件下搭建测试平台,对设计系统进行综合,结果如图9所示。

设计系统时钟频率可达到54 MHz,满足对图像数据的实时处理要求。

4 结束语

本文主要讨论了基于FPGA的快速9/7整形离散小波变换系统设计,该结构采用内部RAM的循环覆盖的存储方式,使对存储器的需求量减小,从而减小了硬件功耗,同时采用基于行的列变换方式,提高了的系统运行,可实现对遥感传输图像的快速实时处理。

1 CCSDS图像压缩标准中的小波变换

CCSDS图像压缩算法主要包括两个功能模块:前一部分是对遥感图像数据进行离散小波变换,去除图像数据之间的冗余;后一部分是对去相关后的图像数据进行位平面压缩编码,如图1所示。

CCSDS标准推荐使用9/7离散小波滤波器对图像数据进行变换,即滤波器的低通系数为9个,滤波器的高通系数为7个。对于长度为2N待变换图像的原始数据Xk(k=0,1,2,…,2N-1),其整形小波变换公式如式(1)~式(6)所示。

其中,[]为对数据进行下取整操作;Cj为低通小波系数输出;Dj为高通小波系数输出。为了避免乘法器运算的繁琐,对公式进行了变形,采用加法器和移位操作实现公式的运算,提高了运算速度。

2 9/7二维离散小波变换的系统设计过程

本文在Xilinx公司提供的ISE7.1集成设计软件环境下,采用VHDL语言设计实现9/7二维离散小波变换系统,首先进行小波行变换,行变换后的数据按照行数输入内部RAM缓存,然后对行变换后的数据再进行列变换,最后将低频系数dLLl输入RAM缓存,其余高频系数dLHl,dHLl,dHHl输出到外挂RAM中缓存,系统设计流程,如图2所示。

2.1 行变换过程

首先,使用7个移位寄存器来实现对数据的读写传输,每到来一个时钟控制信号(clk),就往移位寄存器中读写一个数据,数据在移位寄存器中的传输过程,如图3所示。

当输入第5个数据时,就可以根据式(1)和式(5)分别计算出第一个高通系数值D0和第一个低通系数值C0,下一个时钟控制信号读入第6个数据时,不进行操作,当控制读入第7个数据时,根据式(2)和式(6)分别计算出第2个高通系数值Dj和第2个低通系数值Cj,小波行变换后的高通系数D和低通系数C采用地址传输的方式交叉存储到6个内部RAM当中,如图4所示。

2.2 列变换过程

由于列变换是针对行变换后的数据进行的,即对上面6片RAM中存储的行变换后的数据进行列变换,为了提高运行速度,本文采用基于行的列变换方法,即当小波变换进行到第5行时,列变换也同时进行,第5行行变换结束时,也完成了针对第5行数据的列变换,当第6行进行小波变换时,不进行列变换操作,直到第7行小波行变化数据输入时,再同时进行列变换计算操作,依次完成小波列变换。对于列小波变换后的低频数据dLLl,要输入RAM缓存以进行下一级变换,对于其他的高频数据(dLHl,dHLl,dHHl)可以直接输出到片外存储器中。

下面是设计的一级二维小波变换的集成模块,如图5所示。

3 仿真与综合

为了验证本文设计系统的性能,使用Modlesim6.3仿真软件对系统进行了仿真测试,下面是采用大小为1 024×1 024,图像数据为8位的测试图像进行测试仿真的部分波形图。

在Xilinx提供的ISE7.1仿真软件下搭建测试平台,对设计系统进行综合,结果如图9所示。

设计系统时钟频率可达到54 MHz,满足对图像数据的实时处理要求。

4 结束语

本文主要讨论了基于FPGA的快速9/7整形离散小波变换系统设计,该结构采用内部RAM的循环覆盖的存储方式,使对存储器的需求量减小,从而减小了硬件功耗,同时采用基于行的列变换方式,提高了的系统运行,可实现对遥感传输图像的快速实时处理。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)