一种基于FPGA的RFID无线通信系统的实现

时间:11-09

来源:互联网

点击:

1.3.2 SPI硬件设计

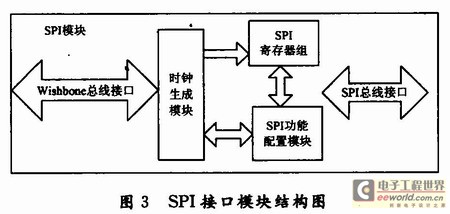

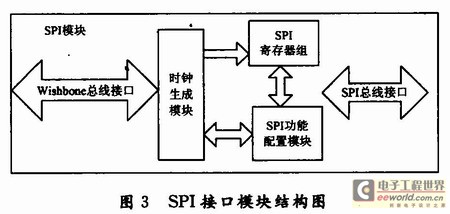

图3是本文无线通信系统中SPI模块的结构图,该系统中的SPI主要由时钟生成模块,SPI寄存器组,SPI功能配置的模块组成,并且通过Wishbone总线与控制器相连,具体设计如下:

时钟生成模块:由于SPI模块是基于FPGA来实现的,而FPGA外部提供的时钟较快(50 MHz或100 MHz),不适合与NRF905的SPI接口进行通信(1 Hz~10 MHz),所以需要分频来使时钟慢下来。但是至于几分频是由SPI功能配置模块来完成的。其次由于SPI协议指出数据可在上升沿或下降沿触发,所以还需要对时钟的上升沿或下降沿进行鉴别(也称抓沿程序),这个功能也由这个模块完成。

SPI寄存器模块:这个模块实现的是一个由16个8位寄存器组成的128位的寄存器组,也就是说通过SPI接口一次性可收发8~128位的串行数据。具体操作由SPI功能配置模块来完成。

SPI功能配置模块:这个模块相当于一个SPI控制器,通过对其寄存器的配置来决定时钟的分频数,收发数据位数,时钟上升沿或下降沿传输数据等,而对这些寄存器的配置是由控制模块完成的。下面就配置寄存器做一些简要说明。

首先介绍控制寄存器:

1.4 控制模块

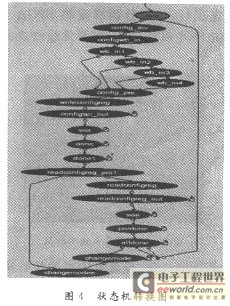

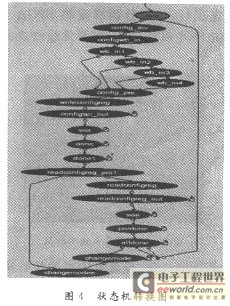

对于控制模块来说,其实现方法是利用基于Verilog语言的有限状态机来实现,相当于一条一条的指令来控制SPI模块接收发送数据。控制模块分成三个独立的部分即接收控制模块、发送控制模块及NRF905配置模块。其中接收与发送控制模块分别包含对SPI进行配置的状态。下面对接收控制模块的设计进行说明。图4即为Debussy综合出的状态机转换图。

为了完成无线通讯而设计的状态较多,比较复杂,故只对比较重要的状态做些简要说明。idle空闲状态,完成对端口进行初始化寄存器清零;config_div状态,对时钟进行分频(定义sclk);configwb_in状态,定义传输数据的位数以及是上升沿收发还是下降沿收发,wb_inl,wb_in2,wb_in3,wb_in4,这四个状态就是通过Wishbone总线接口对SPI配置要写的数(每一个状态对应一个寄存器);configspi_out状态,开始传送数据;done状态,片选置高数据传送完成;readeonfigreg_prel状态,设定发送数据位数;readconfigreg(读寄存器控制字位数)状态,通过Wishbone总线接口对SPI配置读命令字;readconfigreg_out状态,设定发送/接收数据位;alldone状态,片选置高完成配置数据读取的过程。

该设计考虑到验证配置过程的正确性,故特意设定了读寄存器配置数据的状态,ehangemode就是接收状态,当接收完成后(DR=1)进入eh-angmodee状态,把收到的数据读出来。然后再回到readeonfigreg_prel状态,等待新的传输数据。

2 系统验证

该设计最后进行了板级验证,FPGA开发板与NRF905的PCB板构成这个验证系统。FPGA芯片的采用Xilinx公司的XC2V1000,所用的综合工具是Synplify,前仿真与后仿真用来查看波形的工具是Modelsim,所用到的布局布线工具与下载工具是ISE10.1集成的iMPACT,而板级测试用来查看波形的工具是Chipseope。

在下载之前对本设计进行了充足的功能仿真,用Verilog编写了SPI从机模仿NRF905的SPI接口与SPI主机进行通信,确保能够完成预先设定的功能。

下载是将配置文件下载到具体的FPGA芯片中。本文系统中采用的是JTAG下载方式,下载工具使用Xilinx ISE的集成工具iMPACT。在下载之前进行了管脚绑定其目的就在于能够将设计的输入/输出端口约束在FPGA芯片的合适的引脚上,以方便对其进行分析和调试并与外界I/O进行相连。下面即为本设计中相应的管脚约束文件中的相关内容。

下载完成后,依照管脚绑定将FPGA开发板与NRF905的PCB相连,图5即为无线收发的PCB连接图。

这只是其中一端,在这里假定为接收端,那么另外还有一样的互连PCB板作为发送端。右边的PCB板为FPGA用来实现SPI模块与控制模块。左上倒凸字形的小PCB板即为NRF905,左边的PCB板起到了连接FPGA与NRF905的左右,并给NRF905提供电源。

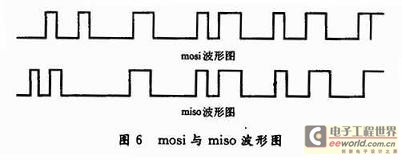

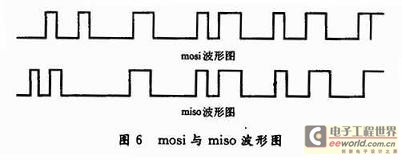

系统建立起来后,下一步是最终的板级验证。图6为用Chipscope得到的波形图。mosi与miso分别是发送端与接收端SPI总线上的信号。从图中可以看出数据基本吻合,由此表明设计的以FPGA控制NRF905的无线通信系统能够正常工作。

图3是本文无线通信系统中SPI模块的结构图,该系统中的SPI主要由时钟生成模块,SPI寄存器组,SPI功能配置的模块组成,并且通过Wishbone总线与控制器相连,具体设计如下:

时钟生成模块:由于SPI模块是基于FPGA来实现的,而FPGA外部提供的时钟较快(50 MHz或100 MHz),不适合与NRF905的SPI接口进行通信(1 Hz~10 MHz),所以需要分频来使时钟慢下来。但是至于几分频是由SPI功能配置模块来完成的。其次由于SPI协议指出数据可在上升沿或下降沿触发,所以还需要对时钟的上升沿或下降沿进行鉴别(也称抓沿程序),这个功能也由这个模块完成。

SPI寄存器模块:这个模块实现的是一个由16个8位寄存器组成的128位的寄存器组,也就是说通过SPI接口一次性可收发8~128位的串行数据。具体操作由SPI功能配置模块来完成。

SPI功能配置模块:这个模块相当于一个SPI控制器,通过对其寄存器的配置来决定时钟的分频数,收发数据位数,时钟上升沿或下降沿传输数据等,而对这些寄存器的配置是由控制模块完成的。下面就配置寄存器做一些简要说明。

首先介绍控制寄存器:

- 控制寄存器第O位go:是否开始发送。

- 控制寄存器第1位rx_negedge:接收数据是下降沿还是上升沿。

- 控制寄存器第2位tx_negedge:发送数据是下降沿还是上升沿。

- 控制寄存器第3~9位char_len:发送数据的位数(因为SPI是全双工的,所以这实际上也是接收数据的位数)。

- 控制寄存器第10位lsb:是从高位发送还是地位发送。

- 控制寄存器第11位ie:读写完成之后是否发送中断信号。

- 控制寄存器第12位ass:是否自动产生片选信号。

- 分频寄存器:spi_divider_sel。

- 状态寄存器:spi_ctrl_sel。

- 数据寄存器O:spi_tx_sel[0]。

- 数据寄存器1:spi_tx_sel。

- 数据寄存器2:spi_tx_sel。

- 数据寄存器3:spi_tx_sel。

- 片选信号寄存器:spi_ss_sel。

1.4 控制模块

对于控制模块来说,其实现方法是利用基于Verilog语言的有限状态机来实现,相当于一条一条的指令来控制SPI模块接收发送数据。控制模块分成三个独立的部分即接收控制模块、发送控制模块及NRF905配置模块。其中接收与发送控制模块分别包含对SPI进行配置的状态。下面对接收控制模块的设计进行说明。图4即为Debussy综合出的状态机转换图。

为了完成无线通讯而设计的状态较多,比较复杂,故只对比较重要的状态做些简要说明。idle空闲状态,完成对端口进行初始化寄存器清零;config_div状态,对时钟进行分频(定义sclk);configwb_in状态,定义传输数据的位数以及是上升沿收发还是下降沿收发,wb_inl,wb_in2,wb_in3,wb_in4,这四个状态就是通过Wishbone总线接口对SPI配置要写的数(每一个状态对应一个寄存器);configspi_out状态,开始传送数据;done状态,片选置高数据传送完成;readeonfigreg_prel状态,设定发送数据位数;readconfigreg(读寄存器控制字位数)状态,通过Wishbone总线接口对SPI配置读命令字;readconfigreg_out状态,设定发送/接收数据位;alldone状态,片选置高完成配置数据读取的过程。

该设计考虑到验证配置过程的正确性,故特意设定了读寄存器配置数据的状态,ehangemode就是接收状态,当接收完成后(DR=1)进入eh-angmodee状态,把收到的数据读出来。然后再回到readeonfigreg_prel状态,等待新的传输数据。

2 系统验证

该设计最后进行了板级验证,FPGA开发板与NRF905的PCB板构成这个验证系统。FPGA芯片的采用Xilinx公司的XC2V1000,所用的综合工具是Synplify,前仿真与后仿真用来查看波形的工具是Modelsim,所用到的布局布线工具与下载工具是ISE10.1集成的iMPACT,而板级测试用来查看波形的工具是Chipseope。

在下载之前对本设计进行了充足的功能仿真,用Verilog编写了SPI从机模仿NRF905的SPI接口与SPI主机进行通信,确保能够完成预先设定的功能。

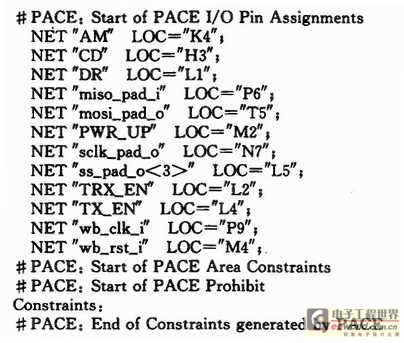

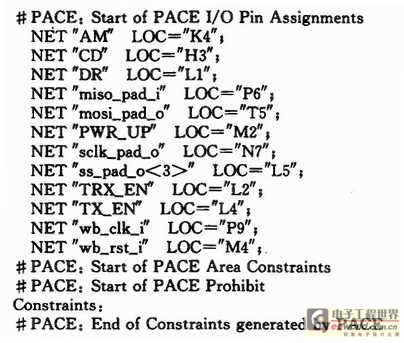

下载是将配置文件下载到具体的FPGA芯片中。本文系统中采用的是JTAG下载方式,下载工具使用Xilinx ISE的集成工具iMPACT。在下载之前进行了管脚绑定其目的就在于能够将设计的输入/输出端口约束在FPGA芯片的合适的引脚上,以方便对其进行分析和调试并与外界I/O进行相连。下面即为本设计中相应的管脚约束文件中的相关内容。

下载完成后,依照管脚绑定将FPGA开发板与NRF905的PCB相连,图5即为无线收发的PCB连接图。

这只是其中一端,在这里假定为接收端,那么另外还有一样的互连PCB板作为发送端。右边的PCB板为FPGA用来实现SPI模块与控制模块。左上倒凸字形的小PCB板即为NRF905,左边的PCB板起到了连接FPGA与NRF905的左右,并给NRF905提供电源。

系统建立起来后,下一步是最终的板级验证。图6为用Chipscope得到的波形图。mosi与miso分别是发送端与接收端SPI总线上的信号。从图中可以看出数据基本吻合,由此表明设计的以FPGA控制NRF905的无线通信系统能够正常工作。

电子 RFID FPGA 射频 无线电 自动化 总线 电压 电流 收发器 Verilog PCB Xilinx 仿真 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)