理解FPGA中的压稳态及计算压稳态的方法

时间:11-09

来源:互联网

点击:

计算亚稳态MTBF

亚稳态平均故障间隔时间MTBF 大致估算了亚稳态导致出现两次设计失败之间的平均时间。较大的MTBF( 例如亚稳态失败间隔数百甚至数千年) 表明非常可靠的设计。所需要的MTBF 取决于系统应用。例如,急救医疗设备需要的MTBF 要比消费类视频显示设备长得多。增大亚稳态MTBF 能够减小信号传输导致设备出现亚稳态问题的概率。

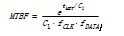

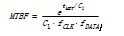

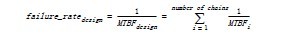

可以使用设计信息以及器件特征参数来计算设计中某些信号传输或者所有信息传输的亚稳态MTBF。采用下面的公式和参数来计算同步器链的MTBF:

C1 和C2 常数取决于器件工艺和工作条件。

在fCLK 和fDATA 参数取决于设计规范: fCLK 是接收异步信号时钟域的时钟频率, fDATA 是异步输入数据信号的触发频率。较快的时钟频率以及触发数据能够降低( 或者劣化) MTBF。

tMET 参数是亚稳态信号达到确切状态的亚稳态建立时间,即,超出寄存器tCO 的时序余量。同步链的 tMET 是链上每一寄存器输出时序余量之和。

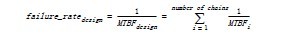

设计中每一同步器链的MTBF 确定了总的设计MTBF。同步器的失效率是1/MTBF,将每一同步器链的失败概率相加得到整个设计的失败概率,如下所示:

设计亚稳态MTBF 为1/failure_ratedesign。

设计人员使用Altera? FPGA 时,不需要手动完成这些计算,这是因为Altera Quartus? II 软件将亚稳态参数集成到了工具中。

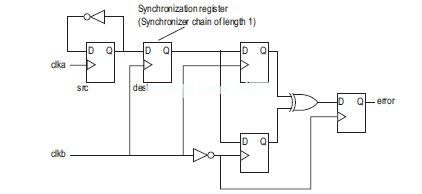

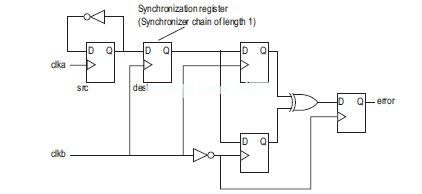

确定亚稳态常数

FPGA供应商可以通过FPGA的亚稳态特性来确定MTBF方程中的常数。确定特性的难点在于典型FPGA设计的MTBF 一般在几年以上,因此,使用真实设计,在实际工作条件下测量亚稳态事件之间的时间间隔是不可行的。为确定器件亚稳态常数, Altera 使用了测试电路,设计的这一电路具有较短的可测量MTBF,如图4 所示。

图 4. 亚稳态特性参数测试电路结构

在这一设计中, clka 和clkb 是两路不相关的时钟信号。同步器输入数据在每一时钟周期进行触发( 较大的fDATA)。同步器长度为1,这是因为一个同步寄存器连接了两个目的寄存器。目的寄存器在一个时钟周期后以及一个半时钟周期后采集同步器输出。如果信号在下一时钟沿到达之前进入亚稳态,电路探测到采样信号出现了不同,输出一个错误信号。这一电路能够探测到半时钟周期内出现的大部分亚稳态事件。

在器件中很多地方复制了这一电路,以减小本地差异的影响,对每一例化模块进行连续测试,以消除耦合噪声。Altera 对每一测试结构测量一分钟,记录错误数。以不同的时钟频率进行测试,在对数坐标上画出MTBF 与tMET 的关系。常数C2 对应于试验结果趋势线的斜率,以常数C1 线性标出曲线。

提高亚稳态MTBF

由于MTBF 方程中的指数因子, tMET/C2 项对MTBF 计算的影响最大。因此,可以通过优化器件常数C2,改进体系结构来提高亚稳态性能,或者优化设计,增大同步寄存器的tMET。

改进FPGA 体系结构MTBF 方程中的亚稳态时间常数C2 取决于器件制造工艺技术相关的各种因素,包括晶体管速率和供电电压等。采用较快的工艺技术和速度更快的晶体管,亚稳态信号能够很快达到稳定。FPGA 从180-nm 工艺尺寸发展到90 nm,晶体管在提高速度的同时也增大了亚稳态MTBF。因此,亚稳态并不是FPGA 设计人员主要考虑的问题。

然而,随着工艺尺寸的减小,供电电压随之降低,电路阈值电压并没有成比例下降。当寄存器进入亚稳态时,其电压大约是供电电压的一半。供电电压降低后,亚稳态电压电平接近电路中的阈值电压。当这些电压比较接近时,电路增益降低了,寄存器需要较长的时间才能脱离亚稳态。FPGA 进入65-nm 以及更小的工艺尺寸之后,供电电压降到0.9V 以下,相对于晶体管速度的提高,应重点考虑阈值电压的影响。因此,除非供应商设计FPGA 电路来提高亚稳态可靠性,否则,亚稳态MTBF 会越来越差。

altera 利用FPGA 体系结构亚稳态分析功能来优化电路,提高亚稳态MTBF。Altera 40-nm Stratix? IV FPGA体系结构以及新器件在设计上进行改进,降低了MTBF 常数C2 ,从而提高了亚稳态的可靠性。

设计优化

MTBF 方程中的指数因子意味着增大设计相关tMET 值能够指数增大同步器MTBF。例如,如果某一器件的常数C2,设置工作条件为50 ps,那么, tMET 只需要增大200 ps,就能够实现指数200/50,提高MTBF e4 倍,即50 多倍,而增大400 ps,提高MTBF e8 倍,即3000 倍。

另一方面,最差MTBF 链对设计MTBF 的影响最大。例如,考虑具有10 个同步链的两个不同设计。一个设计的10 个链有相同的10,000 年MTBF,另一设计的9 个链有一百万年的MTBF,但是一个链的MTBF为100 年。设计失败概率是每一链的失败概率之和,失败概率为1/MTBF。第一个设计的亚稳态失败概率为10 个链× 1/10,000 年 = 0.001,因此,设计MTBF是1000 年。第二个设计的失败概率为9 个链 × 1/1,000,000 +1/100 = 0.01009,设计MTBF 为99 年,略小于最差链的MTBF。

换言之,设计较差的同步链决定了设计的亚稳态总MTBF。由于这一效应,对所有异步信号和时钟域传输进行亚稳态分析非常重要。设计人员或者工具供应商提高最差MTBF 同步链的tMET ,会对设计MTBF 有很大的影响。

为提高亚稳态MTBF,设计人员可以在同步寄存器链上增加额外的寄存器级,以提高tMET 。增加的每一寄存器至寄存器连接时序余量被加到tMET 值中。设计人员一般使用两个寄存器来同步信号,而Altera 建议使用三个寄存器作为标准,以实现更好的亚稳态保护。然而,增加一个寄存器会在同步逻辑中加入额外的延时级,因此,设计人员必须综合考虑这是否可行。

如果设计使用Altera FIFO 宏功能,跨时钟域使用单独的读写时钟,那么,设计人员可以增强亚稳态保护(和延时),实现更好的MTBF。Altera Quartus II MegaWizard? 插件管理器提供增强亚稳态保护选项,包括三个甚至更多的同步级 。

Quartus II 软件还提供业界最好的亚稳态分析和优化功能,以增大同步寄存器链的tMET。确定同步器后,软件将同步寄存器靠近放置,以增加同步链的输出时序余量,然后报告亚稳态MTBF。

亚稳态平均故障间隔时间MTBF 大致估算了亚稳态导致出现两次设计失败之间的平均时间。较大的MTBF( 例如亚稳态失败间隔数百甚至数千年) 表明非常可靠的设计。所需要的MTBF 取决于系统应用。例如,急救医疗设备需要的MTBF 要比消费类视频显示设备长得多。增大亚稳态MTBF 能够减小信号传输导致设备出现亚稳态问题的概率。

可以使用设计信息以及器件特征参数来计算设计中某些信号传输或者所有信息传输的亚稳态MTBF。采用下面的公式和参数来计算同步器链的MTBF:

C1 和C2 常数取决于器件工艺和工作条件。

在fCLK 和fDATA 参数取决于设计规范: fCLK 是接收异步信号时钟域的时钟频率, fDATA 是异步输入数据信号的触发频率。较快的时钟频率以及触发数据能够降低( 或者劣化) MTBF。

tMET 参数是亚稳态信号达到确切状态的亚稳态建立时间,即,超出寄存器tCO 的时序余量。同步链的 tMET 是链上每一寄存器输出时序余量之和。

设计中每一同步器链的MTBF 确定了总的设计MTBF。同步器的失效率是1/MTBF,将每一同步器链的失败概率相加得到整个设计的失败概率,如下所示:

设计亚稳态MTBF 为1/failure_ratedesign。

设计人员使用Altera? FPGA 时,不需要手动完成这些计算,这是因为Altera Quartus? II 软件将亚稳态参数集成到了工具中。

确定亚稳态常数

FPGA供应商可以通过FPGA的亚稳态特性来确定MTBF方程中的常数。确定特性的难点在于典型FPGA设计的MTBF 一般在几年以上,因此,使用真实设计,在实际工作条件下测量亚稳态事件之间的时间间隔是不可行的。为确定器件亚稳态常数, Altera 使用了测试电路,设计的这一电路具有较短的可测量MTBF,如图4 所示。

图 4. 亚稳态特性参数测试电路结构

在这一设计中, clka 和clkb 是两路不相关的时钟信号。同步器输入数据在每一时钟周期进行触发( 较大的fDATA)。同步器长度为1,这是因为一个同步寄存器连接了两个目的寄存器。目的寄存器在一个时钟周期后以及一个半时钟周期后采集同步器输出。如果信号在下一时钟沿到达之前进入亚稳态,电路探测到采样信号出现了不同,输出一个错误信号。这一电路能够探测到半时钟周期内出现的大部分亚稳态事件。

在器件中很多地方复制了这一电路,以减小本地差异的影响,对每一例化模块进行连续测试,以消除耦合噪声。Altera 对每一测试结构测量一分钟,记录错误数。以不同的时钟频率进行测试,在对数坐标上画出MTBF 与tMET 的关系。常数C2 对应于试验结果趋势线的斜率,以常数C1 线性标出曲线。

提高亚稳态MTBF

由于MTBF 方程中的指数因子, tMET/C2 项对MTBF 计算的影响最大。因此,可以通过优化器件常数C2,改进体系结构来提高亚稳态性能,或者优化设计,增大同步寄存器的tMET。

改进FPGA 体系结构MTBF 方程中的亚稳态时间常数C2 取决于器件制造工艺技术相关的各种因素,包括晶体管速率和供电电压等。采用较快的工艺技术和速度更快的晶体管,亚稳态信号能够很快达到稳定。FPGA 从180-nm 工艺尺寸发展到90 nm,晶体管在提高速度的同时也增大了亚稳态MTBF。因此,亚稳态并不是FPGA 设计人员主要考虑的问题。

然而,随着工艺尺寸的减小,供电电压随之降低,电路阈值电压并没有成比例下降。当寄存器进入亚稳态时,其电压大约是供电电压的一半。供电电压降低后,亚稳态电压电平接近电路中的阈值电压。当这些电压比较接近时,电路增益降低了,寄存器需要较长的时间才能脱离亚稳态。FPGA 进入65-nm 以及更小的工艺尺寸之后,供电电压降到0.9V 以下,相对于晶体管速度的提高,应重点考虑阈值电压的影响。因此,除非供应商设计FPGA 电路来提高亚稳态可靠性,否则,亚稳态MTBF 会越来越差。

altera 利用FPGA 体系结构亚稳态分析功能来优化电路,提高亚稳态MTBF。Altera 40-nm Stratix? IV FPGA体系结构以及新器件在设计上进行改进,降低了MTBF 常数C2 ,从而提高了亚稳态的可靠性。

设计优化

MTBF 方程中的指数因子意味着增大设计相关tMET 值能够指数增大同步器MTBF。例如,如果某一器件的常数C2,设置工作条件为50 ps,那么, tMET 只需要增大200 ps,就能够实现指数200/50,提高MTBF e4 倍,即50 多倍,而增大400 ps,提高MTBF e8 倍,即3000 倍。

另一方面,最差MTBF 链对设计MTBF 的影响最大。例如,考虑具有10 个同步链的两个不同设计。一个设计的10 个链有相同的10,000 年MTBF,另一设计的9 个链有一百万年的MTBF,但是一个链的MTBF为100 年。设计失败概率是每一链的失败概率之和,失败概率为1/MTBF。第一个设计的亚稳态失败概率为10 个链× 1/10,000 年 = 0.001,因此,设计MTBF是1000 年。第二个设计的失败概率为9 个链 × 1/1,000,000 +1/100 = 0.01009,设计MTBF 为99 年,略小于最差链的MTBF。

换言之,设计较差的同步链决定了设计的亚稳态总MTBF。由于这一效应,对所有异步信号和时钟域传输进行亚稳态分析非常重要。设计人员或者工具供应商提高最差MTBF 同步链的tMET ,会对设计MTBF 有很大的影响。

为提高亚稳态MTBF,设计人员可以在同步寄存器链上增加额外的寄存器级,以提高tMET 。增加的每一寄存器至寄存器连接时序余量被加到tMET 值中。设计人员一般使用两个寄存器来同步信号,而Altera 建议使用三个寄存器作为标准,以实现更好的亚稳态保护。然而,增加一个寄存器会在同步逻辑中加入额外的延时级,因此,设计人员必须综合考虑这是否可行。

如果设计使用Altera FIFO 宏功能,跨时钟域使用单独的读写时钟,那么,设计人员可以增强亚稳态保护(和延时),实现更好的MTBF。Altera Quartus II MegaWizard? 插件管理器提供增强亚稳态保护选项,包括三个甚至更多的同步级 。

Quartus II 软件还提供业界最好的亚稳态分析和优化功能,以增大同步寄存器链的tMET。确定同步器后,软件将同步寄存器靠近放置,以增加同步链的输出时序余量,然后报告亚稳态MTBF。

FPGA 电路 总线 Altera Quartus 电压 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)