一种基于FPGA的语音密码锁系统的研究与设计

时间:11-09

来源:互联网

点击:

电子密码锁系统主要由电子锁体、电子密匙等部分组成,一把电子密匙里能存放多组开锁密码,用户在使用过程中能够随时修改开锁密码,更新或配制钥匙里开锁密码。一把电子锁可配制多把钥匙。语音方面的广泛应用,使得具有语音播放的电子密码锁使用起来更加方便。语音密码锁的体积小、保密性能好、使用方便,是用在保险箱、电话或是房门上不可少的部分。

本文介绍的基于FPGA的语音密码锁电路具有显示接口,显示时可以是明文也可以是密文星号。由于FPGA具有ISP功能,当用户需要更改时,如增加口令位数和更改口令权限管理时,只需更改FPGA中的控制和接口电路,利用EDA工具将更新后的设计下载到FPGA中即可,无需更改外部电路,这就大大提高了设计效率。而且采用FPGA设计的电子密码锁与单片机控制的电子密码锁相比结构简单、具有更高的系统保密性和可靠性。这种基于FPGA的电子密码锁可以应用在办公室、仓库、宾馆等人员经常变动的场所。

语音密码锁系统的设计

本设计中的语音密码锁具有如下功能:

①电子密码锁部分功能如下:

密码输入:按下一个数字键,就输入一个数值,并在显示器的最右方显示出该数值,并将先前已经输入的数据依次左移一个数字位置,当超出四位时锁定数字键,不响应其输入值。

密码清除:按下此键可清除前面所有的输入值,清除成为“- - - -”。

数字位退格:按下此键可清除最低的数字位,并使各位向右移。

密码设定:按下此键时会将目前的数字设定成新的密码。

激活电锁:按下此键可将密码锁上锁。

解除电锁:按下此键会检查输入的密码是否正确,密码正确即开锁,如果密码错误次数超过三次,系统将进入锁定状态。

万能密码:为了怕使用者忘记密码,系统维护者可考虑设计一个万用密码(8421),不论原先输入的密码是什么,只要输入万用密码即可开锁。

②语音部分功能如下:

录音:能根据所需的内容实现语音录制,为播放准备。

放音:根据系统所处的不同时段以及不同的按键值播放不同的语音提示,以方便使用者操作。

报警:在密码输入错误时,发出报警音。

硬件设计

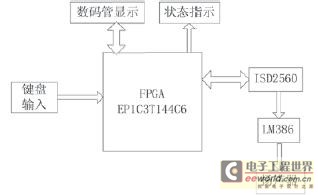

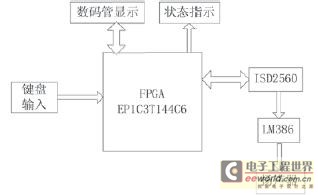

根据整个系统的技术要求,选择硬件电路的设计方案,整个系统原理如图1所示。

根据整个电路的结构可分为几个功能模块:显示模块、电子锁状态指示灯(LED绿:密码正确开锁,LED红:进入死锁状态,LED黄:密码错误)、键盘模块、语音模块等。下面分别对各个功能模块进行详细的介绍。

显示模块

本设计主要是设计一个四位的语音密码锁,因此选择了四位共阴数码管,对输入数字与系统状态进行显示,其接口如图2所示。

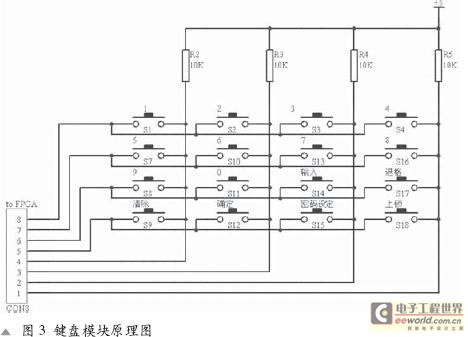

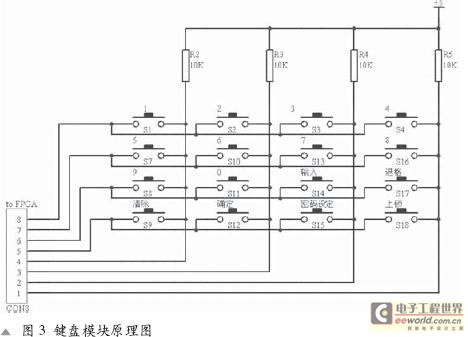

键盘模块如图3所示。以上采用的是4×4矩阵式键盘,可划分为:数字键与功能键。其中,功能键分为:输入、退格、清除、确定、密码设定、上锁。

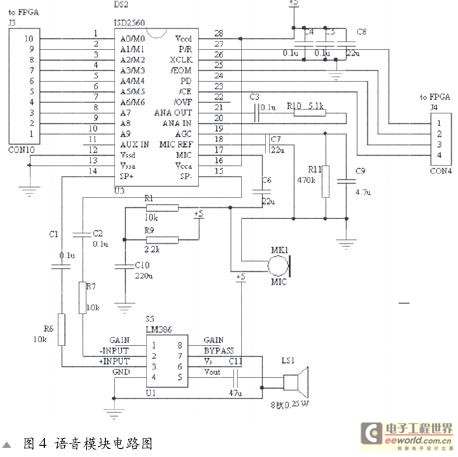

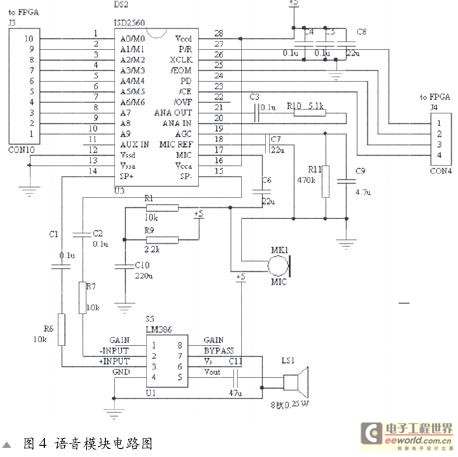

语音模块如图4所示。

根据所需的内容由柱式话筒MIC实现语音录制,同时也可以由ISD2560芯片的11引脚AUX IN 通过计算机的声卡输出端进行语音录制(效果差不多)。在整个系统中由主芯片对ISD2560芯片进行控制,以实现不同时段以及不同按键值播放不同的语音提示。

软件设计

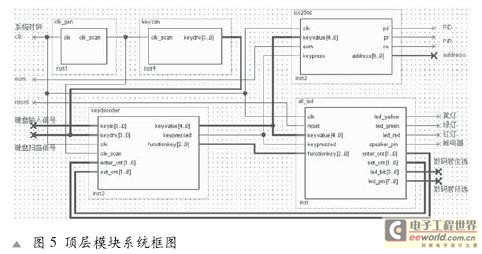

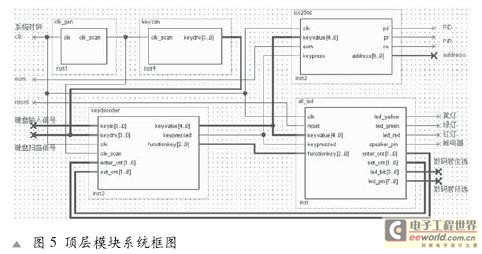

本设计中,采用自顶向下的层次化结构设计方法,把整个系统划分为几个子模块,最后完成顶层电路的设计。子模块可分为:时钟模块、显示子模块、键盘子模块、语音子模块。当各个功能子模块设计完毕,顶层模块的设计就变得简单了,就是将各个子模块连接起来,其电路模型如图5所示。

结语

本设计中采用了ALTERA公司的 EP1C3T144芯片进行设计,实际测试表明系统的各项设计要求均得到满足并且系统工作良好,该设计采用了SOPC技术和FPGA,几乎将整个系统下载于同一芯片中,实现了所谓的片上系统,可以极大减少其它分立元件或其它芯片的使用,有效地缩小了线路板面积,增加了系统的可靠性,大大缩短了系统开发的周期。克服了传统电子密码锁可靠性差、价格高的缺点,提高了系统的性价比。由于采用VHDL语言进行层次化设计,用软件实现硬件电路,具有良好的可移植性,可随时在线更改逻辑设计及有关参数,充分体现现场可编程器件的优越性。

本文介绍的基于FPGA的语音密码锁电路具有显示接口,显示时可以是明文也可以是密文星号。由于FPGA具有ISP功能,当用户需要更改时,如增加口令位数和更改口令权限管理时,只需更改FPGA中的控制和接口电路,利用EDA工具将更新后的设计下载到FPGA中即可,无需更改外部电路,这就大大提高了设计效率。而且采用FPGA设计的电子密码锁与单片机控制的电子密码锁相比结构简单、具有更高的系统保密性和可靠性。这种基于FPGA的电子密码锁可以应用在办公室、仓库、宾馆等人员经常变动的场所。

语音密码锁系统的设计

本设计中的语音密码锁具有如下功能:

①电子密码锁部分功能如下:

密码输入:按下一个数字键,就输入一个数值,并在显示器的最右方显示出该数值,并将先前已经输入的数据依次左移一个数字位置,当超出四位时锁定数字键,不响应其输入值。

密码清除:按下此键可清除前面所有的输入值,清除成为“- - - -”。

数字位退格:按下此键可清除最低的数字位,并使各位向右移。

密码设定:按下此键时会将目前的数字设定成新的密码。

激活电锁:按下此键可将密码锁上锁。

解除电锁:按下此键会检查输入的密码是否正确,密码正确即开锁,如果密码错误次数超过三次,系统将进入锁定状态。

万能密码:为了怕使用者忘记密码,系统维护者可考虑设计一个万用密码(8421),不论原先输入的密码是什么,只要输入万用密码即可开锁。

②语音部分功能如下:

录音:能根据所需的内容实现语音录制,为播放准备。

放音:根据系统所处的不同时段以及不同的按键值播放不同的语音提示,以方便使用者操作。

报警:在密码输入错误时,发出报警音。

硬件设计

根据整个系统的技术要求,选择硬件电路的设计方案,整个系统原理如图1所示。

根据整个电路的结构可分为几个功能模块:显示模块、电子锁状态指示灯(LED绿:密码正确开锁,LED红:进入死锁状态,LED黄:密码错误)、键盘模块、语音模块等。下面分别对各个功能模块进行详细的介绍。

显示模块

本设计主要是设计一个四位的语音密码锁,因此选择了四位共阴数码管,对输入数字与系统状态进行显示,其接口如图2所示。

键盘模块如图3所示。以上采用的是4×4矩阵式键盘,可划分为:数字键与功能键。其中,功能键分为:输入、退格、清除、确定、密码设定、上锁。

语音模块如图4所示。

根据所需的内容由柱式话筒MIC实现语音录制,同时也可以由ISD2560芯片的11引脚AUX IN 通过计算机的声卡输出端进行语音录制(效果差不多)。在整个系统中由主芯片对ISD2560芯片进行控制,以实现不同时段以及不同按键值播放不同的语音提示。

软件设计

本设计中,采用自顶向下的层次化结构设计方法,把整个系统划分为几个子模块,最后完成顶层电路的设计。子模块可分为:时钟模块、显示子模块、键盘子模块、语音子模块。当各个功能子模块设计完毕,顶层模块的设计就变得简单了,就是将各个子模块连接起来,其电路模型如图5所示。

结语

本设计中采用了ALTERA公司的 EP1C3T144芯片进行设计,实际测试表明系统的各项设计要求均得到满足并且系统工作良好,该设计采用了SOPC技术和FPGA,几乎将整个系统下载于同一芯片中,实现了所谓的片上系统,可以极大减少其它分立元件或其它芯片的使用,有效地缩小了线路板面积,增加了系统的可靠性,大大缩短了系统开发的周期。克服了传统电子密码锁可靠性差、价格高的缺点,提高了系统的性价比。由于采用VHDL语言进行层次化设计,用软件实现硬件电路,具有良好的可移植性,可随时在线更改逻辑设计及有关参数,充分体现现场可编程器件的优越性。

电子 FPGA 电路 EDA 单片机 显示器 LED LTE VHDL 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)