对基于FPGA的作战系统时统的研究与设计

时间:11-08

来源:互联网

点击:

作战系统时间的统一同步(时统)的重要性越来越得到重视,只有保证整个系统处在同一时间的基准上,才能实现真正意义上的以网络为中心的信息战、以精确制导武器系统对抗和以协同作战方式为主的现代化战争。另外由于不同的作战系统对时统有着不同要求,因此对时统接收处理模块(简称时统模块)有着较高要求。利用FPGA的强大功能及灵活性设计的时统模块能够很好地实现以上要求。

FPGA为大规模可编程逻辑器件,具有编程方便、集成度高、速度快等特点,可反复编程、擦除、使用,在不改变硬件设计的情况下,可实现不同的功能需求。在FPGA中可完成各种时统功能设计。

1 原理

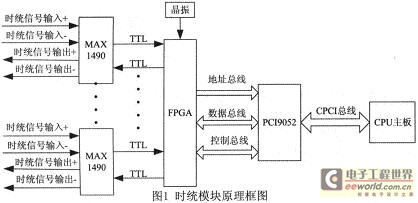

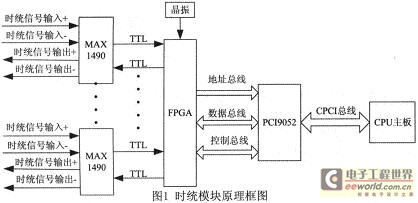

目前时统模块主要应用于Compact PCI(CPCI)系统,因此该时统模块为CPCI总线模块。其主要由总线桥接电路、FPGA、外围接口电路部分组成,如图1所示。接口电路采用MAXl490实现对时统输入信号(授时信号)的接收及转换。将差分信号转换成TTL电平信号提供给FPGA处理,另外将FPGA输出的TTL电平信号转换成差分信号作为时统信号提供给其它设备。

桥接电路采用PCI9052,实现CPCI总线到局部总线的过渡,并将中断信号通过CPCI总线的中断信号线送给CPU主板。CPU主板收到时统模块的中断请求后,做出响应,系统软件根据中断响应输出时间信息。

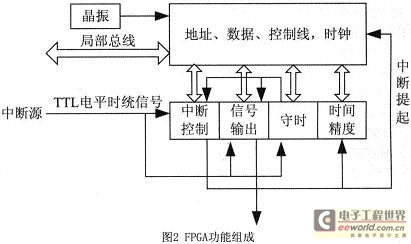

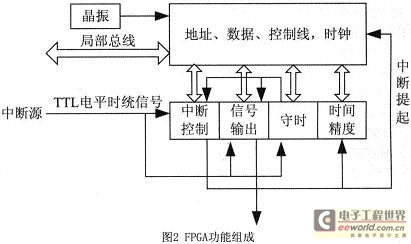

FPGA选用Altera公司MAX70O0S系列中的EPM7256SRl208—10,这是工业界中速度最快的高集成度可编程逻辑器件,具有5000个可用门和1256个宏单元,可满足设计需要。设计中,FPGA实现了对TTL电平时统信号的各种处理,主要包括中断控制、信号输出、守时、时间精度等功能。见图2所示。

下面具体介绍FPGA内部各主要功能的设计。

2 中断控制

中断控制部分主要包括脉冲识别、中断源判断等。为保证时统信号的准确识别,避免丢帧、误判,需要对信号整形,适当展宽。在FPGA中利用反相器对信号整形,利用信号上升沿触发D触发器输出高电平去提起中断,在CPU主板响应中断后,通过控制D触发器清零端将输出的高电平拉低。以此避免非正常情况的出现。

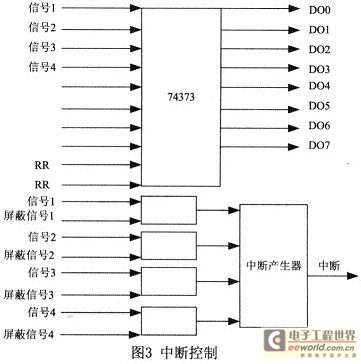

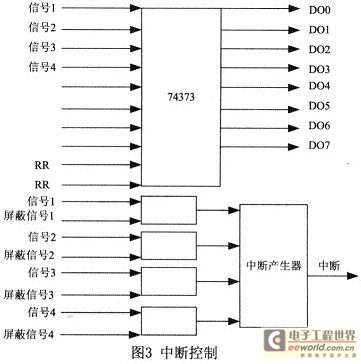

本模块设计了4路时统接收电路,可同时采集4路外部授时信号,在同时工作的情况下,系统可得到4种不同的时间信息。因此,设计时需要能够准确地识别4路不同的中断源。CPCI系统只能分配给每个CPCI设备1个中断号,使得各路中断源都要通过这1个中断号向CPU主板提起中断。设计过程中可以利用FPGA内部寄存器来识别各路中断源。见图3所示。

4路信号用寄存器74373的低4位识别,在系统响应中断后,随即读取寄存器,根据寄存器位的值,判断是由哪路信号源提起的中断。屏蔽信号用于系统关断任一路中断信号源,根据需要,可用软件屏蔽l路或多路信号源,未被屏蔽的信号进入中断产生器,输出中断信号,发起中断申请。

3 守时设计

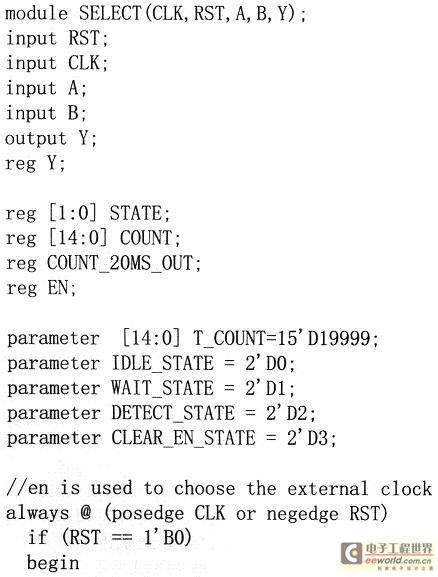

守时是指外部授时信号中断或受阻时,模块可以自行产生频率相同且脉冲沿一致的信号维持系统时间信息。在外部授时信号正常时,由其发起中断获得系统时间信息,无外部授时信号时,需由模块自行产生的信号自动接替外部授时信号的工作,同时用来维持时统信号输出,保证全系统的时间不中断。在FPGA中这部分功能由Verilog语言编写实现。

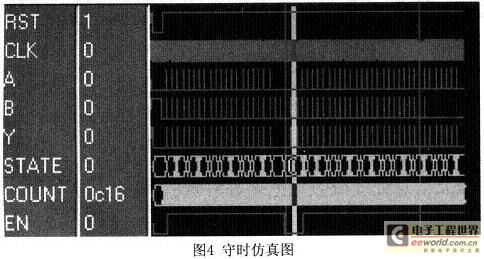

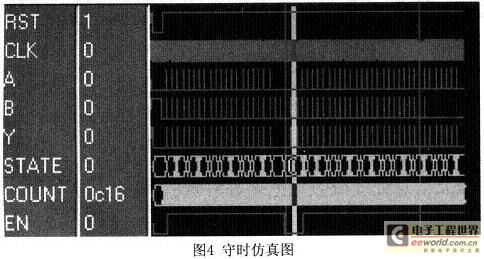

其中CLK(时钟)、RST(复位)、A(外部授时信号)、B(自产生信号)为输入信号。Y为输出信号,即中断信号。仿真结果如图4所示。

4 时间精度

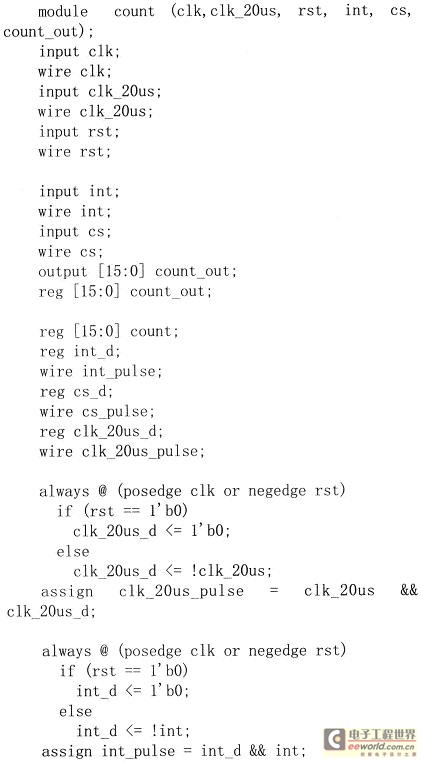

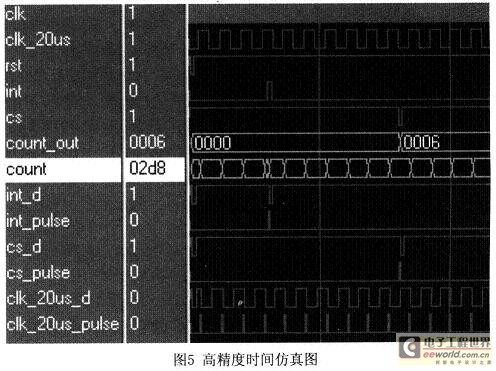

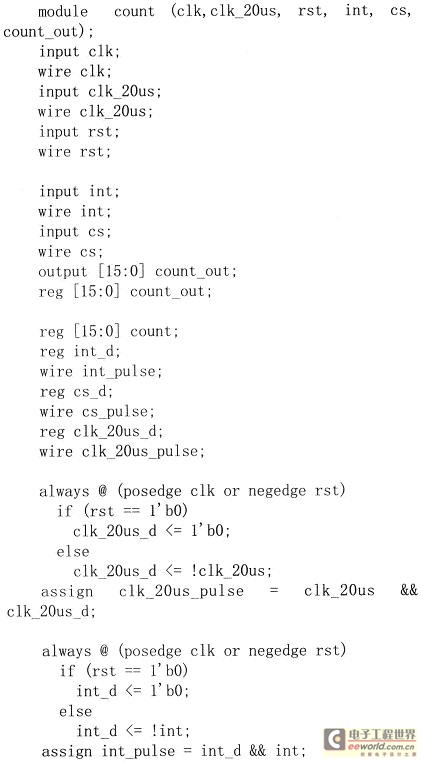

外部授时信号大多为1秒周期的秒脉冲信号,这时系统获得的时间只能精确到秒。在需要获得精确度更高的时间信息时,可利用FPGA中的计数器等来实现设计。见下面所示:

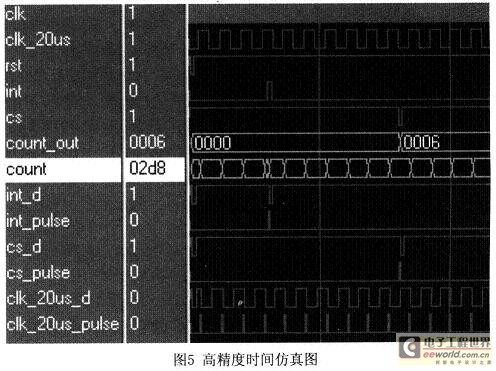

其中clk(时钟)、clk_20μs(20μs周期时钟)、rst(复位)、int(外部信号)、cs(锁存当前计数值)为输入信号。count_out为输出的16位二进制计数值(eount out[15..0])。本功能能够给出20μs精度的计数,在秒脉冲到来时(上升沿)产生中断,同时启动计数器,为20μs一次的计数,最大计数值为50000。计数值存入寄存器,可随时读取当前计数值,得出计数值后可换算成ms等其它值。其仿真结果如图5所示。

5 结束语

利用FPGA完成了作战系统对时统模块功能要求的设计,经在工程项目中使用验证,其功能完全满足要求。设计中使用的FPGA(EPM7256SRl208一lO)是一种高性能的CMOS EEPROM器件,通过4个引脚的JTAG接口能够进行在线编程,在开发过程中实现了快速有效的重复编程。借助其可重复编程使用的灵活性,通过改写FPGA内部逻辑来实现不同的功能需求,避免了硬件的重复设计,缩短了设计周期,适应了发展的需要。

FPGA为大规模可编程逻辑器件,具有编程方便、集成度高、速度快等特点,可反复编程、擦除、使用,在不改变硬件设计的情况下,可实现不同的功能需求。在FPGA中可完成各种时统功能设计。

1 原理

目前时统模块主要应用于Compact PCI(CPCI)系统,因此该时统模块为CPCI总线模块。其主要由总线桥接电路、FPGA、外围接口电路部分组成,如图1所示。接口电路采用MAXl490实现对时统输入信号(授时信号)的接收及转换。将差分信号转换成TTL电平信号提供给FPGA处理,另外将FPGA输出的TTL电平信号转换成差分信号作为时统信号提供给其它设备。

桥接电路采用PCI9052,实现CPCI总线到局部总线的过渡,并将中断信号通过CPCI总线的中断信号线送给CPU主板。CPU主板收到时统模块的中断请求后,做出响应,系统软件根据中断响应输出时间信息。

FPGA选用Altera公司MAX70O0S系列中的EPM7256SRl208—10,这是工业界中速度最快的高集成度可编程逻辑器件,具有5000个可用门和1256个宏单元,可满足设计需要。设计中,FPGA实现了对TTL电平时统信号的各种处理,主要包括中断控制、信号输出、守时、时间精度等功能。见图2所示。

下面具体介绍FPGA内部各主要功能的设计。

2 中断控制

中断控制部分主要包括脉冲识别、中断源判断等。为保证时统信号的准确识别,避免丢帧、误判,需要对信号整形,适当展宽。在FPGA中利用反相器对信号整形,利用信号上升沿触发D触发器输出高电平去提起中断,在CPU主板响应中断后,通过控制D触发器清零端将输出的高电平拉低。以此避免非正常情况的出现。

本模块设计了4路时统接收电路,可同时采集4路外部授时信号,在同时工作的情况下,系统可得到4种不同的时间信息。因此,设计时需要能够准确地识别4路不同的中断源。CPCI系统只能分配给每个CPCI设备1个中断号,使得各路中断源都要通过这1个中断号向CPU主板提起中断。设计过程中可以利用FPGA内部寄存器来识别各路中断源。见图3所示。

4路信号用寄存器74373的低4位识别,在系统响应中断后,随即读取寄存器,根据寄存器位的值,判断是由哪路信号源提起的中断。屏蔽信号用于系统关断任一路中断信号源,根据需要,可用软件屏蔽l路或多路信号源,未被屏蔽的信号进入中断产生器,输出中断信号,发起中断申请。

3 守时设计

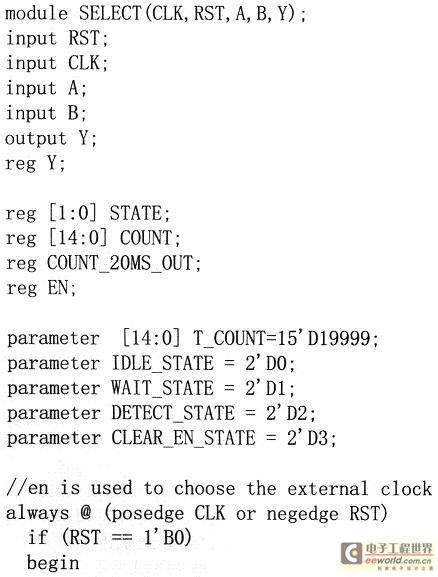

守时是指外部授时信号中断或受阻时,模块可以自行产生频率相同且脉冲沿一致的信号维持系统时间信息。在外部授时信号正常时,由其发起中断获得系统时间信息,无外部授时信号时,需由模块自行产生的信号自动接替外部授时信号的工作,同时用来维持时统信号输出,保证全系统的时间不中断。在FPGA中这部分功能由Verilog语言编写实现。

其中CLK(时钟)、RST(复位)、A(外部授时信号)、B(自产生信号)为输入信号。Y为输出信号,即中断信号。仿真结果如图4所示。

4 时间精度

外部授时信号大多为1秒周期的秒脉冲信号,这时系统获得的时间只能精确到秒。在需要获得精确度更高的时间信息时,可利用FPGA中的计数器等来实现设计。见下面所示:

其中clk(时钟)、clk_20μs(20μs周期时钟)、rst(复位)、int(外部信号)、cs(锁存当前计数值)为输入信号。count_out为输出的16位二进制计数值(eount out[15..0])。本功能能够给出20μs精度的计数,在秒脉冲到来时(上升沿)产生中断,同时启动计数器,为20μs一次的计数,最大计数值为50000。计数值存入寄存器,可随时读取当前计数值,得出计数值后可换算成ms等其它值。其仿真结果如图5所示。

5 结束语

利用FPGA完成了作战系统对时统模块功能要求的设计,经在工程项目中使用验证,其功能完全满足要求。设计中使用的FPGA(EPM7256SRl208一lO)是一种高性能的CMOS EEPROM器件,通过4个引脚的JTAG接口能够进行在线编程,在开发过程中实现了快速有效的重复编程。借助其可重复编程使用的灵活性,通过改写FPGA内部逻辑来实现不同的功能需求,避免了硬件的重复设计,缩短了设计周期,适应了发展的需要。

FPGA 总线 电路 Altera Verilog 仿真 CMOS 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)