基于FPGA的小数分频器的实现

时间:11-08

来源:互联网

点击:

频率合成技术是现代通讯系统的重要组成部分,他将一个高稳定和高准确度的基准频率,经过四则运算,产生同样稳定度和基准度的频率。分频器是集成电路中最基础也是最常用的电路。整数分频器的实现比较简单,可采用标准的计数器或可编程逻辑器件设计实现。但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。本文利用VerilogHDL硬件描述语言的设计方式,通过ModelSimSE开发软件进行仿真,设计基于FPGA的双模前置小数分频器。随着超大规模集成电路的发展,利用FPGA小数分频合成技术解决了单环数字频率合成器中高鉴相频率与小频间隔之间的矛盾。

1 双模前置小数分频原理

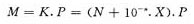

小数分频器的实现方法很多,但其基本原理一样,即在若干个分频周期中采取某种方法使某几个周期多计或少计一个数,从而在整个计数周期的总体平均意义上获得一个小数分频比,设要进行分频比为K的小数分频,K可表示为:

式中:n,N,X均为正整数;n为到X的位数,即K有n位小数。另一方面,分频比又可以写成:

式中:M为分频器输入脉冲数;P为输出脉冲数。

令P=10n,则:

以上是小数分频器的一种实现方法,即在进行10n次N分频时,设法多输入X个脉冲。

2 电路组成

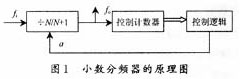

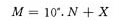

每个周期分频N+10-n.X,其电路双模前置小数分频器电路由÷N/N+1双模分频器、控制计数器和控制逻辑3部分组成。当a点电平为1时,进行÷N分频;当a点电平为0时进行÷N+1分频。适当设计控制逻辑,使在10n个分频周期中分频器有X次进行÷N+1分频,这样,当从fo输出10n个脉冲时,在fi处输入了X.(N+1)+(10n-X).N个脉冲,也就是10n.N+X个脉冲,其原理如图1所示。

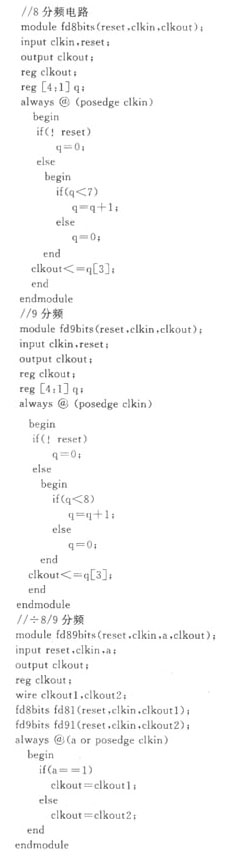

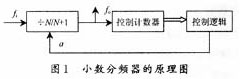

3 小数分频器的Verilog-HDL设计

现通过设计一个分频系数为8.7的分频器来给出使用VerilogHDL语言设计数字逻辑电路的一般设计方法。这里使用÷8/9双模前置分频器,按照前面的分析,可以通过计数器计数先做3次8分频,后做7次9分频,即可得到平均分频系数8.7。由于从N分频切换到N+1分频和从N+1分频切换到N分频都会产生一个随时间增长的相位移,如果简单的先进行3次8分频后做7次9分频将会产生很大的相位波动。考虑到该小数分频器要进行多次8分频和9分频,那么就设法将两种分频混合均匀,这种“均匀”工作是通过计数器来完成的,在这里只讨论一位小数的情况,下面简要介绍这种混合的方法:

每进行一次分频,计数值为10减去分频系数的小数部分,各次计数值累加。若累加结果小于10,则进行N+1分频,若大于10或等于10,则进行N分频。该例中计数值为(10-7)=3,前3次累加结果都小于10,所以为9分频,第四次累加结果为12,则去掉十位数后累加结果变为2,同时进行8分频,表1给出了该分频器的分频过程。

若分频系数后为两位小数,则用100减去分频系数的小数部分。用VerilogHDL设计÷8/9双模前置分频器的描述程序如下:

4 波形仿真

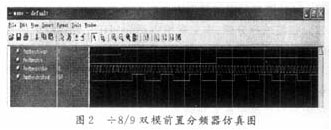

上述的÷8/9双模前置分频器的描述程序经ModelSim编译、时序模拟后,得到的波形如图2所示。

由图2可见,当reset为0时,分频器复位,当a为1时,进行8分频,当a为0时则进行9分频。

如图3所示,在前3个时钟,a值为0,则进行9分频,其后一个时钟a为1,进行8分频,后两个脉冲,又进行9分频,后进行一次8分频,然后又进行两次9分频,最后进行一次8分频。

5 电路实现

FPGA现场可编程门阵列(FieldProgrammableGateArray)是20世纪80年代中期出现的高密度可编程逻辑器件。FPGA及其软件系统是开发数字电路的最新技术。他利用EDA技术,以电路原理图、硬件描述语言、状态机等形式输入设计逻辑;他提供功能模拟、时序仿真等模拟手段,在功能模拟和时序仿真度满足要求后,经过一系列的变换,将输入逻辑转换成FPGA器件的编程文件,以实现专用集成电路。本设计选用Xilinx公司推出的90nm工艺制造的现场可编程门陈列Spartan-3来设计小数分频器,体积减小,可靠性提高。

6 结语

采用前置双频分频器设计的小数分频器,小数分频器的精度受控制计数器的影响,当n值为100时,小数分频的精度达到1/100;当n值为1000时,小数分频的精度达到1/1000;依此类推。FPGA有相当丰富的硬件资源,因此可以用FPGA设计高精度的小数分频器。采用FPGA组成的数字频率合成器,单环鉴相频率达100MHz以上,分辨率可达10-6。这种小数分频器得到了广泛的应用,例如,对图象采集系统中的行分频和列分频的设计,就可以应用本分频器电路作为时钟发生器。

1 双模前置小数分频原理

小数分频器的实现方法很多,但其基本原理一样,即在若干个分频周期中采取某种方法使某几个周期多计或少计一个数,从而在整个计数周期的总体平均意义上获得一个小数分频比,设要进行分频比为K的小数分频,K可表示为:

式中:n,N,X均为正整数;n为到X的位数,即K有n位小数。另一方面,分频比又可以写成:

式中:M为分频器输入脉冲数;P为输出脉冲数。

令P=10n,则:

以上是小数分频器的一种实现方法,即在进行10n次N分频时,设法多输入X个脉冲。

2 电路组成

每个周期分频N+10-n.X,其电路双模前置小数分频器电路由÷N/N+1双模分频器、控制计数器和控制逻辑3部分组成。当a点电平为1时,进行÷N分频;当a点电平为0时进行÷N+1分频。适当设计控制逻辑,使在10n个分频周期中分频器有X次进行÷N+1分频,这样,当从fo输出10n个脉冲时,在fi处输入了X.(N+1)+(10n-X).N个脉冲,也就是10n.N+X个脉冲,其原理如图1所示。

3 小数分频器的Verilog-HDL设计

现通过设计一个分频系数为8.7的分频器来给出使用VerilogHDL语言设计数字逻辑电路的一般设计方法。这里使用÷8/9双模前置分频器,按照前面的分析,可以通过计数器计数先做3次8分频,后做7次9分频,即可得到平均分频系数8.7。由于从N分频切换到N+1分频和从N+1分频切换到N分频都会产生一个随时间增长的相位移,如果简单的先进行3次8分频后做7次9分频将会产生很大的相位波动。考虑到该小数分频器要进行多次8分频和9分频,那么就设法将两种分频混合均匀,这种“均匀”工作是通过计数器来完成的,在这里只讨论一位小数的情况,下面简要介绍这种混合的方法:

每进行一次分频,计数值为10减去分频系数的小数部分,各次计数值累加。若累加结果小于10,则进行N+1分频,若大于10或等于10,则进行N分频。该例中计数值为(10-7)=3,前3次累加结果都小于10,所以为9分频,第四次累加结果为12,则去掉十位数后累加结果变为2,同时进行8分频,表1给出了该分频器的分频过程。

若分频系数后为两位小数,则用100减去分频系数的小数部分。用VerilogHDL设计÷8/9双模前置分频器的描述程序如下:

4 波形仿真

上述的÷8/9双模前置分频器的描述程序经ModelSim编译、时序模拟后,得到的波形如图2所示。

由图2可见,当reset为0时,分频器复位,当a为1时,进行8分频,当a为0时则进行9分频。

如图3所示,在前3个时钟,a值为0,则进行9分频,其后一个时钟a为1,进行8分频,后两个脉冲,又进行9分频,后进行一次8分频,然后又进行两次9分频,最后进行一次8分频。

5 电路实现

FPGA现场可编程门阵列(FieldProgrammableGateArray)是20世纪80年代中期出现的高密度可编程逻辑器件。FPGA及其软件系统是开发数字电路的最新技术。他利用EDA技术,以电路原理图、硬件描述语言、状态机等形式输入设计逻辑;他提供功能模拟、时序仿真等模拟手段,在功能模拟和时序仿真度满足要求后,经过一系列的变换,将输入逻辑转换成FPGA器件的编程文件,以实现专用集成电路。本设计选用Xilinx公司推出的90nm工艺制造的现场可编程门陈列Spartan-3来设计小数分频器,体积减小,可靠性提高。

6 结语

采用前置双频分频器设计的小数分频器,小数分频器的精度受控制计数器的影响,当n值为100时,小数分频的精度达到1/100;当n值为1000时,小数分频的精度达到1/1000;依此类推。FPGA有相当丰富的硬件资源,因此可以用FPGA设计高精度的小数分频器。采用FPGA组成的数字频率合成器,单环鉴相频率达100MHz以上,分辨率可达10-6。这种小数分频器得到了广泛的应用,例如,对图象采集系统中的行分频和列分频的设计,就可以应用本分频器电路作为时钟发生器。

集成电路 电路 Verilog ModelSim 仿真 FPGA EDA Xilinx 相关文章:

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA 重复配置和测试的实现(08-14)

- 适用于消费性市场的nano FPGA技术(09-27)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)