利用现成FPGA开发板进行ASIC原型开发

时间:11-08

来源:互联网

点击:

手工分割和综合多个FPGA设计

在手工分割的情况下,任何ASIC中心结构(门控时钟,Synopsys的DesignWare?实例等),在原始的RTL源代码中,在进行分割之前,不得不手工将它们翻译为与它们的FPGA相等同的代码。除其它东西之外,这直接导致了两个分离的代码流,这可能失去同步,从而导致在FPGA原型和ASIC之间所代表的功能不同。

当开始分割处理时,工程师们尝试将不同的功能模块组集合在一起,在这里每组在不同的FPGA上实现。这种组合(分割)以门级的传统方式实现。最近,一些流程支持在RTL级分组,此时每个分成的组通过传统的FPGA综合工具,并且仅在这一点上,不同FPGA的实际资源利用是已知的。

所有这些方案都有一个问题,就是对于不同组的面积和资源的影响而言,工程师们是“临时的盲人”,这导致了许多耗时的迭代。首先,工程师根据“A模块可能将消耗‘xxx’的资源,而模块B可能要求‘yyy’的资源”而进行“估算”。这些估算是根据大量“分组”命令,然后综合(在基于RTL分割的情况下),然后是结果的分析,以及然后是大量的“取消组”和“再次分组”命令来估算不同的实现方式。

该任务由于这一事实而进一步混淆,该事实就是这些原型经常被FPGA上的I/O管脚的数量所限制;一个无效的解决方案很容易耗费一个器件上100%的I/O资源,然而与此同时,仅仅其相对少量的内部逻辑资源可以实现。为了克服这些I/O限制,I/O的多重分组和/或在多个FPGA中复制同一个逻辑模块是必要的。(为了达到特定的性能目标,逻辑复制也是经常要求的。)

假设在这种原型中使用的每个FPGA可能有超过1000个管脚,一项管理连接的电子表格方法能很容易地包含几千个单元。不足为奇地是,记录分配给每个FPGA的模块和连接矩阵(在不同FPGA之间的连接)是一项繁重的任务,这将是资源密集型的、耗时的以及容易出错的。

自动分割和综合多个FPGA设计

来自Synplicity的Certify? RTL原型开发工具是业内时间最长和最强大的多个FPGA分割和综合工具。很令人感兴趣的是,当Certify软件在上世纪90年代晚期创立时,对ASIC设计团队而言,没有任何现成的多个FPGA原型开发板能够得到。在那时,Certify软件被设计成一个ASIC团队设计他们自己的定制的多个FPGA原型开发板的辅助工具。

使用Certify软件,工程师们能够定义电路板上的FPGA的数量和类型以及它们之间的互连线。随后,该数据被用于对通过多个FPGA进行ASIC设计自动地分割RTL,并且将被分割的RTL综合成用于FPGA编程的配置文件。

一旦工程师们已经使用Certify工具来定义电路板的基本结构,来自该软件的输出之一是描述FPGA以及它们之间连接的网表。以Verilog来描述的该网表的格式由Synplicity定义,并且是知名的*.vb(Verilog模版)格式。

设计团队希望建立他们自己的定制电路板今天仍然使用这种技术。这一点使得Synplicity的*.vb格式很快变成这种类型应用的事实上的工业标准。现在,每个现成的多个FPGA原型开发板供应商采用通用的*.vb文件交付他们的电路板,其作为定义每块开发板结构的输入被读入到Certify软件。

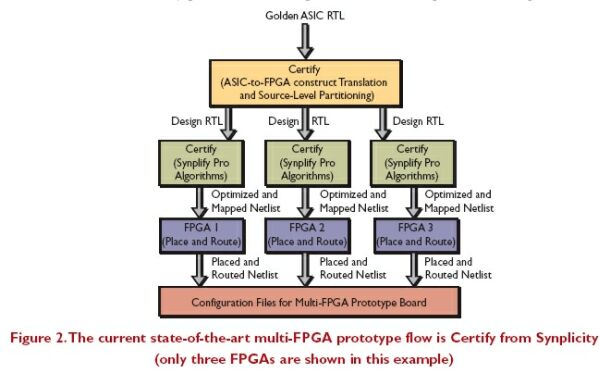

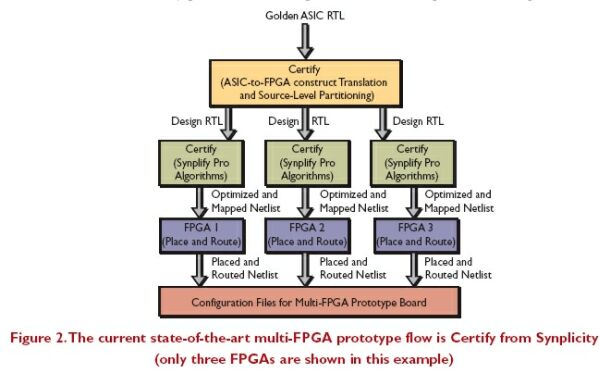

Certify工具能够采用Verilog、VHDL和混合语言进行设计。该流程中的第一个要素是采用Certify软件,自动将任何ASIC专用代码转换为相当的FPGA结构。就目前现成的多个FPGA原型开发板而言,用户简单地通知软件使用下拉式列表框的开发板的类型,该列表框包括来自所有主要第三方供应商所提供的开发板。(换句话说,如果这是一块定制的电路板,Certify工具有能力建立一个在传输过程中的“虚拟的”多个FPGA开发板,接下来这块虚拟的开发板能够作为建立真实电路板的基础来使用。)接下来,Certify软件用于通过多个FPGA自动分割设计(图 2)。

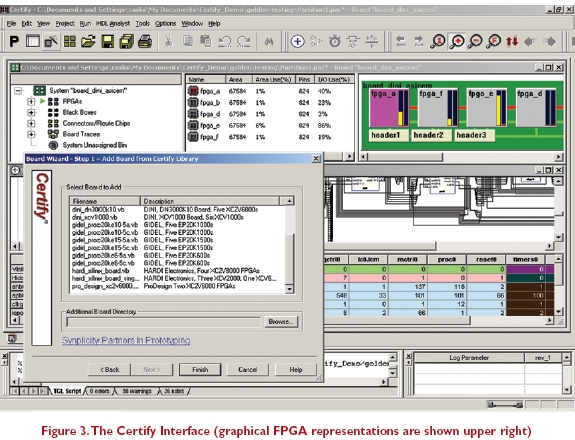

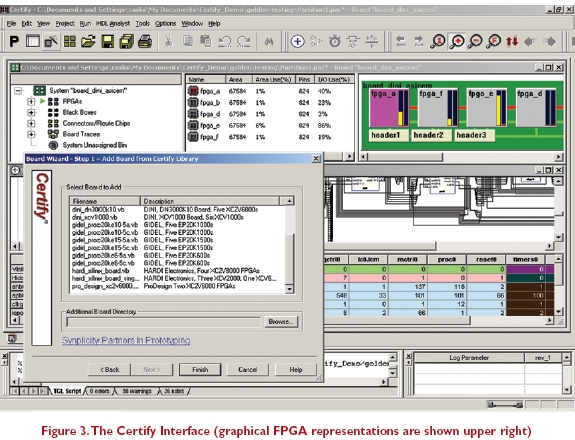

与Certify软件紧密集成在一起的是Synplicity的HDL分析器,其以高级的层次化的模块图以及接着综合相应的门级电路的形式,自动地产生设计的技术独立的图形视图。Certify和HDL分析器工具在HDL源代码和模块级以及门级电路之间,支持全双向交叉探测,所以允许设计者在设计以及定位感兴趣的信号和逻辑功能之间,进行快速定位。除设计的各种其他视图之外,Certify软件提供一个形成原型开发板的FPGA的图形表示(第6页图3)。这些虚拟器件中的每一个有两个关联的“温度计型”显示:其反映I/O的应用和器件的其他面积/资源应用。

以I/O和相关的逻辑资源以及FPGA和在FPGA之间的布线资源的认识为基础,Certify软件能够自动地实现管脚分配和交互地执行分割——通过简单地拖曳代码模块和将它们下拉到不同的FPGA——或者两种技术可以混合使用。

Certify软件提供大量非常强大的工具来帮助分割任务。例如,接下来的分割,软件能够分析结果和向用户提出使用Certify管脚复用(CPM)的时机,信号的复合设置是一起复用来减轻在相关器件I/O资源上的负载。除了在多个器件上促进逻辑复制外,Certify工具也提供位片应用,其中宽的数据路径结构能够分裂成更小的分支。此外,Certify软件提供成熟的“撕裂”能力,借此将大的模块分解成更小的部分(这些部分能够依次分配给不同的FPGA)。

作为一个候选的分割实现方式就是建立,其他非常有用的特性使其能够被命名和保存。这允许用户维持对多个可选择的分割方案的控制。这种能力能够与Certify软件的影响分析特征一道使用,其允许用户就在该多个FPGA开发板上能够得到的面积和I/O而论,估计布局和/或移动逻辑。而不是用户不得不推测这个逻辑应该被分配给哪个FPGA,影响分析产生关于以那个分割决定为基础的特定信息。

一旦分割已经被执行,Certify软件用于综合与不同的FPGA器件有关的代码流。该工具使用同一个基本的综合技术,就是起重要作用的Synplicity的主导市场的Synplify Pro? FPGA综合引擎。例如,Certify软件充分利用Synplicity的BEST? (Behavior Extracting Synthesis Technology?)算法,其分析RTL和在主要综合步骤前实现高级优化。并且,Certify工具以拥有Synplify Pro软件的先进的综合能力为自豪,例如资源共享、寄存器平衡、重定时、复制以及再次综合。

这个过程一个关键的方面是Certify软件把不同的FPGA简单看作设计层次中一个额外的层。这意味着该工具提供针对性能优化时序路径的独特能力,甚至当这些路径越过多个FPGA时(Certify软件也能够提供一个时序报告,其告知设计者原型在硬件被编程之前能够达到的性能)。

在手工分割的情况下,任何ASIC中心结构(门控时钟,Synopsys的DesignWare?实例等),在原始的RTL源代码中,在进行分割之前,不得不手工将它们翻译为与它们的FPGA相等同的代码。除其它东西之外,这直接导致了两个分离的代码流,这可能失去同步,从而导致在FPGA原型和ASIC之间所代表的功能不同。

当开始分割处理时,工程师们尝试将不同的功能模块组集合在一起,在这里每组在不同的FPGA上实现。这种组合(分割)以门级的传统方式实现。最近,一些流程支持在RTL级分组,此时每个分成的组通过传统的FPGA综合工具,并且仅在这一点上,不同FPGA的实际资源利用是已知的。

所有这些方案都有一个问题,就是对于不同组的面积和资源的影响而言,工程师们是“临时的盲人”,这导致了许多耗时的迭代。首先,工程师根据“A模块可能将消耗‘xxx’的资源,而模块B可能要求‘yyy’的资源”而进行“估算”。这些估算是根据大量“分组”命令,然后综合(在基于RTL分割的情况下),然后是结果的分析,以及然后是大量的“取消组”和“再次分组”命令来估算不同的实现方式。

该任务由于这一事实而进一步混淆,该事实就是这些原型经常被FPGA上的I/O管脚的数量所限制;一个无效的解决方案很容易耗费一个器件上100%的I/O资源,然而与此同时,仅仅其相对少量的内部逻辑资源可以实现。为了克服这些I/O限制,I/O的多重分组和/或在多个FPGA中复制同一个逻辑模块是必要的。(为了达到特定的性能目标,逻辑复制也是经常要求的。)

假设在这种原型中使用的每个FPGA可能有超过1000个管脚,一项管理连接的电子表格方法能很容易地包含几千个单元。不足为奇地是,记录分配给每个FPGA的模块和连接矩阵(在不同FPGA之间的连接)是一项繁重的任务,这将是资源密集型的、耗时的以及容易出错的。

自动分割和综合多个FPGA设计

来自Synplicity的Certify? RTL原型开发工具是业内时间最长和最强大的多个FPGA分割和综合工具。很令人感兴趣的是,当Certify软件在上世纪90年代晚期创立时,对ASIC设计团队而言,没有任何现成的多个FPGA原型开发板能够得到。在那时,Certify软件被设计成一个ASIC团队设计他们自己的定制的多个FPGA原型开发板的辅助工具。

使用Certify软件,工程师们能够定义电路板上的FPGA的数量和类型以及它们之间的互连线。随后,该数据被用于对通过多个FPGA进行ASIC设计自动地分割RTL,并且将被分割的RTL综合成用于FPGA编程的配置文件。

一旦工程师们已经使用Certify工具来定义电路板的基本结构,来自该软件的输出之一是描述FPGA以及它们之间连接的网表。以Verilog来描述的该网表的格式由Synplicity定义,并且是知名的*.vb(Verilog模版)格式。

设计团队希望建立他们自己的定制电路板今天仍然使用这种技术。这一点使得Synplicity的*.vb格式很快变成这种类型应用的事实上的工业标准。现在,每个现成的多个FPGA原型开发板供应商采用通用的*.vb文件交付他们的电路板,其作为定义每块开发板结构的输入被读入到Certify软件。

Certify工具能够采用Verilog、VHDL和混合语言进行设计。该流程中的第一个要素是采用Certify软件,自动将任何ASIC专用代码转换为相当的FPGA结构。就目前现成的多个FPGA原型开发板而言,用户简单地通知软件使用下拉式列表框的开发板的类型,该列表框包括来自所有主要第三方供应商所提供的开发板。(换句话说,如果这是一块定制的电路板,Certify工具有能力建立一个在传输过程中的“虚拟的”多个FPGA开发板,接下来这块虚拟的开发板能够作为建立真实电路板的基础来使用。)接下来,Certify软件用于通过多个FPGA自动分割设计(图 2)。

与Certify软件紧密集成在一起的是Synplicity的HDL分析器,其以高级的层次化的模块图以及接着综合相应的门级电路的形式,自动地产生设计的技术独立的图形视图。Certify和HDL分析器工具在HDL源代码和模块级以及门级电路之间,支持全双向交叉探测,所以允许设计者在设计以及定位感兴趣的信号和逻辑功能之间,进行快速定位。除设计的各种其他视图之外,Certify软件提供一个形成原型开发板的FPGA的图形表示(第6页图3)。这些虚拟器件中的每一个有两个关联的“温度计型”显示:其反映I/O的应用和器件的其他面积/资源应用。

以I/O和相关的逻辑资源以及FPGA和在FPGA之间的布线资源的认识为基础,Certify软件能够自动地实现管脚分配和交互地执行分割——通过简单地拖曳代码模块和将它们下拉到不同的FPGA——或者两种技术可以混合使用。

Certify软件提供大量非常强大的工具来帮助分割任务。例如,接下来的分割,软件能够分析结果和向用户提出使用Certify管脚复用(CPM)的时机,信号的复合设置是一起复用来减轻在相关器件I/O资源上的负载。除了在多个器件上促进逻辑复制外,Certify工具也提供位片应用,其中宽的数据路径结构能够分裂成更小的分支。此外,Certify软件提供成熟的“撕裂”能力,借此将大的模块分解成更小的部分(这些部分能够依次分配给不同的FPGA)。

作为一个候选的分割实现方式就是建立,其他非常有用的特性使其能够被命名和保存。这允许用户维持对多个可选择的分割方案的控制。这种能力能够与Certify软件的影响分析特征一道使用,其允许用户就在该多个FPGA开发板上能够得到的面积和I/O而论,估计布局和/或移动逻辑。而不是用户不得不推测这个逻辑应该被分配给哪个FPGA,影响分析产生关于以那个分割决定为基础的特定信息。

一旦分割已经被执行,Certify软件用于综合与不同的FPGA器件有关的代码流。该工具使用同一个基本的综合技术,就是起重要作用的Synplicity的主导市场的Synplify Pro? FPGA综合引擎。例如,Certify软件充分利用Synplicity的BEST? (Behavior Extracting Synthesis Technology?)算法,其分析RTL和在主要综合步骤前实现高级优化。并且,Certify工具以拥有Synplify Pro软件的先进的综合能力为自豪,例如资源共享、寄存器平衡、重定时、复制以及再次综合。

这个过程一个关键的方面是Certify软件把不同的FPGA简单看作设计层次中一个额外的层。这意味着该工具提供针对性能优化时序路径的独特能力,甚至当这些路径越过多个FPGA时(Certify软件也能够提供一个时序报告,其告知设计者原型在硬件被编程之前能够达到的性能)。

FPGA DSP SoC 嵌入式 仿真 电路 USB 电子 Verilog VHDL Altera 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)