FPGA设计的验证技术及应用原则

时间:09-25

来源:互联网

点击:

选择层次

取得层次模拟成功的一个主要部分是选取层次。没有现成的公式可用于选择正确的层次。这就是为什么没有对或错的层次的原因,虽然在试图选取层次还是有些原则可资借鉴的。确保满足如下这些原则永远是明智之举。

1)设计应当是完全同步的。

2)所有关键路径应包括在一个逻辑组(可被分别同步的设计的一部分)中。典型情况,每个逻辑组应是在设计顶层例示(instantiated)的Verilog内的一个模块或VHDL内的一个实体 。

3)全部IOB(输入/输出块)逻辑应在顶层。器件的任一个输入和输出应在顶层及I/O缓冲器和I/O三态门内进行声明。但,逻辑组内例示的I/O逻辑是可接受的。

4)在每个逻辑组的输入和/或输出应放置寄存器。高明的作法是在逻辑组的边界对所有输入信号或输出信号进行寄存处理。它确保逻辑组内的所有关键路径得到保持并免去了当通过逻辑组边界进行逻辑优化时可能导致的问题。在设计中的所有层次组内都应一致遵守该规则。

5)顶层应只包含例示的模块或实体、IOB逻辑及时钟逻辑(DCM、BUFG等)。

6)选择逻辑组时,应不使任一组过小以至对其单独进行验证的价值不大或不太关乎大局,还应不使任一组过大以便当发生问题时难以模拟和调试。但对此没有确切的定律,另外,它可根据设计和验证要求而变。

7)选择逻辑组时还应注意使设计中最可能在后续设计流中被改动的部分与设计中更稳定的部分独立开来。这样,当进行了这种明智选择后,以后的设计变更对验证时间产生的影响最小。

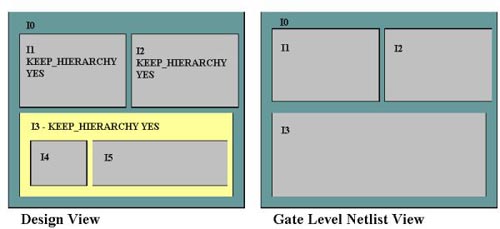

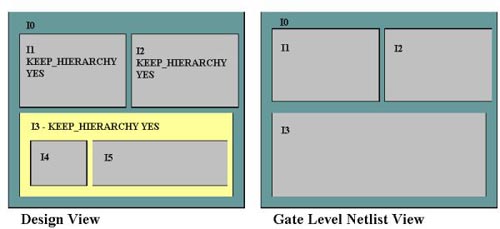

只要遵循上述提到的规则,保持层次就该不会对设计性能产生影响。为从保有的层次中得到最大利益,只应将其应用在设计中的其端口在门级模拟中需要可见性的块中。一般情况,这些块是遵循了上述规则的上层块。通过对选择的块限制其保留层次,综合和实现工具将具有更多的自由以优化设计并改进性能。下图2显示的是在一个范例设计中可在哪里保留层次的例子。

应注意的是这里只有指导方针。没有指定如何选择或保持层次的确定规则。它的确因设计而异、因用户而不同。应由用户来决定在哪里保持层次对验证最有价值、以及在哪里应将其解构。

层次验证进入实战

为对在时序仿真中采用层次方法的可能好处进行量化,我们将检查两个设计:VHDL和Verilog各一个,它们都是以中等规模Xilinx FPGA为目标器件的,且采用了500微秒的Model Technology ModelSim SE模拟器进行模拟。这些模拟是在带2GB RDRAM存储器的双2.0 GHz Xeon计算机上在Linux环境下运行的。这是为表现该方法论能显现的量值差别所进行的一个适当的尝试,它并不一定代表典型的模拟运行时间或存储器需求。

VHDL设计在一定程度上代表了典型的以DSP为导向的设计,这里用的是Xilinx的 Virtex-4 SX35 FPGA。我们选择将设计分为9个子层和一个顶层,在每个期望子层都放置一个KEEP_HIERARCHY。

在该测试中,我们选取代码最不稳定的部分,也即在设计流的这一部分它频繁改变。执行一个相对简单的模拟,并比较TRL模拟时间与设计的时序仿真时间,我们发现它对运行时间和存储器容量要求有显著增加,见下表1。但,若我们采取仅对设计的改变部分施以时序仿真的方法,我们可相应降低运行时间24倍、减小存储器容量21倍。即使我们选择仅采用改变的部分对整个设计进行时序验证,我们看到,与完全RTL模拟相比,其所需的运行时间和存储器容量与完全RTL模拟相比也只需增加约一倍。与更传统的全时序仿真相比,其对上述两个指标的要求也有大幅降低。

看Verilog设计,它代表了某种更大更复杂数据路径方式的设计,我们以Xilinx Virtex-4 LX80 FPGA为目标器件。我们将其分为14个子层和一个顶层,采用KEEP_HIERARCHY约束以支持分段时序仿真。我们看到,与VHDL运行相比,所需的时间长了些,但对该设计仍取得类似的改进。仅对改变部分进行的时序仿真与对整个设计进行时序仿真相比,运行时间和模拟存储器分别节省了6.3和6.6倍。仅将设计的改变部分代替以时序仿真网络表然后模拟整个RTL设计,运行时间和存储器需求仍分别缩短了3.6倍、减小了 5.5倍。

在两个设计中,被改变模块的覆盖范围完全相当,且因为更快的运行时间以及需分析的设计更小,设计调试变得更容易。也许因为需要更大的存储器,模拟器用起来也更觉灵便。我们注意到,采用该方法论(扩展了验证设计的可用资源并允许并行运行以进一步降低总体运行时间),可能用一款较低端的计算机(速度更慢、存储器更少)执行该模拟。

取得层次模拟成功的一个主要部分是选取层次。没有现成的公式可用于选择正确的层次。这就是为什么没有对或错的层次的原因,虽然在试图选取层次还是有些原则可资借鉴的。确保满足如下这些原则永远是明智之举。

1)设计应当是完全同步的。

2)所有关键路径应包括在一个逻辑组(可被分别同步的设计的一部分)中。典型情况,每个逻辑组应是在设计顶层例示(instantiated)的Verilog内的一个模块或VHDL内的一个实体 。

3)全部IOB(输入/输出块)逻辑应在顶层。器件的任一个输入和输出应在顶层及I/O缓冲器和I/O三态门内进行声明。但,逻辑组内例示的I/O逻辑是可接受的。

4)在每个逻辑组的输入和/或输出应放置寄存器。高明的作法是在逻辑组的边界对所有输入信号或输出信号进行寄存处理。它确保逻辑组内的所有关键路径得到保持并免去了当通过逻辑组边界进行逻辑优化时可能导致的问题。在设计中的所有层次组内都应一致遵守该规则。

5)顶层应只包含例示的模块或实体、IOB逻辑及时钟逻辑(DCM、BUFG等)。

6)选择逻辑组时,应不使任一组过小以至对其单独进行验证的价值不大或不太关乎大局,还应不使任一组过大以便当发生问题时难以模拟和调试。但对此没有确切的定律,另外,它可根据设计和验证要求而变。

7)选择逻辑组时还应注意使设计中最可能在后续设计流中被改动的部分与设计中更稳定的部分独立开来。这样,当进行了这种明智选择后,以后的设计变更对验证时间产生的影响最小。

只要遵循上述提到的规则,保持层次就该不会对设计性能产生影响。为从保有的层次中得到最大利益,只应将其应用在设计中的其端口在门级模拟中需要可见性的块中。一般情况,这些块是遵循了上述规则的上层块。通过对选择的块限制其保留层次,综合和实现工具将具有更多的自由以优化设计并改进性能。下图2显示的是在一个范例设计中可在哪里保留层次的例子。

应注意的是这里只有指导方针。没有指定如何选择或保持层次的确定规则。它的确因设计而异、因用户而不同。应由用户来决定在哪里保持层次对验证最有价值、以及在哪里应将其解构。

层次验证进入实战

为对在时序仿真中采用层次方法的可能好处进行量化,我们将检查两个设计:VHDL和Verilog各一个,它们都是以中等规模Xilinx FPGA为目标器件的,且采用了500微秒的Model Technology ModelSim SE模拟器进行模拟。这些模拟是在带2GB RDRAM存储器的双2.0 GHz Xeon计算机上在Linux环境下运行的。这是为表现该方法论能显现的量值差别所进行的一个适当的尝试,它并不一定代表典型的模拟运行时间或存储器需求。

VHDL设计在一定程度上代表了典型的以DSP为导向的设计,这里用的是Xilinx的 Virtex-4 SX35 FPGA。我们选择将设计分为9个子层和一个顶层,在每个期望子层都放置一个KEEP_HIERARCHY。

在该测试中,我们选取代码最不稳定的部分,也即在设计流的这一部分它频繁改变。执行一个相对简单的模拟,并比较TRL模拟时间与设计的时序仿真时间,我们发现它对运行时间和存储器容量要求有显著增加,见下表1。但,若我们采取仅对设计的改变部分施以时序仿真的方法,我们可相应降低运行时间24倍、减小存储器容量21倍。即使我们选择仅采用改变的部分对整个设计进行时序验证,我们看到,与完全RTL模拟相比,其所需的运行时间和存储器容量与完全RTL模拟相比也只需增加约一倍。与更传统的全时序仿真相比,其对上述两个指标的要求也有大幅降低。

看Verilog设计,它代表了某种更大更复杂数据路径方式的设计,我们以Xilinx Virtex-4 LX80 FPGA为目标器件。我们将其分为14个子层和一个顶层,采用KEEP_HIERARCHY约束以支持分段时序仿真。我们看到,与VHDL运行相比,所需的时间长了些,但对该设计仍取得类似的改进。仅对改变部分进行的时序仿真与对整个设计进行时序仿真相比,运行时间和模拟存储器分别节省了6.3和6.6倍。仅将设计的改变部分代替以时序仿真网络表然后模拟整个RTL设计,运行时间和存储器需求仍分别缩短了3.6倍、减小了 5.5倍。

在两个设计中,被改变模块的覆盖范围完全相当,且因为更快的运行时间以及需分析的设计更小,设计调试变得更容易。也许因为需要更大的存储器,模拟器用起来也更觉灵便。我们注意到,采用该方法论(扩展了验证设计的可用资源并允许并行运行以进一步降低总体运行时间),可能用一款较低端的计算机(速度更慢、存储器更少)执行该模拟。

FPGA 仿真 Xilinx VHDL Verilog ModelSim Linux DSP 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)