基于FPGA的高速数据采集系统接口设计

时间:09-04

来源:互联网

点击:

(1)参考时钟

高性能的通信质量要求有高稳定性和高精度的时钟源。抖动和频偏是衡量时钟源的两个重要指标。频偏是指时钟标称频率与实际频率的偏差,主要是受晶体精度的影响,由于RocketIO模块内部将输入参考时钟20倍频,而RocketIO模块可容忍的输入参考时钟抖动公差为40ps,可见参考时钟的抖动对其性能有直接影响,所以必须选择性能优良的参考时钟。抖动一般是指一个实际情况下的周期信号每个周期的图样相对于该信号理想情况下一个周期图样的偏差。抖动产生的原因包括:时钟晶体本身的机械振动、器件的热噪声和电源串入噪声等。抖动可以分为确定性抖动和随机抖动,确定性抖动包括信号在传输中煤质损耗、码间串扰(ISI)等周期性因素导致的抖动;随机抖动是由半导体器件热噪声、电源波动等共模随机噪声源导致的。在Virtex Ⅱ-PRO系列FPGA中,RocketIO模块集中分布在上、下4个通道中,当RocketIO工作在2.0 Gbaud以上时,参考时钟应采用差分输入方式(如LVDS、LVPECH),由上述4个通道的专用差分时钟引脚输入,至相同时钟信号引入不必要的抖动,在2.0 Gbaud速率以下应用时,不要用FPGA内部的DCM来生成RocketIO的输入时钟,因为经DCM倍频的时钟会引入较大的抖动,使RocketIO的接收锁相环无法稳定地锁定发送时钟,致使系统无法正常工作。

(2)复位

在Virtex Ⅱ-PRO系列FPGA中,RocketIO模块的复位引脚分为发送(TX_RESET)和接收(RX_RESET)两部分。由于DCM在输出时钟锁定在设定值前,输出时钟处于不稳定状态,不能用作内部逻辑电路时钟,所以要在DCM时钟输出锁定有效,并经过适当延迟后才可将片内逻辑复位。RocketIO模块要求复位输入至少保持2个USRCLK时钟周期来完成内部FIFO的初始化。

(3)PCB设计

在PCB的设计中,应使差分线对内的长度相互匹配,以减少信号扭曲。为使设计传输速率达到2.0 Gbaud,在差分线对内部每个走线区间内的实际布线公差应控制在5 mil内。差分线对内两条线之间的距离应尽可能小,以使外部干扰为共模特征。差分线对间的距离应尽可能保持一致,以降低差分阻抗分布的不连续性。采用电源层作为差分线的信号回路,因为电源平面有最小的传输阻抗,从而减少噪声,由于每个过孔可带来0.5-1.0dB的损耗,应尽量减少过孔数目。过孔的通孔和焊盘应有尽量小的物理尺寸,并且在通孔穿越的未连接不加焊盘,差分对内的过孔不仅在数量上要匹配,而且在放置的位置上也要接近,以使阻抗分布尽量一致,避免导致阻抗不连续的90°走线,而要用圆弧或45°折线来代替。走线时应使向左、向右折角的数量接近,这样可减少信号经差分线传输引起的扭曲。在模拟数字混合系统设计中,首先,应在电源和地线之间加上去耦电容;其次,尽量加宽电源和地线宽度,最好是地线比电源线宽,使得地线宽度>电源线宽度>信号线宽度;第三,使用统一地,而将PCB分区为模拟部分和数字部分,模拟信号在电路板所有层的模拟区内布线,而数字信号在数字电路区内布线,在这种情况下,数字信号返回电流不会流入到模拟信号的地。经过以上设计,噪声影响明显降低。

4 接口解决方案

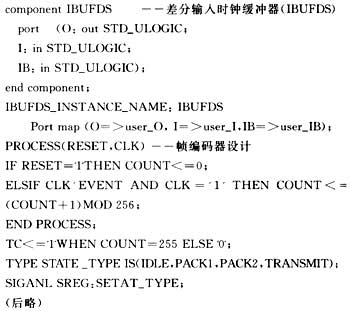

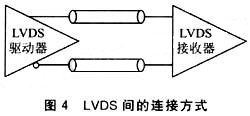

随着高速数据传输业务需求的增加,如何高质量地解决高速IC芯片的相互连接变得越来越重要,低功耗及高的信噪比是有待解决的主要问题。本文所介绍的高速采集系统中芯片间有两种接口:PECL和LVDS,如何进行两接口相互连接就成为一个影响系统性能的关键因素,LVDS的输入与输出都是内匹配的,所以LVDS间的连接可采用图4所示的直接连接,在FPGA内,需对差分输入时钟缓冲器(IBUFDS),差分输入的全局时钟缓冲区(IBUFGDS)和差分输出时钟缓冲器(OBUFDS)例化,在本项目的应用中,发送及接收FIFO的设计用了双口块内存(Block RAM),时钟倍频器用了延迟锁定环(DLL),帧解码器由30位并行数据产生器、同步字检测阵列和接收状态机组成。

FPGA的部分代码如下:

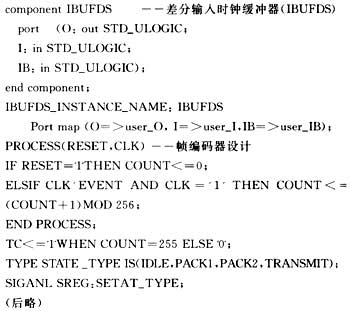

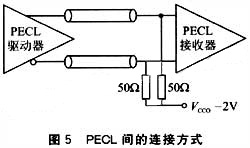

PECL间的连接一般常用直流耦合。在直流耦合情况下,PECL输出设计驱动50Ω负载至(VCC-2V),电路如图5所示。

FPGA的部分代码如下:

经实际测试,输入输出指标均符号系统要求,在硬件电路设计中,由于LVDS信号的偏置电压为1.25V,电压摆幅只有350mV,传输速率≥100Mb/s;因此,电路板制作至关重要,要求至少使用四层板。为使干扰信号以共模方式加到差分线对上(不影响数据正确性),要求差分线对间的距离尽可能小。电源方面,FPGA芯片上电时要求有大于500mA的驱动电流,同时,由于多个输出引脚的电位速度变化,要求每对电源和地引脚都要良好旁路。

高性能的通信质量要求有高稳定性和高精度的时钟源。抖动和频偏是衡量时钟源的两个重要指标。频偏是指时钟标称频率与实际频率的偏差,主要是受晶体精度的影响,由于RocketIO模块内部将输入参考时钟20倍频,而RocketIO模块可容忍的输入参考时钟抖动公差为40ps,可见参考时钟的抖动对其性能有直接影响,所以必须选择性能优良的参考时钟。抖动一般是指一个实际情况下的周期信号每个周期的图样相对于该信号理想情况下一个周期图样的偏差。抖动产生的原因包括:时钟晶体本身的机械振动、器件的热噪声和电源串入噪声等。抖动可以分为确定性抖动和随机抖动,确定性抖动包括信号在传输中煤质损耗、码间串扰(ISI)等周期性因素导致的抖动;随机抖动是由半导体器件热噪声、电源波动等共模随机噪声源导致的。在Virtex Ⅱ-PRO系列FPGA中,RocketIO模块集中分布在上、下4个通道中,当RocketIO工作在2.0 Gbaud以上时,参考时钟应采用差分输入方式(如LVDS、LVPECH),由上述4个通道的专用差分时钟引脚输入,至相同时钟信号引入不必要的抖动,在2.0 Gbaud速率以下应用时,不要用FPGA内部的DCM来生成RocketIO的输入时钟,因为经DCM倍频的时钟会引入较大的抖动,使RocketIO的接收锁相环无法稳定地锁定发送时钟,致使系统无法正常工作。

(2)复位

在Virtex Ⅱ-PRO系列FPGA中,RocketIO模块的复位引脚分为发送(TX_RESET)和接收(RX_RESET)两部分。由于DCM在输出时钟锁定在设定值前,输出时钟处于不稳定状态,不能用作内部逻辑电路时钟,所以要在DCM时钟输出锁定有效,并经过适当延迟后才可将片内逻辑复位。RocketIO模块要求复位输入至少保持2个USRCLK时钟周期来完成内部FIFO的初始化。

(3)PCB设计

在PCB的设计中,应使差分线对内的长度相互匹配,以减少信号扭曲。为使设计传输速率达到2.0 Gbaud,在差分线对内部每个走线区间内的实际布线公差应控制在5 mil内。差分线对内两条线之间的距离应尽可能小,以使外部干扰为共模特征。差分线对间的距离应尽可能保持一致,以降低差分阻抗分布的不连续性。采用电源层作为差分线的信号回路,因为电源平面有最小的传输阻抗,从而减少噪声,由于每个过孔可带来0.5-1.0dB的损耗,应尽量减少过孔数目。过孔的通孔和焊盘应有尽量小的物理尺寸,并且在通孔穿越的未连接不加焊盘,差分对内的过孔不仅在数量上要匹配,而且在放置的位置上也要接近,以使阻抗分布尽量一致,避免导致阻抗不连续的90°走线,而要用圆弧或45°折线来代替。走线时应使向左、向右折角的数量接近,这样可减少信号经差分线传输引起的扭曲。在模拟数字混合系统设计中,首先,应在电源和地线之间加上去耦电容;其次,尽量加宽电源和地线宽度,最好是地线比电源线宽,使得地线宽度>电源线宽度>信号线宽度;第三,使用统一地,而将PCB分区为模拟部分和数字部分,模拟信号在电路板所有层的模拟区内布线,而数字信号在数字电路区内布线,在这种情况下,数字信号返回电流不会流入到模拟信号的地。经过以上设计,噪声影响明显降低。

4 接口解决方案

随着高速数据传输业务需求的增加,如何高质量地解决高速IC芯片的相互连接变得越来越重要,低功耗及高的信噪比是有待解决的主要问题。本文所介绍的高速采集系统中芯片间有两种接口:PECL和LVDS,如何进行两接口相互连接就成为一个影响系统性能的关键因素,LVDS的输入与输出都是内匹配的,所以LVDS间的连接可采用图4所示的直接连接,在FPGA内,需对差分输入时钟缓冲器(IBUFDS),差分输入的全局时钟缓冲区(IBUFGDS)和差分输出时钟缓冲器(OBUFDS)例化,在本项目的应用中,发送及接收FIFO的设计用了双口块内存(Block RAM),时钟倍频器用了延迟锁定环(DLL),帧解码器由30位并行数据产生器、同步字检测阵列和接收状态机组成。

FPGA的部分代码如下:

PECL间的连接一般常用直流耦合。在直流耦合情况下,PECL输出设计驱动50Ω负载至(VCC-2V),电路如图5所示。

FPGA的部分代码如下:

经实际测试,输入输出指标均符号系统要求,在硬件电路设计中,由于LVDS信号的偏置电压为1.25V,电压摆幅只有350mV,传输速率≥100Mb/s;因此,电路板制作至关重要,要求至少使用四层板。为使干扰信号以共模方式加到差分线对上(不影响数据正确性),要求差分线对间的距离尽可能小。电源方面,FPGA芯片上电时要求有大于500mA的驱动电流,同时,由于多个输出引脚的电位速度变化,要求每对电源和地引脚都要良好旁路。

电子 电路 FPGA PCB 电流 Maxim 电压 电阻 Xilinx 收发器 解码器 半导体 电容 总线 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)