CPLD器件的在系统动态配置

时间:08-31

来源:互联网

点击:

2 方案设计

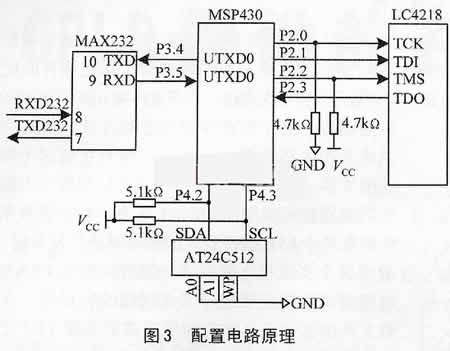

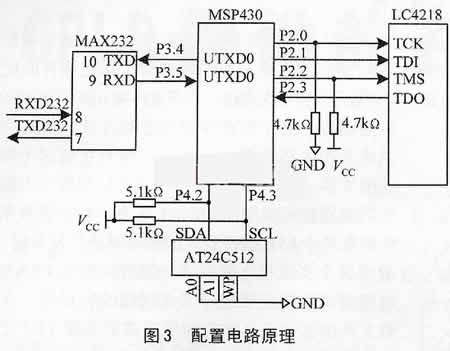

系统硬件电路如图3所示。

MSP430单片机P2口作为配置接口,接到Lattice MACH4128V的JTAG口上,外挂一个E2PROM,用来存储HEX格式的VME文件。整个过程是,通过串口接收来自计算机的配置文件,放到E2PROM,接收完毕以后,单片机运行配置引擎,读取E2PROM,配置指令通过JTAG口对Lattice MACH 4128V进行配置。需要指出的是,Lattice MACH 4128V并没有用专门的引脚来控制进入配置模式或退出配置模式,而仅仅是通过TAP控制所处状态来决定的。IEEE1149.1标准中规定:器件加电时或应用中不利用边界扫描逻辑,强迫TAP控制器处于Test-Logic-Reset状态,因此在通过程序控制JTAG进行器件配置结束时,一定要通过软件方式强迫TAP控制器回到Test-Logic-Reset状态,下面提到的ispVMEnd()函数实现的就是这个功能。另外,当通过JTAG口完成器件配置或测试以后,TMS、TDI引脚器件内部上拉。虽然如此,为了防止TCK可能出现的信号使JTAG状态机离开Test-Logic-Reset状态,或者因为上电瞬间可能产生的TCK信号导致状态机进入未知状态,设计电路时必须在TMS引脚加4.7kΩ下拉电阻。另外,电路中Vcc=3.3V。

3 软件介绍

软件部分包括PC机程序和MSP430单片机程序。其中PC机程序将HEX格式的VME文件通过串口传送给单片机;MSP430单片机程序包括ispVM EMBEDDED,串口读写和E2PROM读写部分。

作为整个配置的核心,ispVM EMBEDDED主要由存储在E2PROM的VME文件驱动,从而将配置信息串行移入Lattice MACH 4128中。整个过程如下:首先,验证VME文件的版本,只有相应版本的ispVM EMBEDDED才能解释同样版本的VME文件,ispVMStart()函数强迫TAP状态机进入配置主引擎ispVMCode(),来自于VFME中的控制代码将驱动这个引擎执行相应操作,其中3个控制代码最为常见的STATE、SIR、SDR和STATE代码控制TAP状态机进入声明的状态,如Shift-DR、Shift-IR等。SIR代码表明将向器件中移入指令流,SDR代码表明将向器件中移入数据流。通过这种方式,配置主引擎ispVMCode()将VME中包含的配置信号器件从而完成配置,配置完成ispVMCode()返回一个配置成功与否的代码。最后ispVMEnd()强迫TAP状态机进入Test-Logic-Reset状态。

Void ispVMEnd(void){

IspVMStateMachine(RESET);/*TAP状态机进入Test-Logic-Reset状态*/

IspVMDelay(1);/*一段延时后,器件由配置模式切换到运行模式*/

}

事实上,作为专门针对嵌入式平台的配置工具ispVM EMBEDDED并不依赖于特定的硬件或系统平台,所以可以很容易地往用户自己的系统上移植。3个与硬件相关的函数需要用户自己改写,Readprot()从输入引脚读一个字节,Writeport()通过输出引脚向外发送一个字节,ispVMDelay()系统延时。在MSP430上的实现如下:

#define pinTDI 0x02 //定义P2.1为TDI

#define pinTDO 0x08 //定义P2.3为TDO

short int isp_pins用来存放当前JTAG口的引脚信号

unsigned char readPort(void){

unsigned char PortVal;

PortVal="P2IN"; //读取P2口

return ((unsigned char)(PortVal &pinTDO)?0x01:0x00));//返回TDO引脚信号

}

void writePort(unsigned char pins,unsigned char value){

if(value)

isp_pins=pins|isp_pins;//把isp-pins引脚置高

else

isp_pins=~pins&isp_pins;//把isp-pins引脚置低

P2OUT=isp_pins;

}

void ispVMDeay(unsigned short int delay_time){//delay_time来自于配置文件,通过它告诉配置引擎具体需要延时多久

if(delay_time &0xA000){//ms级延时

delay_time &=~0xA000;

}

else if(delay_time>=1000)//如果是μs级,转换成ms级延时

delay_time=delay_time/1000;

else

delay_time=1;//延时小于1ms时,就延时1ms

PS1ms=delay_time;

CCTL0=CCIE; //开定时

while(PS1ms){};//在中断PS1ms

CCTL0&=~CCIE; //关定时

}

有一点需要指出,ispVM EMBEDDED要求将已转化成HEX格式的VME作为程序的一部分固化在单片机里。很显然,要想更换配置文件,就必须连同单片机程序一同换掉。这对实现动态配置是不利的,也是为什么在本方案中外加E2PROM的原因。这样无须更改程序,只换掉E2PRO中的配置文件即可。因此还需要更改GetByte()函数。

对24C512的操作应该遵循I2C总线协议,而在MSP430中没有I2C总线硬件,所以本方案中用软件方法模拟。由于I2C串行总线数据交换速度较慢,因而当从E2PROM中读出数据再往CPLD中移入时,形成了配置过程的速度瓶颈。在解决这个问题时,我们充分利用了MSP430149单片机内部2KB RAM,采用E2PROM最快的读取方式——顺序读,将配置数据预先读入到RAM中,GetByte()函数直接从RAM中读取数据。这种方法在一定程度上提高了配置速度。我们改写的GetByte()函数是这样的:

unsigned char GetByte()

{ unsigned char data;

static unsigned short int index="0";

……

if(index==0){ //有新的数据来自E2PROM

fp="wmeArray";//放在unsigned char vmeArray[1024]

}

data=*fp++;

if(index<1024)

index++;

else {

index="0";

if((num+1024)>totalnum是已经读取字节数)

ReadBlock(address,totalnum-num);//totalnum是整个配置文件字节数

}

else{

ReadBlock(address,1024);//从I2PROM的

address="adress"+1024;//adress地址开始读1024字节

}

}

return(data);

}

PC机上应用程序用Delphi7.0开发设计,利用专门的串口控件很容易开发出串口通信程序,从而将VME配置文件发送到MSP430。当配置完成以后由MSP430返回“配置成功”。

系统硬件电路如图3所示。

MSP430单片机P2口作为配置接口,接到Lattice MACH4128V的JTAG口上,外挂一个E2PROM,用来存储HEX格式的VME文件。整个过程是,通过串口接收来自计算机的配置文件,放到E2PROM,接收完毕以后,单片机运行配置引擎,读取E2PROM,配置指令通过JTAG口对Lattice MACH 4128V进行配置。需要指出的是,Lattice MACH 4128V并没有用专门的引脚来控制进入配置模式或退出配置模式,而仅仅是通过TAP控制所处状态来决定的。IEEE1149.1标准中规定:器件加电时或应用中不利用边界扫描逻辑,强迫TAP控制器处于Test-Logic-Reset状态,因此在通过程序控制JTAG进行器件配置结束时,一定要通过软件方式强迫TAP控制器回到Test-Logic-Reset状态,下面提到的ispVMEnd()函数实现的就是这个功能。另外,当通过JTAG口完成器件配置或测试以后,TMS、TDI引脚器件内部上拉。虽然如此,为了防止TCK可能出现的信号使JTAG状态机离开Test-Logic-Reset状态,或者因为上电瞬间可能产生的TCK信号导致状态机进入未知状态,设计电路时必须在TMS引脚加4.7kΩ下拉电阻。另外,电路中Vcc=3.3V。

3 软件介绍

软件部分包括PC机程序和MSP430单片机程序。其中PC机程序将HEX格式的VME文件通过串口传送给单片机;MSP430单片机程序包括ispVM EMBEDDED,串口读写和E2PROM读写部分。

作为整个配置的核心,ispVM EMBEDDED主要由存储在E2PROM的VME文件驱动,从而将配置信息串行移入Lattice MACH 4128中。整个过程如下:首先,验证VME文件的版本,只有相应版本的ispVM EMBEDDED才能解释同样版本的VME文件,ispVMStart()函数强迫TAP状态机进入配置主引擎ispVMCode(),来自于VFME中的控制代码将驱动这个引擎执行相应操作,其中3个控制代码最为常见的STATE、SIR、SDR和STATE代码控制TAP状态机进入声明的状态,如Shift-DR、Shift-IR等。SIR代码表明将向器件中移入指令流,SDR代码表明将向器件中移入数据流。通过这种方式,配置主引擎ispVMCode()将VME中包含的配置信号器件从而完成配置,配置完成ispVMCode()返回一个配置成功与否的代码。最后ispVMEnd()强迫TAP状态机进入Test-Logic-Reset状态。

Void ispVMEnd(void){

IspVMStateMachine(RESET);/*TAP状态机进入Test-Logic-Reset状态*/

IspVMDelay(1);/*一段延时后,器件由配置模式切换到运行模式*/

}

事实上,作为专门针对嵌入式平台的配置工具ispVM EMBEDDED并不依赖于特定的硬件或系统平台,所以可以很容易地往用户自己的系统上移植。3个与硬件相关的函数需要用户自己改写,Readprot()从输入引脚读一个字节,Writeport()通过输出引脚向外发送一个字节,ispVMDelay()系统延时。在MSP430上的实现如下:

#define pinTDI 0x02 //定义P2.1为TDI

#define pinTDO 0x08 //定义P2.3为TDO

short int isp_pins用来存放当前JTAG口的引脚信号

unsigned char readPort(void){

unsigned char PortVal;

PortVal="P2IN"; //读取P2口

return ((unsigned char)(PortVal &pinTDO)?0x01:0x00));//返回TDO引脚信号

}

void writePort(unsigned char pins,unsigned char value){

if(value)

isp_pins=pins|isp_pins;//把isp-pins引脚置高

else

isp_pins=~pins&isp_pins;//把isp-pins引脚置低

P2OUT=isp_pins;

}

void ispVMDeay(unsigned short int delay_time){//delay_time来自于配置文件,通过它告诉配置引擎具体需要延时多久

if(delay_time &0xA000){//ms级延时

delay_time &=~0xA000;

}

else if(delay_time>=1000)//如果是μs级,转换成ms级延时

delay_time=delay_time/1000;

else

delay_time=1;//延时小于1ms时,就延时1ms

PS1ms=delay_time;

CCTL0=CCIE; //开定时

while(PS1ms){};//在中断PS1ms

CCTL0&=~CCIE; //关定时

}

有一点需要指出,ispVM EMBEDDED要求将已转化成HEX格式的VME作为程序的一部分固化在单片机里。很显然,要想更换配置文件,就必须连同单片机程序一同换掉。这对实现动态配置是不利的,也是为什么在本方案中外加E2PROM的原因。这样无须更改程序,只换掉E2PRO中的配置文件即可。因此还需要更改GetByte()函数。

对24C512的操作应该遵循I2C总线协议,而在MSP430中没有I2C总线硬件,所以本方案中用软件方法模拟。由于I2C串行总线数据交换速度较慢,因而当从E2PROM中读出数据再往CPLD中移入时,形成了配置过程的速度瓶颈。在解决这个问题时,我们充分利用了MSP430149单片机内部2KB RAM,采用E2PROM最快的读取方式——顺序读,将配置数据预先读入到RAM中,GetByte()函数直接从RAM中读取数据。这种方法在一定程度上提高了配置速度。我们改写的GetByte()函数是这样的:

unsigned char GetByte()

{ unsigned char data;

static unsigned short int index="0";

……

if(index==0){ //有新的数据来自E2PROM

fp="wmeArray";//放在unsigned char vmeArray[1024]

}

data=*fp++;

if(index<1024)

index++;

else {

index="0";

if((num+1024)>totalnum是已经读取字节数)

ReadBlock(address,totalnum-num);//totalnum是整个配置文件字节数

}

else{

ReadBlock(address,1024);//从I2PROM的

address="adress"+1024;//adress地址开始读1024字节

}

}

return(data);

}

PC机上应用程序用Delphi7.0开发设计,利用专门的串口控件很容易开发出串口通信程序,从而将VME配置文件发送到MSP430。当配置完成以后由MSP430返回“配置成功”。

嵌入式 电路 CPLD 电流 仿真 MSP430 单片机 电阻 总线 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)