采用FPGA的可编程电压源系统原理及设计

时间:08-19

来源:互联网

点击:

可编程电源指某些功能或参数可以通过计算机软件编程进行控制的电源。可编程电源的实现方法有很多种。其中,现场可编程门阵列(Field ProgrammableGate Array,FPGA)具有性能好,规模大,可重复编程,开发投资小等优点。随着微电子技术的发展,FPGA的成本不断下降,正逐渐成为各种电子产品不可或缺的重要部件。由于FPGA有着如此众多的优点,因此系统采用FPGA作为控制芯片,实现可编程电压源系统,为需要可调电压源的电子产品提供高精度、高可靠性的电压。

1 系统设计

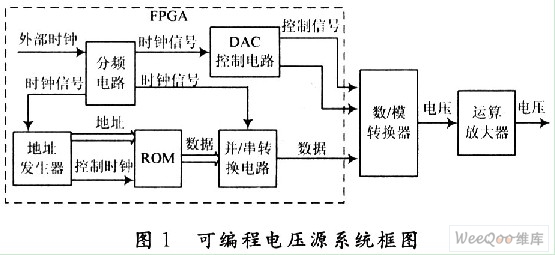

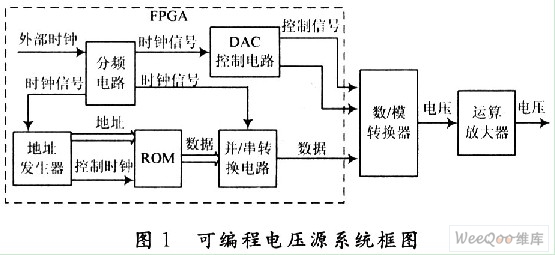

采用Altera公司Cyclone系列EP1C6Q240C8为控制芯片。通过Altera的IP工具MegaWizard管理器定制LPM_ROM宏功能模块,用.mif格式文件存放产生电压的数据;利用硬件描述语言(HDL)设计分频电路、地址发生器或数据计数器等控制电路。地址发生器对ROM进行数据读取。ROM中各单元的数据经串/并转换电路,在DAC控制电路的作用下,串行数据从高位到低位读入数/模转换器中,数/模转换器出来的模拟电压信号经过运算放大器放大后,得到所需的模拟电压。系统框图如图1所示。

根据项目需求,定制10 b×32 Word的LPM_ROM。可以产生32路1 024阶可调的电压。此外,可以根据需要定制不同的位宽,不同单元数的LPM_ROM宏功能模块,可以产生符合精度要求的多通道电压。

2 控制电路设计

2.1 分频电路模块

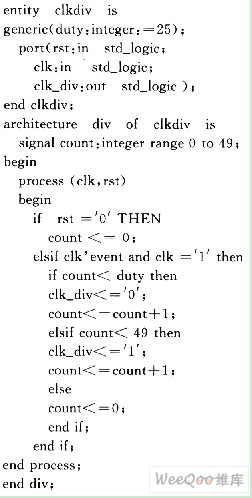

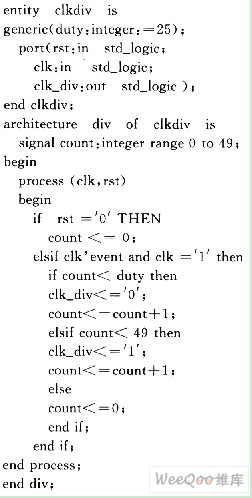

开发板提供的系统时钟为50 MHz,系统的时钟信号通过分频模块进行分频,将分频后的时钟信号分别提供给控制电路模块、地址发生器和并/串转换电路作为时钟控制信号。该模块部分VHDL源程序如下:

程序中,duty为控制占空比的参数;count为控制分频的参数。通过改变duty和count两个参数,得到占空比及分频数可调的时钟信号,极为方便。

2.2 其他模块的实现

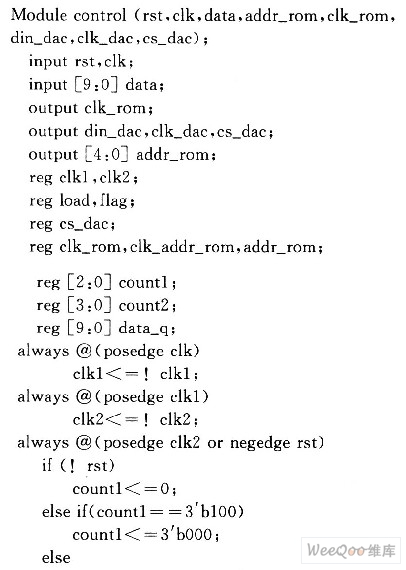

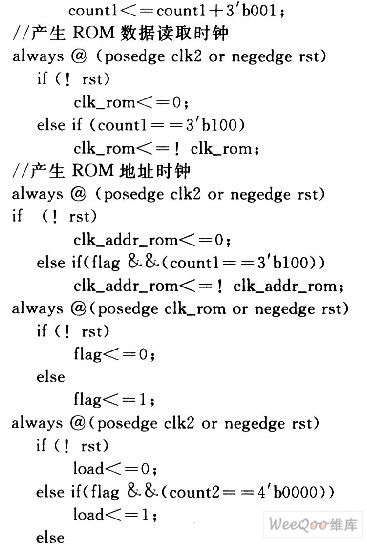

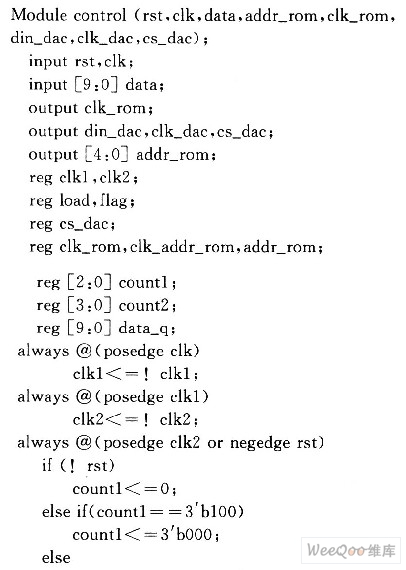

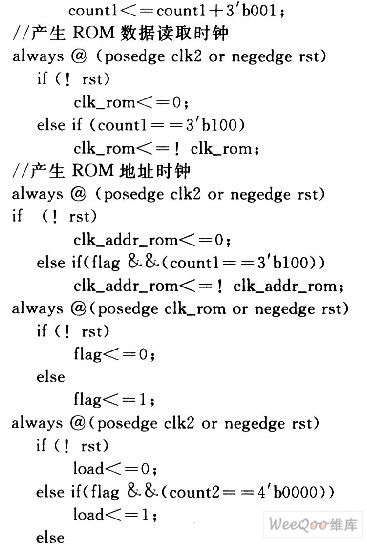

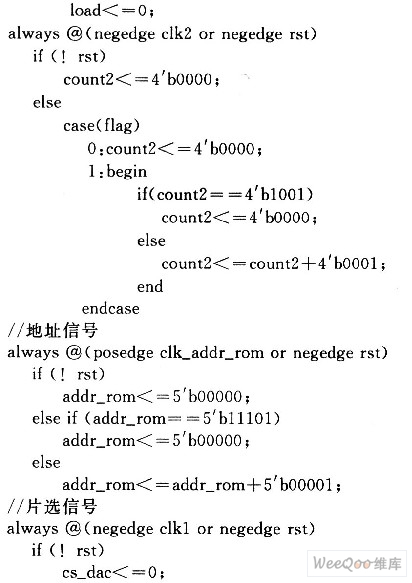

其他控制模块包括地址发生器、DAC控制电路、并/串转换电路。存储数据中只读存储器ROM是通过QuartusII软件中Mega Wizard Plug-In Manager命令定制元件的。地址发生器产生地址信号addr_tom和读使能信号clk_rom,对ROM中的数据进行读取。读取到的数据data为并行数据,由于采用的是串行数据输入的数/摸转换器,所以要进行并/串转换。data并行数据在load使能信号的作用下,赋植给寄存器data_q,经并/串转换电路对data_q进行从高位到低位的并/串转换。在DAC控制电路产生读数据信号clk_dac和片选信号cs_dac的作用下,转换电路的输出信号从高位到低位串行读入数/模转换器DAC中。完整程序如下:

2.3 程序仿真

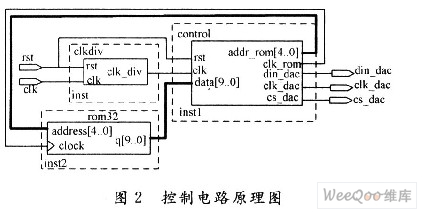

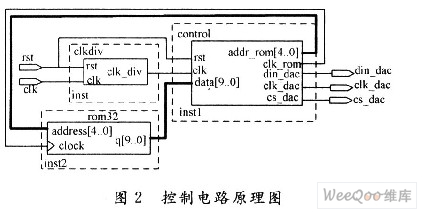

在QuartusⅡ软件中,用原理图的方式把上面两个程序例化成工程。图2为例化后的结果。

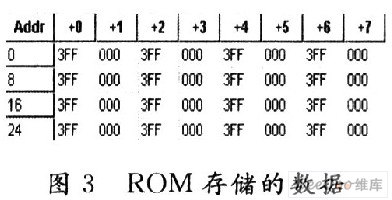

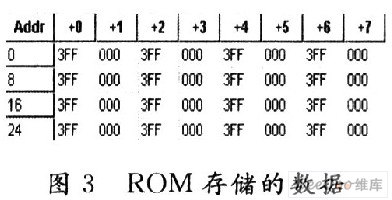

ROM中的数据采用.mif格式进行存储。ROM中存储的数据如图3所示。

对工程进行全编译,用启动仿真器对工程进行功能仿真。仿真结果如图4所示。从仿真结果可以看出,din_dac输出的数据与ROM内写入的数据完全一致。clk_dac和cs_dac:也完全满足数/模转换器所需的控制信号。

3 数/模转换器和运算放大器的设计

采用TI公司的TLC5615和OPA551分别作为数/模转换器和运算放大器。TLC5615是10位电压输出型数/模转换器,其转换输出如式(1)所示。

从式(1)可看出,数/模转换输出由参考电压VREFIN和输入数据Code决定,输出精度达到1/1 024,因此可以达到很高的调压精度。

两款元器件均采用DIP封装形式,可以即插即用,加上价格不高,特别适合用来实验。数/模转换器和运算放大器的硬件连接原理图如图5所示。OPA采用同相输入,放大后的输出电压值为:

通过改变R3和R2的值,在输入不变的条件下便可改变输出电压。

4 实验结果

取Vref=2.16 V,R1=2.5 kΩ,R2=3 kΩ,R3=15 kΩ,V+=30 V。V_=-30 V,ROM中的数据如图6所示。

实验只用到ROM的30个单元数据,即只产生30路可编程电压。把.sof文件加载到FPGA中。实验结果在示波器显示如图7所示。

图7中上边曲线为放大后的电压,下面曲线为数/模转换输出的电压。根据式(1)算出数/模转换器的输出电压最大值Vmax=4.315 V.测得值为4.32 V。根据式(2)算出Vmax=25.89 V,测得值为26.0 V。图7中各阶输出电压均与图6中数据相对应。实际测试结果与理论计算相吻合。实验表明,系统的精度高,稳定性强。

5 结 语

利用FPGA可以方便定制IP核,可重复编程,可在线调试的诸多优点,在改变ROM的地址单元数及各单元数据以及改变分频模块的参数,极其方便地产生所需的可编程多路电压。通过实验表明,系统产生的电压稳定,精度高,可调范围大(0-26V),适合为电子元件或者对多像素的元件提电源。此外,本文给出了完整的程序代码、原理图参数,具有一定的工程参考价值。

1 系统设计

采用Altera公司Cyclone系列EP1C6Q240C8为控制芯片。通过Altera的IP工具MegaWizard管理器定制LPM_ROM宏功能模块,用.mif格式文件存放产生电压的数据;利用硬件描述语言(HDL)设计分频电路、地址发生器或数据计数器等控制电路。地址发生器对ROM进行数据读取。ROM中各单元的数据经串/并转换电路,在DAC控制电路的作用下,串行数据从高位到低位读入数/模转换器中,数/模转换器出来的模拟电压信号经过运算放大器放大后,得到所需的模拟电压。系统框图如图1所示。

根据项目需求,定制10 b×32 Word的LPM_ROM。可以产生32路1 024阶可调的电压。此外,可以根据需要定制不同的位宽,不同单元数的LPM_ROM宏功能模块,可以产生符合精度要求的多通道电压。

2 控制电路设计

2.1 分频电路模块

开发板提供的系统时钟为50 MHz,系统的时钟信号通过分频模块进行分频,将分频后的时钟信号分别提供给控制电路模块、地址发生器和并/串转换电路作为时钟控制信号。该模块部分VHDL源程序如下:

程序中,duty为控制占空比的参数;count为控制分频的参数。通过改变duty和count两个参数,得到占空比及分频数可调的时钟信号,极为方便。

2.2 其他模块的实现

其他控制模块包括地址发生器、DAC控制电路、并/串转换电路。存储数据中只读存储器ROM是通过QuartusII软件中Mega Wizard Plug-In Manager命令定制元件的。地址发生器产生地址信号addr_tom和读使能信号clk_rom,对ROM中的数据进行读取。读取到的数据data为并行数据,由于采用的是串行数据输入的数/摸转换器,所以要进行并/串转换。data并行数据在load使能信号的作用下,赋植给寄存器data_q,经并/串转换电路对data_q进行从高位到低位的并/串转换。在DAC控制电路产生读数据信号clk_dac和片选信号cs_dac的作用下,转换电路的输出信号从高位到低位串行读入数/模转换器DAC中。完整程序如下:

2.3 程序仿真

在QuartusⅡ软件中,用原理图的方式把上面两个程序例化成工程。图2为例化后的结果。

ROM中的数据采用.mif格式进行存储。ROM中存储的数据如图3所示。

对工程进行全编译,用启动仿真器对工程进行功能仿真。仿真结果如图4所示。从仿真结果可以看出,din_dac输出的数据与ROM内写入的数据完全一致。clk_dac和cs_dac:也完全满足数/模转换器所需的控制信号。

3 数/模转换器和运算放大器的设计

采用TI公司的TLC5615和OPA551分别作为数/模转换器和运算放大器。TLC5615是10位电压输出型数/模转换器,其转换输出如式(1)所示。

从式(1)可看出,数/模转换输出由参考电压VREFIN和输入数据Code决定,输出精度达到1/1 024,因此可以达到很高的调压精度。

两款元器件均采用DIP封装形式,可以即插即用,加上价格不高,特别适合用来实验。数/模转换器和运算放大器的硬件连接原理图如图5所示。OPA采用同相输入,放大后的输出电压值为:

通过改变R3和R2的值,在输入不变的条件下便可改变输出电压。

4 实验结果

取Vref=2.16 V,R1=2.5 kΩ,R2=3 kΩ,R3=15 kΩ,V+=30 V。V_=-30 V,ROM中的数据如图6所示。

实验只用到ROM的30个单元数据,即只产生30路可编程电压。把.sof文件加载到FPGA中。实验结果在示波器显示如图7所示。

图7中上边曲线为放大后的电压,下面曲线为数/模转换输出的电压。根据式(1)算出数/模转换器的输出电压最大值Vmax=4.315 V.测得值为4.32 V。根据式(2)算出Vmax=25.89 V,测得值为26.0 V。图7中各阶输出电压均与图6中数据相对应。实际测试结果与理论计算相吻合。实验表明,系统的精度高,稳定性强。

5 结 语

利用FPGA可以方便定制IP核,可重复编程,可在线调试的诸多优点,在改变ROM的地址单元数及各单元数据以及改变分频模块的参数,极其方便地产生所需的可编程多路电压。通过实验表明,系统产生的电压稳定,精度高,可调范围大(0-26V),适合为电子元件或者对多像素的元件提电源。此外,本文给出了完整的程序代码、原理图参数,具有一定的工程参考价值。

FPGA 电子 电压 Altera 电路 DAC 放大器 VHDL Quartus 仿真 运算放大器 示波器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)