基于FPGA的时间间隔测量模块设计

时间:08-19

来源:互联网

点击:

随着半导体技术、嵌人式技术和EDA技术的不断发展,数字设计技术将逐步取代模拟技术。而FPGA技术是数字技术的最新研究成果,利用FPGA技术进行数字电路的设计是必然趋势。电子工艺技术的不断改进使得FPGA的成本不断降低,用FPGA进行数字电路的设计具有开发周期短、成本低、电路设计简单的特点。由于生产FPGA的各大厂家在工艺上不断提升技术,使得FPGA的市场迅速扩大。

1 基本设计原理

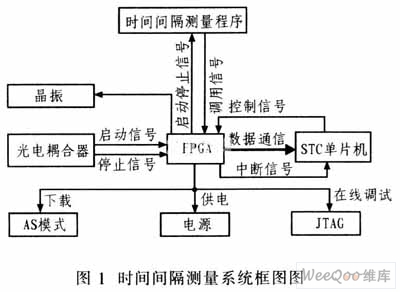

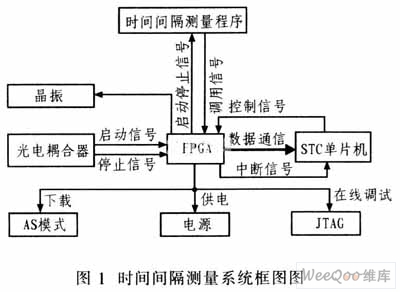

图1为时间间隔测量系统框图。

图l中,FPGA模块作为整个时间间隔测量模块的核心器件,当有启动信号时,经光电耦合器进行电平转换,得出5 V的数字信号。此时,FPGA向时间间隔测量程序发送数字信号1通知,时间间隔测量程序开始测量,当光电耦合器件再次收到信号时,此信号可以设置为停止信号,此时FPGA向时间间隔测量程序发送停止信号,得到两个信号间的间隔数据,FPGA根据经验进行分析判断测量数据是否为正确数据。若为正确测量数据,FPGA向STC单片机发送中断信息,通知STC单片机进行数据的读取。此时,STC单片机向FPGA发送控制信号,FPGA根据STC单片机发来的控制信号进行识别,根据控制信号有序地向STC单片机进行数据传输。FPGA采用A1tera公司的EPlC3T10017器件进行硬件设计,采用A1-tera公司开发的Quartus II进行软件设计。

2 系统硬件设计

系统硬件设计是整个系统的骨架,是数字电路设计的核心部件。所有程序代码都在FPGA内部运行,但是要使FPGA能够正常运作,需要架构一些基本的硬件支撑FPGA小型系统。

时间间隔测量系统的硬件设计主要包括:信号接口、电源、时钟等模块。

1)信号接口电路 信号接口电路主要用于接收外部输入信号并进行电平转换,以使协处理器得到稳定电平的信号,起到保护协处理器的作用,并起到外部电压波动的抗干扰作用。

2)电源 为使仪器直接与外部的市电220 V相接。这里外部电源采用开关电源220 V转换5 V,内部电源采用5 V转换3.3 V电源模块和5 V转换1.5 V电源。整个仪器的内部工作电压为5 V、3.3 V和1.5 V 3种电压模式。

3)时钟 时钟模块是协处理器够正常工作的保证,同时也是测量仪获取时间间隔的重要依据,本设计计数功能模块采用脉冲计数法来获取时间间隔,设计时需要考虑校准时钟,以便定期对时钟进行校准。

整个硬件电路原理设计如图2所示。

3 系统软件设计

测量模块内部需要的集成电路都是通过软件来实现,所以,先设计系统软件流程计。其软件设计包括:信号预处理、计数程序、总线控制器、锁存器等模块设计。

由于该系统软件设计的4大模块的设计过程类似,所以这里只介绍信号预处理模块的设计流程及其后面的功能实现及仿真。

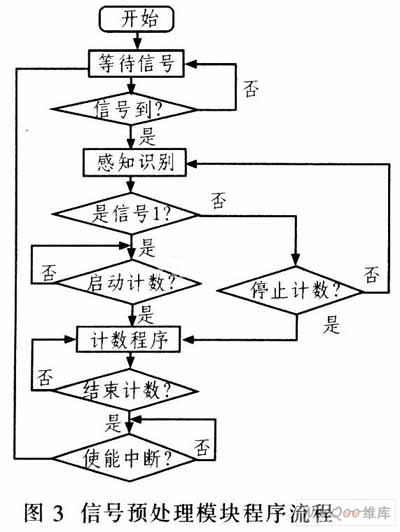

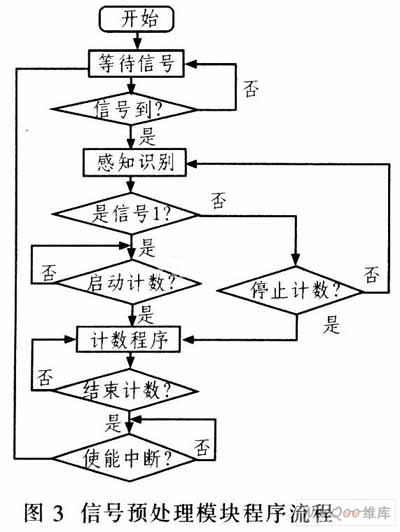

由于时间间隔测量仪在实际使用中可能会受到各种干扰,在靶场实际应用中,经常会存在蚊虫干扰,冲击波干扰,细小物体和外界光线的干扰,因此,需要在时间间隔测量仪的前端做滤波程序,但由于器件自身的特性及环境的复杂性,实际应用中信号由光电靶传输到时间间隔测量仪会存在误跳变误触发现象,这种现象会导致时间间隔测量仪的误判及误测,针对这种异常现象,时间间隔测量仪可以模拟人的视觉来接收环境信息,并由神经冲动进行信息传递,采取神经网络感知识别措施非常必要,识别程序流程如图3所示。

启动时间间隔测量仪,感觉器等待信号的到来,如果有信号,立即进行感知判断,询问是否为信号l,如果为信号1,则判断是否启动计数,若计数程序正在执行上一次信号的工作,则不启动计数器,否则启动计数器并发出中断信号,发出开始信号,即使中断置为高电平,通知主控制器准备读取数据,开始置为高电平。如果不是信号l,也就是当信号2到来时,则判断是否停止计数器,如果信号2到来前未收到信号l,则感知程序可认为此时的信号2为无用信号,直接丢弃。如果信号2到来前已收到信号l,并已在计数,但若小于预设的闸门关闭时间,则不关闭闸门,即中断保持高电平不变,停止信号保持低电平。等待计数程序(计数模块)结束发出复位信号,否则发出停止信号,即使停止置为高,计数器停止计数。若计数程序结束,则发出巾断信号,使中断置为低电平,进入下一步丁作。

4 功能实现及仿真

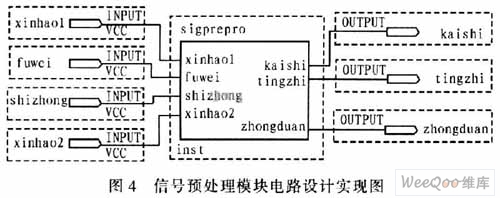

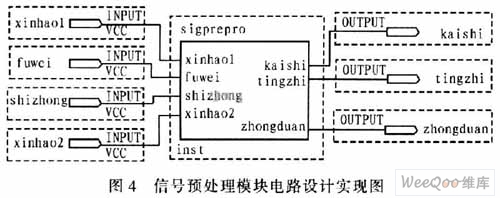

通过QuartusⅡ开发环境,文本编辑方式,用VHDL语言进行编程,生成图元,结合顶层原理图设计,实现信号预处理模块原理图,如图4所示。

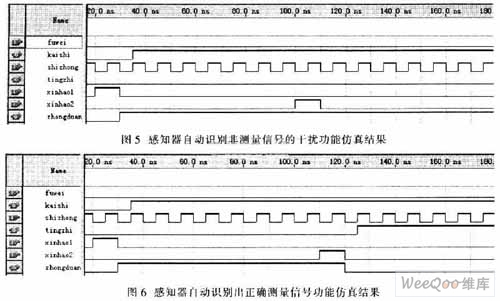

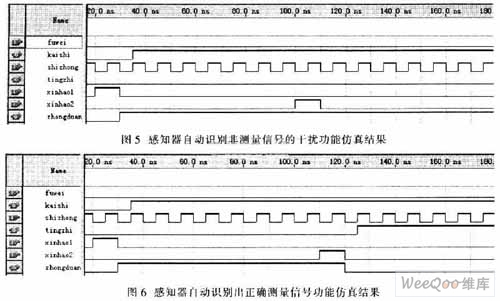

对编写的程序进行调试、编译通过,然后进行功能时序仿真,实现如果信号2到来之前已经收到信号l,并且已经在计数,但若小于预设的闸门关闭时间80 ns,则不进行闸门关闭。即中断保持高电平不变,停止信号保持低电平,感知器认为此信号为非测量信号2,继续监测信号2的到来,如图5所示。

如果信号2到来之前已经收到信号1,并且已经在计数,但若大于或是等于预设的闸门关闭时间80 ns,则进行闸门关闭,即中断由高电平跳变为低电平,停止信号由低电平跳变为高电平,感知器判断出此信号为所要测量的信号2,通知主控制器读取数据,如图6所示。

5 结论

该系统硬件设计采用Ahera公司的FPGA器件EPIC3T10017,同时软件设计采用其公司自行开发的QuartusII开发环境进行程序设计及其功能时序的仿真。实践表明,由于FPGA器件简单易学,市场占有量大,开发设计人员容易购置,开发技术易于掌握,尤其是FPGA本身功能强大,故其在工业控制领域中将占据重要的位置。这里所介绍的时间间隔测量技术可在靶场测试、激光测距、物理实验、航空航天等领域发挥良好的作用。(西安工业大学 作者:张敏光,刘群华,赵新林,韩峰)

1 基本设计原理

图1为时间间隔测量系统框图。

图l中,FPGA模块作为整个时间间隔测量模块的核心器件,当有启动信号时,经光电耦合器进行电平转换,得出5 V的数字信号。此时,FPGA向时间间隔测量程序发送数字信号1通知,时间间隔测量程序开始测量,当光电耦合器件再次收到信号时,此信号可以设置为停止信号,此时FPGA向时间间隔测量程序发送停止信号,得到两个信号间的间隔数据,FPGA根据经验进行分析判断测量数据是否为正确数据。若为正确测量数据,FPGA向STC单片机发送中断信息,通知STC单片机进行数据的读取。此时,STC单片机向FPGA发送控制信号,FPGA根据STC单片机发来的控制信号进行识别,根据控制信号有序地向STC单片机进行数据传输。FPGA采用A1tera公司的EPlC3T10017器件进行硬件设计,采用A1-tera公司开发的Quartus II进行软件设计。

2 系统硬件设计

系统硬件设计是整个系统的骨架,是数字电路设计的核心部件。所有程序代码都在FPGA内部运行,但是要使FPGA能够正常运作,需要架构一些基本的硬件支撑FPGA小型系统。

时间间隔测量系统的硬件设计主要包括:信号接口、电源、时钟等模块。

1)信号接口电路 信号接口电路主要用于接收外部输入信号并进行电平转换,以使协处理器得到稳定电平的信号,起到保护协处理器的作用,并起到外部电压波动的抗干扰作用。

2)电源 为使仪器直接与外部的市电220 V相接。这里外部电源采用开关电源220 V转换5 V,内部电源采用5 V转换3.3 V电源模块和5 V转换1.5 V电源。整个仪器的内部工作电压为5 V、3.3 V和1.5 V 3种电压模式。

3)时钟 时钟模块是协处理器够正常工作的保证,同时也是测量仪获取时间间隔的重要依据,本设计计数功能模块采用脉冲计数法来获取时间间隔,设计时需要考虑校准时钟,以便定期对时钟进行校准。

整个硬件电路原理设计如图2所示。

3 系统软件设计

测量模块内部需要的集成电路都是通过软件来实现,所以,先设计系统软件流程计。其软件设计包括:信号预处理、计数程序、总线控制器、锁存器等模块设计。

由于该系统软件设计的4大模块的设计过程类似,所以这里只介绍信号预处理模块的设计流程及其后面的功能实现及仿真。

由于时间间隔测量仪在实际使用中可能会受到各种干扰,在靶场实际应用中,经常会存在蚊虫干扰,冲击波干扰,细小物体和外界光线的干扰,因此,需要在时间间隔测量仪的前端做滤波程序,但由于器件自身的特性及环境的复杂性,实际应用中信号由光电靶传输到时间间隔测量仪会存在误跳变误触发现象,这种现象会导致时间间隔测量仪的误判及误测,针对这种异常现象,时间间隔测量仪可以模拟人的视觉来接收环境信息,并由神经冲动进行信息传递,采取神经网络感知识别措施非常必要,识别程序流程如图3所示。

启动时间间隔测量仪,感觉器等待信号的到来,如果有信号,立即进行感知判断,询问是否为信号l,如果为信号1,则判断是否启动计数,若计数程序正在执行上一次信号的工作,则不启动计数器,否则启动计数器并发出中断信号,发出开始信号,即使中断置为高电平,通知主控制器准备读取数据,开始置为高电平。如果不是信号l,也就是当信号2到来时,则判断是否停止计数器,如果信号2到来前未收到信号l,则感知程序可认为此时的信号2为无用信号,直接丢弃。如果信号2到来前已收到信号l,并已在计数,但若小于预设的闸门关闭时间,则不关闭闸门,即中断保持高电平不变,停止信号保持低电平。等待计数程序(计数模块)结束发出复位信号,否则发出停止信号,即使停止置为高,计数器停止计数。若计数程序结束,则发出巾断信号,使中断置为低电平,进入下一步丁作。

4 功能实现及仿真

通过QuartusⅡ开发环境,文本编辑方式,用VHDL语言进行编程,生成图元,结合顶层原理图设计,实现信号预处理模块原理图,如图4所示。

对编写的程序进行调试、编译通过,然后进行功能时序仿真,实现如果信号2到来之前已经收到信号l,并且已经在计数,但若小于预设的闸门关闭时间80 ns,则不进行闸门关闭。即中断保持高电平不变,停止信号保持低电平,感知器认为此信号为非测量信号2,继续监测信号2的到来,如图5所示。

如果信号2到来之前已经收到信号1,并且已经在计数,但若大于或是等于预设的闸门关闭时间80 ns,则进行闸门关闭,即中断由高电平跳变为低电平,停止信号由低电平跳变为高电平,感知器判断出此信号为所要测量的信号2,通知主控制器读取数据,如图6所示。

5 结论

该系统硬件设计采用Ahera公司的FPGA器件EPIC3T10017,同时软件设计采用其公司自行开发的QuartusII开发环境进行程序设计及其功能时序的仿真。实践表明,由于FPGA器件简单易学,市场占有量大,开发设计人员容易购置,开发技术易于掌握,尤其是FPGA本身功能强大,故其在工业控制领域中将占据重要的位置。这里所介绍的时间间隔测量技术可在靶场测试、激光测距、物理实验、航空航天等领域发挥良好的作用。(西安工业大学 作者:张敏光,刘群华,赵新林,韩峰)

半导体 EDA FPGA 电路 电子 单片机 Quartus 电压 开关电源 电源模块 集成电路 总线 仿真 神经网络 VHDL PIC 相关文章:

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA 上同步开关噪声的分析(04-05)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)