基于CPLD的函数信号发生器设计

时间:08-20

来源:互联网

点击:

传统的信号源设计常采用模拟分立元件或单片压控函数发生器MAX038,可产生正弦波、方波、三角波,并通过调整外部元件改变输出频率,但由于采用模拟器件,所用元件的分散性太大,即使使用单片函数发生器,也因参数与外部元件有关(外接的电阻电容对参数影响很大),使频率稳定度较差,精度低,抗干扰能力低,成本也高;况且其灵活性较差,而不能实现多种波形以及波形运算输出等功能。

在此,采用直接数字频率合成(DDFS)技术,并使用单片机控制CPLD的方法。由于CPLD具有可编程重置特性,因而可以方便地改变控制方式或更换波形数据,而且简单易行,易于系统升级,同时具有很高的性价比。频率合成是将一个高稳定度和一个高精度的标准频率经过运算,产生同样稳定度和精度的大量离散频率技术,一定程度上解决了既要频率稳定、精确,又要频率在较大范围内可变的矛盾。

1 DDFS的原理和特点

1.1 DDFS的基本原理

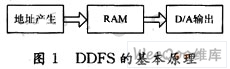

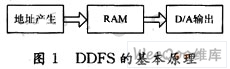

DDFS的基本原理图如图1所示。

一个完整输出波形的周期、幅值都被顺序地存放在RAM中。当RAM的地址变化时,DAC将该波形数据转换成电压波形,该电压波形的频率与RAM地址变化的速率成正比。DDFS发生器使用了相位累加技术,以控制波形在RAM中的地址。它用一个加法器代替计数器来产生RAM的顺序地址。在每一个时钟周期,存储于相位递增寄存器(Phase Increment Register,PIR)中的常数都被加到相位累加器的当前结果上。相位累加器输出的最大有效位数被用来确定波形在RAM中的地址。通过改变PIR的常数,确定每个周期中的点数,而这些点数正是用来改变整个波形的频率。当一个新相位递增寄存器的(PIR)常数被存进寄存器中,波形的输出频率便随下一个时钟周期连续地改变相位。相位累加器将依据PIR中存储的常数来改变RAM的地址,若PIR数值很小(即频率较低)时,累加器便逐步地经过每个RAM地址;当PIR的值较大时,相位累加器将跳跃某些RAM地址。

1.2 DDFS的特点

DDFS的特点如下:

(1)DDFS的频率分辨率在相位累加器的位数N足够大时,理论上可以获得相应的分辨精度,这是传统方法难以实现的。

(2)由于DDFS中不需要相位反馈控制,频率建立及频率切换快,并且与频率分辨率、频谱纯度相互独立,这一点明显优于PPL。

(3)DDFS的相位误差主要依赖于时钟的相位特性,相位误差小。另外,DDFS的相位是连续变化的,形成的信号具有良好的频谱,这是传统的直接频率合成方法无法实现的。

(4)DDFS的失真度除了受到D/A转换器本身的噪声影响外,还与离散点数N和D/A字长有着密切的关系。在高输出频率取样点数32和相应的量化级数256条件下,失真度(5.676%)已经足够小了。

2 系统设计

2.1 总体设计

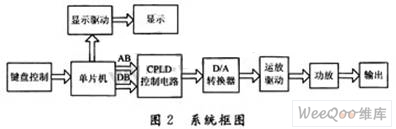

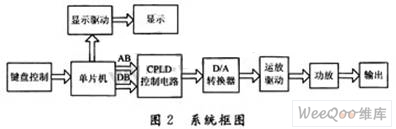

系统框图如图2所示。

2.2 主要模块设计

(1)波形产生电路模块。用CPLD产生方波、正弦波、三角波和占空比可调的矩形波,从存储器读出波形数据,把数据交给D/A转换器DAC0832进行转换得到模拟波形。在CPLD内部采用层次化设计方法产生波形,底层采用硬件描述语言描述波形。

(2)键盘控制模块。用单片机80C196接8255芯片控制4×5键盘,8255得到键盘码,通过中断服务程序把键盘信息送给单片机。

(3)LED显示模块。用8个LED数码管显示占空比和频率值,接口电路简单,控制方便。LED数码管的质量轻,体积小,功耗低,接口简单方便可与8位微处理器或控制器相连。

(4)单片机控制模块。是系统的主控制器,用于控制其他模块协调工作。该系统程序的代码比较长,约几十KB,使用80C196单片机,片内有ROM,不必扩展外部ROM。

该程序需要较大的RAM,以便进行波形存储、失真度分析等操作。

2.3 参数计算

频率参数计算如下:

波形频率范围为20 Hz~20 kHz;步进为10 Hz。因为根据公式:fout=Nfclk/2M,△f=fclk/2M=10 Hz,因此选取的时钟频率必须为2 MHz。另外要保证20 kHz以上时,取样点数都是64点,这样时钟频率必须大于10 MHz。该系统的时钟频率采用80 MHz。综合考虑,相位累加器的时钟频率fx根据公式fx=fclk/(2Nfout)选取,相位累加器位数为16位,频率步进为fs=fx/216=10。相位增量寄存器为16位,故最高输出频率为20 kHz。

D/A转换器的转换时间为1μs,可以保证在输出频率为1 MHz时,输出64个样点。用单片机输出控制信号与数据,CPLD芯片作为系统实现。

2.4 幅度控制

D/A转换器是实现幅度可调和任意输出的关键,以此来控制信号发生器的输出电压。D/A转换器中电流的建立时间将直接影响到输出的最高频率。该系统采用的是DAC0832,电流建立时间为1μs,在最高频率点,一个周期输出64个点,可输出20 Hz~20 kHz的频率信号。幅度控制用8位D/A控制,最高峰值为12.7 V,因此幅度分辨率为0.1 V。

2.5 滤波、缓冲输出电路

D/A转换器输出后,正弦波通过滤波电路、输出缓冲电路对信号去毛刺,使信号平滑且具有负载能力。运放选用高速宽带运放TL084,截止频率约为1 MHz,20 kHz以内幅度平坦。

为了保证稳幅输出,选用OCL功放电路,得到的频率特性好,波形失真小,具有很强大的电流驱动能力。实际电路测量结果表明,当负载为100 Ω,输出电压峰值为12 V时,带宽大于20 kHz,幅度变化小于±1/100。

3 调 试

调试过程分三大部分:硬件调试、软件调试、软硬件联调。电路按模块调试,各模块逐个调试通过后再联调。单片机软件先在最小系统板上调试,确保外部EPROM和RAM工作正常之后,再与硬件系统联调。

3.1 软件调试

该系统的软件系统很大,全部用80C196来编写,由于一般仿真器对196的支持都有一定的缺陷,调试比较复杂。除了语法差错和逻辑差错外,当确认程序没问题时,通过直接下载到单片机来调试。采取的是自上到下的调试方法,即单独调试好每一个模块,然后再连接成一个完整的系统调试。

3.2 硬件调试

(1)CPLD控制电路的调试。该系统的CPLD采用EPM7128SLC84-15。调试时,使用存储示波器显示CPLD的输出波形,以发现时序与仿真结果是否有出入,便于找出硬件电路中的故障。

(2)高频电路抗干扰设计。CPLD的时钟频率很高,对周围电路有一定影响。这里采取一些抗干扰措施,如尽量缩短引线,减少交叉,使每个芯片的电源与地之间都接有去耦电容,并将数字地与模拟地分开、敷铜等。实践证明,这些措施对消除某些引脚上的“毛刺”及高频噪声的效果很好。

(3)运算放大器的调试。由于输出频率为20 Hz~20 kHz,因此对放大器的带宽有一定要求,所以在调试滤波电路和缓冲输出电路时,都选择了高速宽带运放TL084。

3.3 软、硬联调

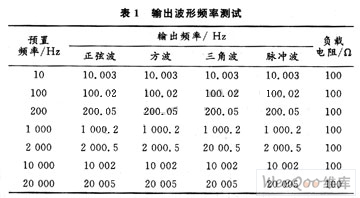

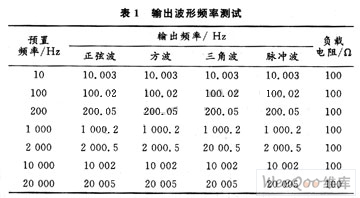

该系统软件与硬件之间的联系不是十分紧密,一般是软件计算完毕后,将数据存入ROM,CPLD读取单片机系统的数据,进行运算、逻辑分析,从而产生波形。因此在软、硬件都基本调通的情况下,系统的软、硬件联调难度不大。输出波形的频率范围测试数据如表1所示。

由表1可以看出,在频率稳定度方面,正弦波、方波、三角波在带负载的情况下均十分稳定,这正体现了DDFS技术的特点,输出频率稳定度和晶振稳定度在同一数量级。脉冲波占空比的调试如表2所示。

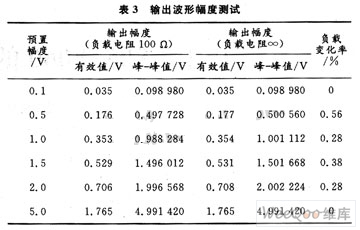

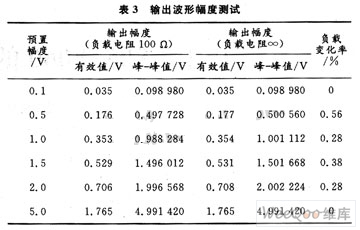

由表2可以看出,占空比可以在10%~90%范围内预置。在20 kHz正弦波条件下测得的输出波形幅度数据如表3所示。

由表3可见,电压稳定度方面,在电压的绝对值和预置值之差及带负载和不带负载的情况下,输出电压之差均小于±1/100。

4 结 语

系统采用DDFS技术和单片机控制CPLD的方法,实现了常用的正弦波、方波、三角波和占空比可调的矩形波,频率范围为20 Hz~20 kHz。利用LED显示波形的类型、频率和幅值,并具有输出电路保护功能。经实际调试,该系统的频率范围宽,步进小,幅度和频率的精度高。

在此,采用直接数字频率合成(DDFS)技术,并使用单片机控制CPLD的方法。由于CPLD具有可编程重置特性,因而可以方便地改变控制方式或更换波形数据,而且简单易行,易于系统升级,同时具有很高的性价比。频率合成是将一个高稳定度和一个高精度的标准频率经过运算,产生同样稳定度和精度的大量离散频率技术,一定程度上解决了既要频率稳定、精确,又要频率在较大范围内可变的矛盾。

1 DDFS的原理和特点

1.1 DDFS的基本原理

DDFS的基本原理图如图1所示。

一个完整输出波形的周期、幅值都被顺序地存放在RAM中。当RAM的地址变化时,DAC将该波形数据转换成电压波形,该电压波形的频率与RAM地址变化的速率成正比。DDFS发生器使用了相位累加技术,以控制波形在RAM中的地址。它用一个加法器代替计数器来产生RAM的顺序地址。在每一个时钟周期,存储于相位递增寄存器(Phase Increment Register,PIR)中的常数都被加到相位累加器的当前结果上。相位累加器输出的最大有效位数被用来确定波形在RAM中的地址。通过改变PIR的常数,确定每个周期中的点数,而这些点数正是用来改变整个波形的频率。当一个新相位递增寄存器的(PIR)常数被存进寄存器中,波形的输出频率便随下一个时钟周期连续地改变相位。相位累加器将依据PIR中存储的常数来改变RAM的地址,若PIR数值很小(即频率较低)时,累加器便逐步地经过每个RAM地址;当PIR的值较大时,相位累加器将跳跃某些RAM地址。

1.2 DDFS的特点

DDFS的特点如下:

(1)DDFS的频率分辨率在相位累加器的位数N足够大时,理论上可以获得相应的分辨精度,这是传统方法难以实现的。

(2)由于DDFS中不需要相位反馈控制,频率建立及频率切换快,并且与频率分辨率、频谱纯度相互独立,这一点明显优于PPL。

(3)DDFS的相位误差主要依赖于时钟的相位特性,相位误差小。另外,DDFS的相位是连续变化的,形成的信号具有良好的频谱,这是传统的直接频率合成方法无法实现的。

(4)DDFS的失真度除了受到D/A转换器本身的噪声影响外,还与离散点数N和D/A字长有着密切的关系。在高输出频率取样点数32和相应的量化级数256条件下,失真度(5.676%)已经足够小了。

2 系统设计

2.1 总体设计

系统框图如图2所示。

2.2 主要模块设计

(1)波形产生电路模块。用CPLD产生方波、正弦波、三角波和占空比可调的矩形波,从存储器读出波形数据,把数据交给D/A转换器DAC0832进行转换得到模拟波形。在CPLD内部采用层次化设计方法产生波形,底层采用硬件描述语言描述波形。

(2)键盘控制模块。用单片机80C196接8255芯片控制4×5键盘,8255得到键盘码,通过中断服务程序把键盘信息送给单片机。

(3)LED显示模块。用8个LED数码管显示占空比和频率值,接口电路简单,控制方便。LED数码管的质量轻,体积小,功耗低,接口简单方便可与8位微处理器或控制器相连。

(4)单片机控制模块。是系统的主控制器,用于控制其他模块协调工作。该系统程序的代码比较长,约几十KB,使用80C196单片机,片内有ROM,不必扩展外部ROM。

该程序需要较大的RAM,以便进行波形存储、失真度分析等操作。

2.3 参数计算

频率参数计算如下:

波形频率范围为20 Hz~20 kHz;步进为10 Hz。因为根据公式:fout=Nfclk/2M,△f=fclk/2M=10 Hz,因此选取的时钟频率必须为2 MHz。另外要保证20 kHz以上时,取样点数都是64点,这样时钟频率必须大于10 MHz。该系统的时钟频率采用80 MHz。综合考虑,相位累加器的时钟频率fx根据公式fx=fclk/(2Nfout)选取,相位累加器位数为16位,频率步进为fs=fx/216=10。相位增量寄存器为16位,故最高输出频率为20 kHz。

D/A转换器的转换时间为1μs,可以保证在输出频率为1 MHz时,输出64个样点。用单片机输出控制信号与数据,CPLD芯片作为系统实现。

2.4 幅度控制

D/A转换器是实现幅度可调和任意输出的关键,以此来控制信号发生器的输出电压。D/A转换器中电流的建立时间将直接影响到输出的最高频率。该系统采用的是DAC0832,电流建立时间为1μs,在最高频率点,一个周期输出64个点,可输出20 Hz~20 kHz的频率信号。幅度控制用8位D/A控制,最高峰值为12.7 V,因此幅度分辨率为0.1 V。

2.5 滤波、缓冲输出电路

D/A转换器输出后,正弦波通过滤波电路、输出缓冲电路对信号去毛刺,使信号平滑且具有负载能力。运放选用高速宽带运放TL084,截止频率约为1 MHz,20 kHz以内幅度平坦。

为了保证稳幅输出,选用OCL功放电路,得到的频率特性好,波形失真小,具有很强大的电流驱动能力。实际电路测量结果表明,当负载为100 Ω,输出电压峰值为12 V时,带宽大于20 kHz,幅度变化小于±1/100。

3 调 试

调试过程分三大部分:硬件调试、软件调试、软硬件联调。电路按模块调试,各模块逐个调试通过后再联调。单片机软件先在最小系统板上调试,确保外部EPROM和RAM工作正常之后,再与硬件系统联调。

3.1 软件调试

该系统的软件系统很大,全部用80C196来编写,由于一般仿真器对196的支持都有一定的缺陷,调试比较复杂。除了语法差错和逻辑差错外,当确认程序没问题时,通过直接下载到单片机来调试。采取的是自上到下的调试方法,即单独调试好每一个模块,然后再连接成一个完整的系统调试。

3.2 硬件调试

(1)CPLD控制电路的调试。该系统的CPLD采用EPM7128SLC84-15。调试时,使用存储示波器显示CPLD的输出波形,以发现时序与仿真结果是否有出入,便于找出硬件电路中的故障。

(2)高频电路抗干扰设计。CPLD的时钟频率很高,对周围电路有一定影响。这里采取一些抗干扰措施,如尽量缩短引线,减少交叉,使每个芯片的电源与地之间都接有去耦电容,并将数字地与模拟地分开、敷铜等。实践证明,这些措施对消除某些引脚上的“毛刺”及高频噪声的效果很好。

(3)运算放大器的调试。由于输出频率为20 Hz~20 kHz,因此对放大器的带宽有一定要求,所以在调试滤波电路和缓冲输出电路时,都选择了高速宽带运放TL084。

3.3 软、硬联调

该系统软件与硬件之间的联系不是十分紧密,一般是软件计算完毕后,将数据存入ROM,CPLD读取单片机系统的数据,进行运算、逻辑分析,从而产生波形。因此在软、硬件都基本调通的情况下,系统的软、硬件联调难度不大。输出波形的频率范围测试数据如表1所示。

由表1可以看出,在频率稳定度方面,正弦波、方波、三角波在带负载的情况下均十分稳定,这正体现了DDFS技术的特点,输出频率稳定度和晶振稳定度在同一数量级。脉冲波占空比的调试如表2所示。

由表2可以看出,占空比可以在10%~90%范围内预置。在20 kHz正弦波条件下测得的输出波形幅度数据如表3所示。

由表3可见,电压稳定度方面,在电压的绝对值和预置值之差及带负载和不带负载的情况下,输出电压之差均小于±1/100。

4 结 语

系统采用DDFS技术和单片机控制CPLD的方法,实现了常用的正弦波、方波、三角波和占空比可调的矩形波,频率范围为20 Hz~20 kHz。利用LED显示波形的类型、频率和幅值,并具有输出电路保护功能。经实际调试,该系统的频率范围宽,步进小,幅度和频率的精度高。

电阻 电容 单片机 CPLD DAC 电压 电路 LED 信号发生器 电流 仿真 示波器 放大器 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- Altera FPGA下载配置(11-11)

- FPGA高速收发器设计原则(03-11)

- 基于CPLD的CCD信号发生器的研究(04-08)