基于CPLD/FPGA的VHDL语言电路优化设计

时间:08-19

来源:互联网

点击:

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述语言,是随着可编程逻辑器件(PLD)的发展而发展起来的。它是一种面向设计、多层次的硬件描述语言,是集行为描述、RTL描述、门级描述功能为一体的语言,并已成为描述、验证和设计数字系统中最重要的标准语言之一。由于VHDL在语法和风格上类似于高级编程语言,可读性好,描述能力强,设计方法灵活,可移植性强,因此它已成为广大EDA工程师的首选。目前,使用VHDL语言进行CPLD/FPGA设计开发,Altera和Lattice已经在开发软件方面提供了基于本公司芯片的强大开发工具。但由于VHDL设计是行为级设计,所带来的问题是设计者的设计思想与电路结构相脱节,而且其在设计思路和编程风格等方面也存在差异,这些差异会对系统综合后的电路整体性能产生重要的影响。

在VHDL语言电路优化设计当中,优化问题主要包括面积优化和速度优化。面积优化是指CPLD/FPGA的资源利用率优化,即用尽可能少的片内资源实现更多电路功能;速度优化是指设计系统满足一定的速度要求,即用更多的片内资源换取更快的处理速度,常用于视频信号采集系统和通信系统之中。面积优化和速度优化通常是一对矛盾,一般情况下,速度指标是首要的,在满足速度要求的前提下,尽可能实现面积优化。因此,本文结合在设计超声探伤数据采集卡过程中的CPLD编程经验,提出串行设计、防止不必要锁存器的产生、使用状态机简化电路描述、资源共享,利用E2PROM芯片节省片内资源等方法对VHDL电路进行优化。

1 VHDL电路优化设计的方法

优化设计是可编成逻辑设计的精华所在,如何节省所占用的面积、如何提高设计的性能是可编成逻辑设计的核心,这两点往往也成为一个设计甚至项目成败的关键因素。下面结合超声探伤数据采集卡设计过程中,并基于Altera公司的EPM7192 CPLD芯片的编程经历来论述VHDL电路的优化方法。

1.1 采用串行设计代替并行设计

串行设计是指把原来单个时钟周期内完成的并行操作的逻辑功能分割出来,提取相同的功能单元,在时间上分时复用这些功能单元,在满足系统速度要求的前提下,用多个时钟周期来完成单个时钟周期即可完成的功能。

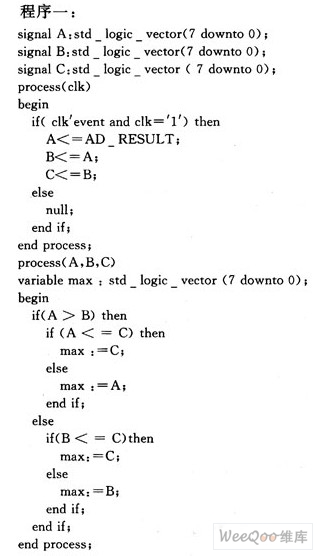

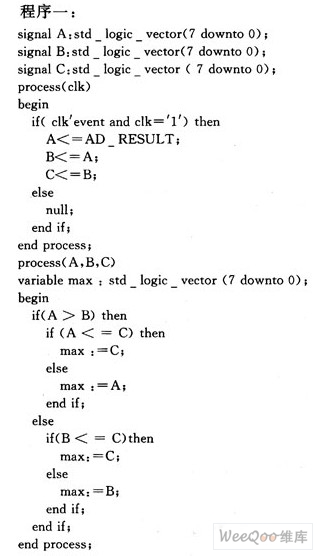

根据项目的要求,超声探伤数据采集卡要有5个模拟通道,每隔125μs就会采集到330个点。如果等5个超声通道采样结束后再进行数据处理和传输,几乎是不可能满足该超声探伤系统的实时性要求,而且数据量也远远超过ARM板上总线接口的传输速率2 MB/s。对于这么高的实时性要求,最好的解决办法是在CPLD内部进行数据压缩,即边采集边压缩,以满足系统使用的ARM板的总线速率要求。经过系统*估,每个超声通道只需保留一个最大值即可满足系统的性能要求。在这里,通过在三个8位数A,B,C中找出最大值的例子来说明串行设计方法的优势,代码如下所示。

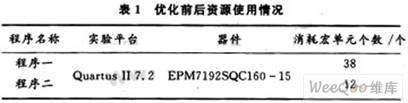

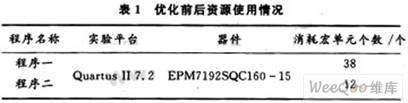

程序一是用并行方法设计,而程序二是采用串行方法设计。从表1的实验数据可见,采用串行方法以后,电路的优化效果比较明显。优化前,程序一需要消耗38个宏单元(Micro Cell),一个时钟周期即可完成找最大值操作;优化后,实现相同的逻辑功能程序二仅需要12个宏单元,但需要3个时钟周期才能完成一次运算,优化率达68.4%。值得注意的是,此方法是以速度换取资源的方法,只适用于对速度要求不高的系统。

1.2 防止不必要锁存器的产生

在VHDL设计中,使用语句不当也是导致电路复杂化的原因之一,这使得综合后的电路当中存在很多不必要的锁存器,降低电路的工作速度。因此,在设计一个逻辑电路时,设计人员应该避免由于VHDL使用习惯的问题,无意识地在电路中添加不必要的锁存器。由于IF或者CASE语句较容易引入锁存器,所以当语句的判断条件不能覆盖所有可能的输入值的时候,逻辑反馈就容易形成一个锁存器。当然,随着高级编译软件的出现,如QuartusⅡ7.2,这样的问题通过编译软件已经得到很好的解决。对一个设计人员而言,有意识地防止不必要锁存器的产生可以加快编译速度。

在超声探伤数据采集卡VHDL程序设计当中,涉及10 MHz系统时钟clk的同步D触发器的设计,即每当clk时钟信号的上升沿到来时,将输入信号in的值赋给输出信号out,代码如下所示。

通过对比,程序四比程序三只多了一条空语句,但这样做可有效防止综合器生成不必要锁存器,并提高电路的工作速度。

1.3 使用状态机简化电路描述

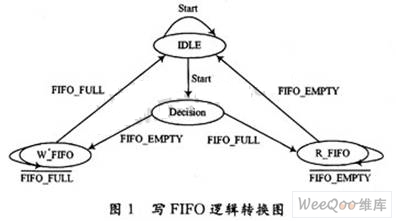

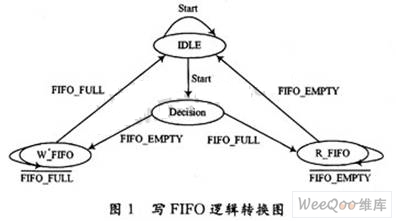

由于状态机的结构模式简单,有相对固定的设计模板,特别是VHDL支持定义符号化枚举类型状态,这就为VHDL综合器充分发挥其强大的优化功能提供了有利条件。因此采用状态机比较容易地设计出高性能的时序逻辑模块,在超声探伤数据采集卡的CPLD程序设计中,使用有限元状态机(FSM)设计CY7CA225 1K×16 b FIFO芯片的读写控制模块,并且达到很好的效果,逻辑转换图如图1所示。实践证明,实现相同的逻辑功能,使用状态机设计能使设计的电路得到更好的优化。

1.4 资源共享

资源共享的思想是通过使用数据缓冲器或多路选择器等方法来共享数据通道中占用资源较多的模块,如算法单元。通过共享电路单元模块可有效提高芯片内部资源的利用率,达到优化电路的目的。

1.5 利用E2PROM芯片节省片内资源

在用VHDL进行项目开发的过程中,经常需要存储一些配置参数值。理论上讲,每存储一个字节的配置参数需要使用8个CPLD宏单元,因此在CPLD内部存储这些参数并不是好的方案,除非使用的CPLD芯片已集成了E2PROM存储单元。例如,在设计超声探伤系统的数据采集卡的过程中,每个通道的采样数都需要保存在CPLD里面。由于项目初期芯片选型不当,选择一款EPM7192S160-15,该款芯片内部只有192个宏单元,因此考虑把参数存储在外扩的E2PROM芯片24WC02中。经实验证明,在CPLD内部实现一个I2C控制器仅需要43个宏单元。由此可见,当初始化参数大于5个的时候,通过外扩E2PROM芯片来存储配置参数是可行的,只需在CPLD/FPGA芯片内实现I2C控制器即可方便地读写E2PROM存储芯片。

2 结语

使用VHDL进行CPLD/FPGA电路设计时,要根据实际项目的具体情况,合理地划分项目功能,并用VHDL实现相应的功能模块。用模块来构建系统,可有效地优化模块间的结构和减少系统的冗余度,并在模块设计过程中始终贯彻以上的优化设计原则,借助于强大的综合开发软件进行优化,才能达到最优化电路的目的。

在VHDL语言电路优化设计当中,优化问题主要包括面积优化和速度优化。面积优化是指CPLD/FPGA的资源利用率优化,即用尽可能少的片内资源实现更多电路功能;速度优化是指设计系统满足一定的速度要求,即用更多的片内资源换取更快的处理速度,常用于视频信号采集系统和通信系统之中。面积优化和速度优化通常是一对矛盾,一般情况下,速度指标是首要的,在满足速度要求的前提下,尽可能实现面积优化。因此,本文结合在设计超声探伤数据采集卡过程中的CPLD编程经验,提出串行设计、防止不必要锁存器的产生、使用状态机简化电路描述、资源共享,利用E2PROM芯片节省片内资源等方法对VHDL电路进行优化。

1 VHDL电路优化设计的方法

优化设计是可编成逻辑设计的精华所在,如何节省所占用的面积、如何提高设计的性能是可编成逻辑设计的核心,这两点往往也成为一个设计甚至项目成败的关键因素。下面结合超声探伤数据采集卡设计过程中,并基于Altera公司的EPM7192 CPLD芯片的编程经历来论述VHDL电路的优化方法。

1.1 采用串行设计代替并行设计

串行设计是指把原来单个时钟周期内完成的并行操作的逻辑功能分割出来,提取相同的功能单元,在时间上分时复用这些功能单元,在满足系统速度要求的前提下,用多个时钟周期来完成单个时钟周期即可完成的功能。

根据项目的要求,超声探伤数据采集卡要有5个模拟通道,每隔125μs就会采集到330个点。如果等5个超声通道采样结束后再进行数据处理和传输,几乎是不可能满足该超声探伤系统的实时性要求,而且数据量也远远超过ARM板上总线接口的传输速率2 MB/s。对于这么高的实时性要求,最好的解决办法是在CPLD内部进行数据压缩,即边采集边压缩,以满足系统使用的ARM板的总线速率要求。经过系统*估,每个超声通道只需保留一个最大值即可满足系统的性能要求。在这里,通过在三个8位数A,B,C中找出最大值的例子来说明串行设计方法的优势,代码如下所示。

程序一是用并行方法设计,而程序二是采用串行方法设计。从表1的实验数据可见,采用串行方法以后,电路的优化效果比较明显。优化前,程序一需要消耗38个宏单元(Micro Cell),一个时钟周期即可完成找最大值操作;优化后,实现相同的逻辑功能程序二仅需要12个宏单元,但需要3个时钟周期才能完成一次运算,优化率达68.4%。值得注意的是,此方法是以速度换取资源的方法,只适用于对速度要求不高的系统。

1.2 防止不必要锁存器的产生

在VHDL设计中,使用语句不当也是导致电路复杂化的原因之一,这使得综合后的电路当中存在很多不必要的锁存器,降低电路的工作速度。因此,在设计一个逻辑电路时,设计人员应该避免由于VHDL使用习惯的问题,无意识地在电路中添加不必要的锁存器。由于IF或者CASE语句较容易引入锁存器,所以当语句的判断条件不能覆盖所有可能的输入值的时候,逻辑反馈就容易形成一个锁存器。当然,随着高级编译软件的出现,如QuartusⅡ7.2,这样的问题通过编译软件已经得到很好的解决。对一个设计人员而言,有意识地防止不必要锁存器的产生可以加快编译速度。

在超声探伤数据采集卡VHDL程序设计当中,涉及10 MHz系统时钟clk的同步D触发器的设计,即每当clk时钟信号的上升沿到来时,将输入信号in的值赋给输出信号out,代码如下所示。

通过对比,程序四比程序三只多了一条空语句,但这样做可有效防止综合器生成不必要锁存器,并提高电路的工作速度。

1.3 使用状态机简化电路描述

由于状态机的结构模式简单,有相对固定的设计模板,特别是VHDL支持定义符号化枚举类型状态,这就为VHDL综合器充分发挥其强大的优化功能提供了有利条件。因此采用状态机比较容易地设计出高性能的时序逻辑模块,在超声探伤数据采集卡的CPLD程序设计中,使用有限元状态机(FSM)设计CY7CA225 1K×16 b FIFO芯片的读写控制模块,并且达到很好的效果,逻辑转换图如图1所示。实践证明,实现相同的逻辑功能,使用状态机设计能使设计的电路得到更好的优化。

1.4 资源共享

资源共享的思想是通过使用数据缓冲器或多路选择器等方法来共享数据通道中占用资源较多的模块,如算法单元。通过共享电路单元模块可有效提高芯片内部资源的利用率,达到优化电路的目的。

1.5 利用E2PROM芯片节省片内资源

在用VHDL进行项目开发的过程中,经常需要存储一些配置参数值。理论上讲,每存储一个字节的配置参数需要使用8个CPLD宏单元,因此在CPLD内部存储这些参数并不是好的方案,除非使用的CPLD芯片已集成了E2PROM存储单元。例如,在设计超声探伤系统的数据采集卡的过程中,每个通道的采样数都需要保存在CPLD里面。由于项目初期芯片选型不当,选择一款EPM7192S160-15,该款芯片内部只有192个宏单元,因此考虑把参数存储在外扩的E2PROM芯片24WC02中。经实验证明,在CPLD内部实现一个I2C控制器仅需要43个宏单元。由此可见,当初始化参数大于5个的时候,通过外扩E2PROM芯片来存储配置参数是可行的,只需在CPLD/FPGA芯片内实现I2C控制器即可方便地读写E2PROM存储芯片。

2 结语

使用VHDL进行CPLD/FPGA电路设计时,要根据实际项目的具体情况,合理地划分项目功能,并用VHDL实现相应的功能模块。用模块来构建系统,可有效地优化模块间的结构和减少系统的冗余度,并在模块设计过程中始终贯彻以上的优化设计原则,借助于强大的综合开发软件进行优化,才能达到最优化电路的目的。

VHDL EDA CPLD FPGA Altera 电路 ARM 总线 Quartus 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)