基于CPLD的VGA视频显示系统的设计应用

时间:08-09

来源:互联网

点击:

显示系统在工业、农业及日常生活中扮演着越来越重要的角色,因此,对其进行设计与研究具有十分重要的意义。

CPLD(Complex Programmable Logic Device;复杂可编程逻辑器件)具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进等优点,用户可根据自身需要构造数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆将代码传送到目标芯片中,从而实现数字系统。CPLD的应用目前已深入网络、仪器仪表、汽车电子、数控机床、航天测控设备等领域,其设计及应用成为电子工程师必备的一项技能。

系统总体设计方案

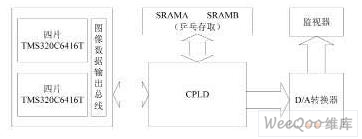

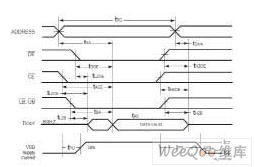

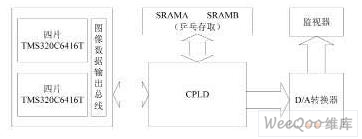

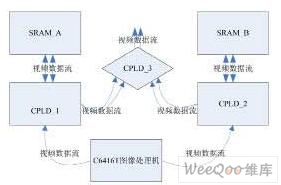

XC95144XL是XILINX公司推出的5ns引脚延迟、系统频率高达178MHz、144个宏单元、3200个可用逻辑门单元的可编程逻辑器件。本设计采用XC95144XL作为数据传输与控制核心模块,接受来自TMS320C6416T的视频数据,并采用两片IS61WV51216ALL组成缓存,以达到实时输入输出数据的效果。本部分实现框图如图1所示。

图1 视频显示功能框图

系统硬件设计

系统硬件设计主要包括:TMS320C6416T与VGA显示系统的接口设计;2片IS61WV51216ALL SRAM组成的缓存模块;视频DAC模块。

TMS320C6416T与VGA显示系统的接口设计

来自4片TMS320C6416T的图像处理机的EMIFB口连接在一起,并通过CPLD的仲裁,使能哪一块图像处理机输出数据至VGA显示系统。

采用C6416T的EMIFB口输出处理结果,当1片C6416T要求输出数据时,C6416T要通过GP01向CPLD发送输出数据请求,CPLD根据内部逻辑确定是否允许C6416T请求。内部逻辑准则如下:

各个DSP的输出数据请求优先级别相等,请求信号先到者先被允许,后到者不能中断正在响应的请求。对于同时到来的请求,CPLD响应先接收到原始视频信号的C6416T。

当CPLD响应一个C6416T的输出数据请求时,CPLD向C6416T的BHOLD#信号发送响应信号(对EMIFB的保持请求输入信号)。此时,数据开始输出。

2片IS61WV51216ALL SRAM组成的缓存模块

2片XC95144XL各自连接1片IS61WV51216ALL组成的图像缓存模块。

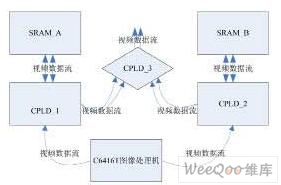

实时显示控制:由CPLD对各个6416T图像处理机数据输出接口(EMIFB)总线进行总线仲裁,实现各个6416T图像处理机的图像数据分时输出。由于VGA的刷新频率大于输入信号的频率,因此采用两片SRAM“乒乓存取”工作方式,组成了图像数据缓冲区,每片SRAM存放一帧图像,由CPLD控制其乒乓读写切换以达到实时显示效果。数据缓存电路框图如图2所示。

图2 数据缓存电路框图

采用一组SRAM作为显存,可以简化系统设计、降低成本。这时可以考虑利用行时序和帧时序中SRAM总线空闲的时序段,在不关闭图像显示的情况下实现显存SRAM的数据更新。该方法的更新率与数据写速度密切相关,显存的写数据速度越快,该方法的更新率就越高。

视频DAC模块

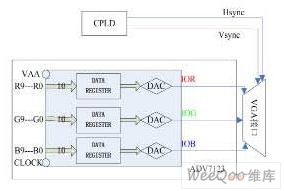

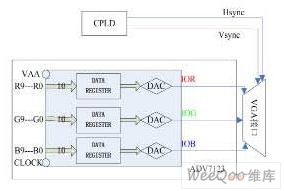

ADV7123是一个三路10位输入的高速视频DAC,具有330MHz的最大采样速度,与多种高精度的显示系统兼容,包括RS-343A和RS-170,可以广泛应用于如HDTV、数字视频系统(1600*1200 @100Hz)、高分辨率的彩色图片图像处理、视频信号再现等,因此能够满足多方面应用需求。视频DAC(ADV7123)工作原理如图3所示。

图3 ADV7123工作原理

CPLD提供Hsync(行)、Vsync(场)同步信号,直接接入15针的VGA显示接口连接器。在点时钟脉冲pixel clock的作用下将3路10位的RGB信号送入数据寄存器,而后送到3个DAC模块,复合消隐信号和复合同步信号加到红、绿、蓝模拟信号送到输出端。

系统软件设计

系统软件设计是本文的重点,主要包括三部分内容:SRAM读写状态机的设计、CPLD与SRAM的缓冲模块通信以及VGA时序设计。

SRAM读写状态机的设计

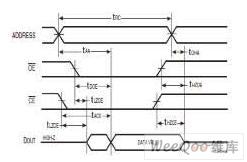

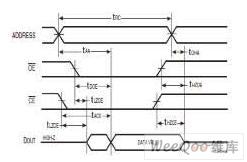

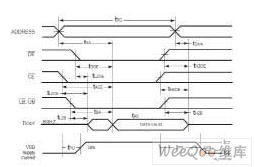

以6416为核心的图象处理机通过外部存储器接口向外传送数据,连接到后端的显示系统;但SRAM需要严格的通信时序确保数据的完整性,此处在CPLD内部通过状态机构造SRAM的读时序和写时序,确保了6416能够和SRAM正常通信,也确保缓冲模块的正常运行。读写SRAM的时序图如图4和图5所示。

图4 读周期时序图

图5 写周期时序图

当从SRAM中读取数据时:首先使能片选;UB、LB时钟处于有效状态;WE为高,时钟处于无效状态;主要由OE的时序来控制使其符合读时序图,才能正确地读出存储器中的数据。在向SRAM中写入数据时,同样首先使能片选;UB、LB时钟处于有效状态;OE为高,时钟处于无效状态;主要由WE的时序来控制使之符合写时序图,才能向存储器正确写入数据。

CPLD与SRAM组成的缓冲模块的通信

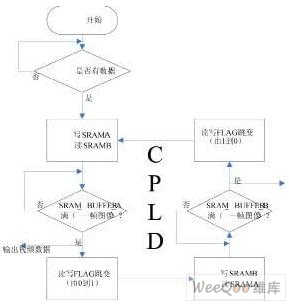

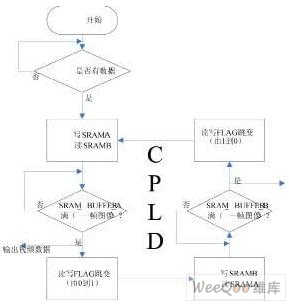

CPLD与SRAM组成的缓冲通信模块,即如何乒乓读写SRAM机制。设定一个读写标志FLAG,当一块SRAM写满一帧图像时,FLAG会出现“1”到“0”或者“0”到“1”的跳变,同时切换数据流的流向,写另一块SRAM,同时切换输出至后级DAC的数据流;如此循环,软件流程图如图6所示。

图6 缓冲模块通信软件流程图

VGA时序发生器设计

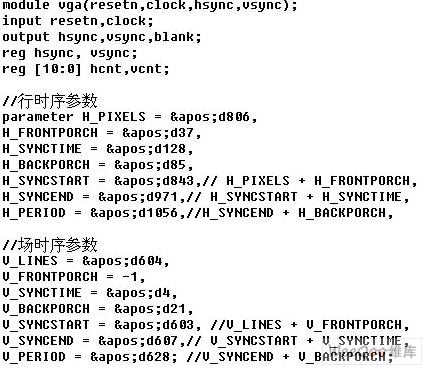

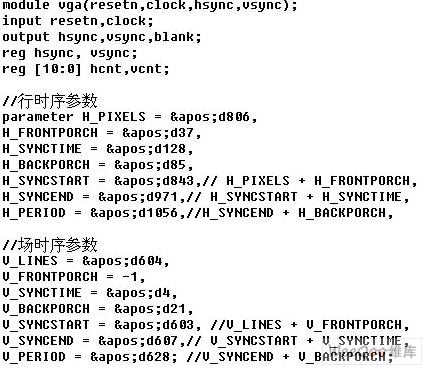

VGA标准时序参考图如图7所示,并用VERILOGHDL设计For VESA 800*600 @ 60Hz:VGA时序的源代码:

图7 VGA标准时序参考图

系统分析

经过反复测试,系统能够将采集端数据实时传送到显示器上,具体性能指标如下:

视频输出:VGA视频输出

视频显示DA转换精度: 10bit

图像输出标准: SVGA(75Hz, 800×600)

显示分辨率: 10bit

结语

该VGA视频显示系统不但可以稳定地采集图像数据,而且可以实时将数据传输到CRT显示器,便于以后人工综合分析、处理。它特别适用于大型商场等显示端,可以说是一个理想的解决方案。

CPLD(Complex Programmable Logic Device;复杂可编程逻辑器件)具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进等优点,用户可根据自身需要构造数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆将代码传送到目标芯片中,从而实现数字系统。CPLD的应用目前已深入网络、仪器仪表、汽车电子、数控机床、航天测控设备等领域,其设计及应用成为电子工程师必备的一项技能。

系统总体设计方案

XC95144XL是XILINX公司推出的5ns引脚延迟、系统频率高达178MHz、144个宏单元、3200个可用逻辑门单元的可编程逻辑器件。本设计采用XC95144XL作为数据传输与控制核心模块,接受来自TMS320C6416T的视频数据,并采用两片IS61WV51216ALL组成缓存,以达到实时输入输出数据的效果。本部分实现框图如图1所示。

图1 视频显示功能框图

系统硬件设计

系统硬件设计主要包括:TMS320C6416T与VGA显示系统的接口设计;2片IS61WV51216ALL SRAM组成的缓存模块;视频DAC模块。

TMS320C6416T与VGA显示系统的接口设计

来自4片TMS320C6416T的图像处理机的EMIFB口连接在一起,并通过CPLD的仲裁,使能哪一块图像处理机输出数据至VGA显示系统。

采用C6416T的EMIFB口输出处理结果,当1片C6416T要求输出数据时,C6416T要通过GP01向CPLD发送输出数据请求,CPLD根据内部逻辑确定是否允许C6416T请求。内部逻辑准则如下:

各个DSP的输出数据请求优先级别相等,请求信号先到者先被允许,后到者不能中断正在响应的请求。对于同时到来的请求,CPLD响应先接收到原始视频信号的C6416T。

当CPLD响应一个C6416T的输出数据请求时,CPLD向C6416T的BHOLD#信号发送响应信号(对EMIFB的保持请求输入信号)。此时,数据开始输出。

2片IS61WV51216ALL SRAM组成的缓存模块

2片XC95144XL各自连接1片IS61WV51216ALL组成的图像缓存模块。

实时显示控制:由CPLD对各个6416T图像处理机数据输出接口(EMIFB)总线进行总线仲裁,实现各个6416T图像处理机的图像数据分时输出。由于VGA的刷新频率大于输入信号的频率,因此采用两片SRAM“乒乓存取”工作方式,组成了图像数据缓冲区,每片SRAM存放一帧图像,由CPLD控制其乒乓读写切换以达到实时显示效果。数据缓存电路框图如图2所示。

图2 数据缓存电路框图

采用一组SRAM作为显存,可以简化系统设计、降低成本。这时可以考虑利用行时序和帧时序中SRAM总线空闲的时序段,在不关闭图像显示的情况下实现显存SRAM的数据更新。该方法的更新率与数据写速度密切相关,显存的写数据速度越快,该方法的更新率就越高。

视频DAC模块

ADV7123是一个三路10位输入的高速视频DAC,具有330MHz的最大采样速度,与多种高精度的显示系统兼容,包括RS-343A和RS-170,可以广泛应用于如HDTV、数字视频系统(1600*1200 @100Hz)、高分辨率的彩色图片图像处理、视频信号再现等,因此能够满足多方面应用需求。视频DAC(ADV7123)工作原理如图3所示。

图3 ADV7123工作原理

CPLD提供Hsync(行)、Vsync(场)同步信号,直接接入15针的VGA显示接口连接器。在点时钟脉冲pixel clock的作用下将3路10位的RGB信号送入数据寄存器,而后送到3个DAC模块,复合消隐信号和复合同步信号加到红、绿、蓝模拟信号送到输出端。

系统软件设计

系统软件设计是本文的重点,主要包括三部分内容:SRAM读写状态机的设计、CPLD与SRAM的缓冲模块通信以及VGA时序设计。

SRAM读写状态机的设计

以6416为核心的图象处理机通过外部存储器接口向外传送数据,连接到后端的显示系统;但SRAM需要严格的通信时序确保数据的完整性,此处在CPLD内部通过状态机构造SRAM的读时序和写时序,确保了6416能够和SRAM正常通信,也确保缓冲模块的正常运行。读写SRAM的时序图如图4和图5所示。

图4 读周期时序图

图5 写周期时序图

当从SRAM中读取数据时:首先使能片选;UB、LB时钟处于有效状态;WE为高,时钟处于无效状态;主要由OE的时序来控制使其符合读时序图,才能正确地读出存储器中的数据。在向SRAM中写入数据时,同样首先使能片选;UB、LB时钟处于有效状态;OE为高,时钟处于无效状态;主要由WE的时序来控制使之符合写时序图,才能向存储器正确写入数据。

CPLD与SRAM组成的缓冲模块的通信

CPLD与SRAM组成的缓冲通信模块,即如何乒乓读写SRAM机制。设定一个读写标志FLAG,当一块SRAM写满一帧图像时,FLAG会出现“1”到“0”或者“0”到“1”的跳变,同时切换数据流的流向,写另一块SRAM,同时切换输出至后级DAC的数据流;如此循环,软件流程图如图6所示。

图6 缓冲模块通信软件流程图

VGA时序发生器设计

VGA标准时序参考图如图7所示,并用VERILOGHDL设计For VESA 800*600 @ 60Hz:VGA时序的源代码:

图7 VGA标准时序参考图

系统分析

经过反复测试,系统能够将采集端数据实时传送到显示器上,具体性能指标如下:

视频输出:VGA视频输出

视频显示DA转换精度: 10bit

图像输出标准: SVGA(75Hz, 800×600)

显示分辨率: 10bit

结语

该VGA视频显示系统不但可以稳定地采集图像数据,而且可以实时将数据传输到CRT显示器,便于以后人工综合分析、处理。它特别适用于大型商场等显示端,可以说是一个理想的解决方案。

CPLD 集成电路 汽车电子 电子 DAC DSP 总线 电路 连接器 显示器 相关文章:

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)

- Virtex-5推动超宽带通信和测距的发展(01-06)