基于SYSTEM C的FPGA设计方法

时间:07-18

来源:互联网

点击:

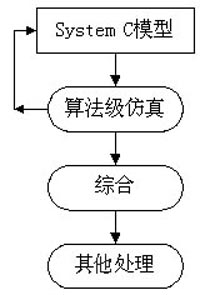

图2

这种设计方法与现在常用的设计方法相比有很多优点:

1.精炼的设计方法。使用System C设计系统,系统设计人员不必花费很大的精力将整个系统设计由C语言描述转换为HDL描述。系统设计人员可以通过在C模块中很小的区域范围内加入必要的硬件和时序结构描述,从而将C模块方便准确地转化为一个有效的硬件设计,而避免将另行设计一个硬件模块。利用System C设计方法,设计人员可以很轻松地实现一个设计的更改,或在优化算法时检测出一些设计错误并及时修改。

2.单一语言书写。使用System C设计系统,整个设计都用一种语言设计系统,降低了对设计人员的要求,减少了语言转换时所造成的错误。这一优点也使得设计人员可以在一个比较高的层次上进行系统模块设计。在较高层次的设计会导致产生小的设计代码,使设计和仿真的速度比传统的设计方法要快很多。这一点是很显著的。

四、SYSTEM C基本概念

1.模块

模块是System C设计中的基本设计单元。模块可以使得设计者将一个复杂的系统分割为一些更小但易于管理的部分。System C模块的功能和作用与HDL语言中的模块是相类似的,这使得一位习惯于用HDL进行设计的设计人员可以很容易的转向用System C进行设计。

模块在System C中的关键字为SC_MODULE。紧跟着关键字后的是模块的名称,如SC_MODULE(fifo),这就定义了一个叫fifo的模块。定义的模块也可以像HDL语言一样包含端口、信号、其它模块、处理过程和结构体,这些单元实现用以实现模块的功能。通过端口可以将几个模块连接起来。

模块被保存为.h文件。如果在一个模块中调用其它模块,只需像C++中引入库一样将要调用的模块作为一个库引入即可。

2.过程

模块中的处理过程(process)类似于C语言中的子程序,与C语言中的子程序不同的的是它具有HDL语言中的触发功能。处理过程(process)的具体工作部分被保存为.cpp文件。处理过程的调用类似于在C语言中子程序的调用。根据不同的要求,SystemC中有三种处理过程。

● Methods : SC_METHOD()

● Threads : SC_THREAD()

● Clock Threads : SC_CTHREAD() SC_METHOD是用来描述组合逻辑,它由输入信号的变化触发,但不能在两次调用中保存控制状态。并且在SC_METHOD中不能包含无限循环。由于组合逻辑有可能导致毛刺的产生,从而影响系统性能,所以SC_METHOD不易太复杂。

下面是一个简单的SC_METHOD例子:

SC_MODULE(example) {

sc_in din;

sc_out dout;//端口

void inverter();//处理过程声明

SC_CTOR(example) {

SC_METHOD(inverter);

sensitive(din);//处理过程由输入变化触发

}

};

处理过程inverter如下:

void example::inverter() {

bool internal;

internal = din;//输入数据取反后由输出端口输出

dout = ~internal;

}

SC_THREAD是最常用的处理过程,基本上可以用在任何地方。它是由输入信号的变化触发,但与SC_METHOD不同的是它可以在两次调用这保存控制状态。它的功能类似于积存器的功能。SC_THREAD中可以包含有wait()函数,这使得处理过程可以被挂起。

SC_CTHREAD是SC_THREAD的一种特殊情况。SC_CTHREAD能产生更好的综合效果。SC_CTHREAD中可以使用wait()函数。在不同的状态间加入wait()函数,设计人员可以用SC_CTHREAD来实现状态机。这种设计风格是简便的而且容易理解。SC_CTHREAD只能由时钟信号沿触发,而SC_THREAD可以由其它非时钟信号触发。如果在时钟上跳边触发,可以使用pos()函数,反之用neg()。

为进一步说明SC_CTHREAD,下面给出了一个SC_CTHREAD的例子。

SC_MODULE(example) {

sc_in_clk clock;//输入时钟

sc_in trigger, din;

sc_out dout;

void invert();

SC_CTOR(example) {

SC_CTHREAD(toggler, clock.pos());//时钟上升沿触发

}

}

void example::invert() {

bool last = false;

for (;;) {

wait_until(trigger.delayed() == true);//等到下个时钟上升沿 //且trigger=1再执行

last = din; dout = last; wait();

last =~din; dout = last;wait();//下个上升沿才更改数据

}

}

3.端口与信号

与HDL语言相似,使用System C库就可以在C程序中加入端口和信号。这些原先C语言中没有的功能,使设计更复合硬件设计的要求。

模块与模块之间是通过端口信号加一联系。只要两个端口被连接在一起,信号就可以在它们之间进行传递。对于这一点习惯用HDL进行设计的设计人员是很容易理解和接受的,因为这和HDL中端口的功能是一样的。 信号只是在一个模块的内部使用,这也是和HDL中信号的用法是一致的。 下面给出端口和信号声明的例子。

sc_in<“类型”> din// 输入端口din

sc_out<“类型”> dout// 输出端口dout

sc_inout<“类型”> q// 输入输出端口q

sc_signal i[16]; //创建一个具有16比特的逻辑型信号i

集成电路 DSP 仿真 C语言 VHDL Verilog 相关文章:

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA 重复配置和测试的实现(08-14)

- 适用于消费性市场的nano FPGA技术(09-27)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)