一种基于移位寄存器的CAM的Verilog HDL实现

时间:07-15

来源:互联网

点击:

CAM(Content ADDRessable Memory,内容可寻址存储器)是一种特殊的存储阵列。它通过将输入数据与CAM中存储的所有数据项同时进行比较,迅速判断出输入数据是否与CAM中的存储数据项相匹配,并给出匹配数据项的对应地址和匹配信息。CAM以其高速查找、大容量等特点而被广泛地应用于电讯、网络等领域。

本文介绍一种用Verilog HDL设计CAM的方案。该方案以移位寄存器为核心,具有可重新置改变字长、易于扩展、匹配查找速度快等特点。

1 CAM功能描述

CAM的基本框图如图1所示。

与RAM相似,CAM是将数据项存储在一个阵列中。每个数据项的位数叫做字宽,CAM中所有数据项的条数叫做CAM的深度。通过字宽和深度可以表征CAM中容量。

在写CAM模式(配置)时,WRITE_E信号有效,MATCH_E信号无效,此时通过地址线ADDR选择DATA_IN输入的数据将要被写放哪一个单元;在读CAM模式(查找匹配)时,WRITE_E信号无效,MATCH_E信号有效,CAM将不使用地址线,而是直接将DATA_IN读入的数据与CAM中存储的各条数据项进行并行比较。如果CAM中含有与此时输入数据相匹配的存储数据项,CAM将从MATCH_ADDR输出此存储数据项的地址,并且通过MATH_OK输出匹配成功的信息。在查找匹配模式时,由于CAM是将输入数据与存储数据项并行比较,所以速度极快。同时,由于不需要通过地址线来寻址数据项,CAM将不受地址线宽度的限制,容易扩展。

2 基于移位寄存器的CAM的设计

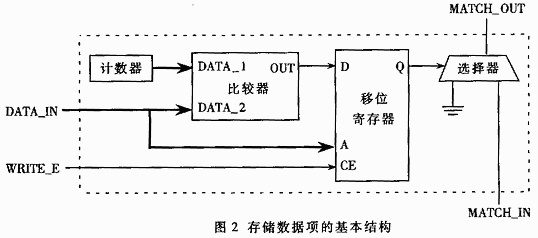

为了说明设计方案,以一个宽度为4位、深度为1的基本CAM存储单元为例。利用这样一个基本存储单元,通过适当级联,可以构成任意字宽和深度的CAM。该基本单元采用一个16位的移位寄存器、一个4位的比较器,外加16位的计数器和一个"二选一"的选择器构成。如图2所示。

在写CAM模式时,WRITE_E信号有效,DATA_IN输入的是将要写入数据存储项的4位数据。计数器进行从"1111"到"0000"的减计数,并将计数输出值与DATA_IN输入值进行比较。若二者相同,比较器输出"1"到移位寄存器中;不同则输出"0"到移位寄存器中。在16个时钟周期之后,将完成DATA_IN输入数据与计数器输出的所有情况的比较。这样,移位寄存器中将存入15个"0"和一个"1"。

在读CAM模式时,MATCH_IN为"1",此时,DATA_IN输入的数据直接送到移位寄存器的地址端,它将决定移位寄存器输出其16个位中的哪一位。如果该位输出"1",则表示此时DATA_IN与原来写入该单元的数据相同,即发生匹配;反之则输出"0",表示无匹配项。

以上讨论只是针对4位字宽的数据项的读写,而对于更长字宽的数据项,必须进行字宽扩展。可用多个比较器和移位寄存器组成的存储数据项并联在一起,组成一个字结构,即把输入的数据按每4位分为一组,每组对应一套比较器和移位寄存器,每组只产生一个最终的MTACH_OUT信号。例如,对于16位的数据项,就需要4组这样的结构。这4组基本结构中的读和写可以同时完成。只有4组都产生匹配信号,最终的MATCH_OUT输出才有"1",表明读入的16位DATA_IN数据与存储的数据项匹配。

CAM只需要存储多个数据项,因此需要多个字结构的深度扩展。将这些字结构中的比较器和移位寄存器分别组合在一起,构成比较器阵列和移位寄存器阵列。为了在写CAM时进行写入数据的定位,还需要一个地址译码模块来指出是对哪一个数据项进行写操作。在读CAM时,得到输入数据与各个存储数据项的匹配信息之后,还要对这些匹配信息进行编码,得到最后要输出的相匹配的存储数据项的地址MATCH_ADDR和是否发生匹配的信息MATCH_OK。

完整的CAM结构框图见图3。

3 基于移位寄存器的CAM的Verilog HDL实现

硬件描述语言VerilogHDL是一种应用于电路设计的描述语言,具有行为级、寄存器传输级、逻辑门级和开关级等多层次描述。它简单易读,描述与工艺无关,并且得到许多EDA工具的支持。利用Verilog HDL语言进行电路设计可以大大节省设计时间和成本。

本设计以一个数据项字宽为16位、深度为8的CAM为例,进行Verilog HDL设计,并利用Xilinx Virtex系列中XCV1000器件进行综合。综合后的仿真分析表明,该方案是合理可行的。

图4为匹配查找的时序仿真结果,CAM中预先放入了0019H,001AH,…,001DH五个数据。CLK为系统时钟,DATA_IN为数据输入,MATCH_ENABLE为读CAM(查找)允许信号,GLOBAL_RST为全局清零信号,R_MATCH_ADDR为匹配地址输出信号,R_MATCH_OK为是否发生匹配信号。从仿真波形可以看出,输入数据经过两个时钟周期,输出匹配信息,包括是否匹配和相匹配的存储数据项的地址。如果不匹配,是否匹配的信号为0,而输出地址线不变。

本方案以移位寄存器设计CAM,在写模式下需要16个时钟周期完成一个数据项的写入;读模式仅需一个时钟周期。它具有速度快、易于重新配置、易于扩展等特点。本方案中的CAM利用Xilinx Virtex系列器件实现,时钟最高频率可达80MHz以上。以本方案为基础,扩展到32位、36位的实用化CAM已运用于网络协处理器的仿真测试中,并取得了较好的效果。

本文介绍一种用Verilog HDL设计CAM的方案。该方案以移位寄存器为核心,具有可重新置改变字长、易于扩展、匹配查找速度快等特点。

1 CAM功能描述

CAM的基本框图如图1所示。

与RAM相似,CAM是将数据项存储在一个阵列中。每个数据项的位数叫做字宽,CAM中所有数据项的条数叫做CAM的深度。通过字宽和深度可以表征CAM中容量。

在写CAM模式(配置)时,WRITE_E信号有效,MATCH_E信号无效,此时通过地址线ADDR选择DATA_IN输入的数据将要被写放哪一个单元;在读CAM模式(查找匹配)时,WRITE_E信号无效,MATCH_E信号有效,CAM将不使用地址线,而是直接将DATA_IN读入的数据与CAM中存储的各条数据项进行并行比较。如果CAM中含有与此时输入数据相匹配的存储数据项,CAM将从MATCH_ADDR输出此存储数据项的地址,并且通过MATH_OK输出匹配成功的信息。在查找匹配模式时,由于CAM是将输入数据与存储数据项并行比较,所以速度极快。同时,由于不需要通过地址线来寻址数据项,CAM将不受地址线宽度的限制,容易扩展。

2 基于移位寄存器的CAM的设计

为了说明设计方案,以一个宽度为4位、深度为1的基本CAM存储单元为例。利用这样一个基本存储单元,通过适当级联,可以构成任意字宽和深度的CAM。该基本单元采用一个16位的移位寄存器、一个4位的比较器,外加16位的计数器和一个"二选一"的选择器构成。如图2所示。

在写CAM模式时,WRITE_E信号有效,DATA_IN输入的是将要写入数据存储项的4位数据。计数器进行从"1111"到"0000"的减计数,并将计数输出值与DATA_IN输入值进行比较。若二者相同,比较器输出"1"到移位寄存器中;不同则输出"0"到移位寄存器中。在16个时钟周期之后,将完成DATA_IN输入数据与计数器输出的所有情况的比较。这样,移位寄存器中将存入15个"0"和一个"1"。

在读CAM模式时,MATCH_IN为"1",此时,DATA_IN输入的数据直接送到移位寄存器的地址端,它将决定移位寄存器输出其16个位中的哪一位。如果该位输出"1",则表示此时DATA_IN与原来写入该单元的数据相同,即发生匹配;反之则输出"0",表示无匹配项。

以上讨论只是针对4位字宽的数据项的读写,而对于更长字宽的数据项,必须进行字宽扩展。可用多个比较器和移位寄存器组成的存储数据项并联在一起,组成一个字结构,即把输入的数据按每4位分为一组,每组对应一套比较器和移位寄存器,每组只产生一个最终的MTACH_OUT信号。例如,对于16位的数据项,就需要4组这样的结构。这4组基本结构中的读和写可以同时完成。只有4组都产生匹配信号,最终的MATCH_OUT输出才有"1",表明读入的16位DATA_IN数据与存储的数据项匹配。

CAM只需要存储多个数据项,因此需要多个字结构的深度扩展。将这些字结构中的比较器和移位寄存器分别组合在一起,构成比较器阵列和移位寄存器阵列。为了在写CAM时进行写入数据的定位,还需要一个地址译码模块来指出是对哪一个数据项进行写操作。在读CAM时,得到输入数据与各个存储数据项的匹配信息之后,还要对这些匹配信息进行编码,得到最后要输出的相匹配的存储数据项的地址MATCH_ADDR和是否发生匹配的信息MATCH_OK。

完整的CAM结构框图见图3。

3 基于移位寄存器的CAM的Verilog HDL实现

硬件描述语言VerilogHDL是一种应用于电路设计的描述语言,具有行为级、寄存器传输级、逻辑门级和开关级等多层次描述。它简单易读,描述与工艺无关,并且得到许多EDA工具的支持。利用Verilog HDL语言进行电路设计可以大大节省设计时间和成本。

本设计以一个数据项字宽为16位、深度为8的CAM为例,进行Verilog HDL设计,并利用Xilinx Virtex系列中XCV1000器件进行综合。综合后的仿真分析表明,该方案是合理可行的。

图4为匹配查找的时序仿真结果,CAM中预先放入了0019H,001AH,…,001DH五个数据。CLK为系统时钟,DATA_IN为数据输入,MATCH_ENABLE为读CAM(查找)允许信号,GLOBAL_RST为全局清零信号,R_MATCH_ADDR为匹配地址输出信号,R_MATCH_OK为是否发生匹配信号。从仿真波形可以看出,输入数据经过两个时钟周期,输出匹配信息,包括是否匹配和相匹配的存储数据项的地址。如果不匹配,是否匹配的信号为0,而输出地址线不变。

本方案以移位寄存器设计CAM,在写模式下需要16个时钟周期完成一个数据项的写入;读模式仅需一个时钟周期。它具有速度快、易于重新配置、易于扩展等特点。本方案中的CAM利用Xilinx Virtex系列器件实现,时钟最高频率可达80MHz以上。以本方案为基础,扩展到32位、36位的实用化CAM已运用于网络协处理器的仿真测试中,并取得了较好的效果。

Verilog 比较器 电路 EDA Xilinx 仿真 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)