EDA技术与FPGA设计应用

时间:06-11

来源:互联网

点击:

GA设计应用及优化策略

1.FPGA设计层次分析

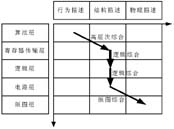

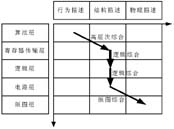

FPGA设计包括描述层次及描述领域两方面内容。通常设计描述分为6个抽象层次,从高到低依次为:系统层、算法层、寄存器传输层、逻辑层、电路层和版图层。对每一层又分别有三种不同领域的描述:行为域描述、结构域描述和物理域描述。

系统层是系统最高层次的抽象描述,针对于电子系统整体性能。算法层又称为行为层,它是在系统级性能分析和结构划分后对每个模块的功能描述。算法层所描述的功能、行为最终要用数字电路来实现。而数字电路本质上可视为由寄存器和组合逻辑电路组成,其中寄存器负责信号存储,组合逻辑电路负责信号传输。寄存器传输层描述正是从信号存储、传输的角度去描述整个系统。寄存器和组合逻辑本质上是由逻辑门构成,逻辑层正是从逻辑门组合及连接角度去描述整个系统。

FPGA各个描述层次及综合技术关系如图1所示。传统的综合工具是将寄存器传输级(RTL)的描述转化为门级描述。随着以行为设计为主要标志的新一代系统设计理论的不断成熟,能够将系统行为级描述转化为RTL描述的高层次综合技术不断涌现。

作为现代集成电路设计的重点与热点,FPGA设计一般采用自顶向下、由粗到细、逐步求精的方法。设计最顶层是指系统的整体要求,最下层是指具体的逻辑电路实现。自顶向下是将数字系统的整体逐步分解为各个子系统和模块,若子系统规模较大则进一步分解为更小的子系统和模块,层层分解,直至整个系统中各子模块关系合理、便于设计实现为止。

2.VHDL在FPGA设计中的应用

集成电路设计规模及复杂度不断增大,用传统原理图方法进行系统级芯片设计已不能满足设计要求,而硬件描述语言(HDL,Hardware Description Language)在进行大规模数字系统设计时具有诸多优势,因此利用硬件描述语言进行系统行为级设计已成为FPGA与ASIC设计的主流。目前最流行、最具代表性的硬件描述语言是美国国防部(DOD)开发的VHDL(VHSIC Hardware Description Language)和GDA(Gateway Design Automation)公司开发的Verilog HDL。

VHSIC代表Very High Speed Integrated Circuit,因此VHDL即甚高速集成电路硬件描述语言。VHDL语法严格,1987年即成为IEEE标准,即IEEE STD 1076-1987,1993年进一步修订成为IEEE STD 1076-1993。

VHDL作为IEEE标准,已得到众多EDA公司支持,其主要优点有:

● 描述能力强,支持系统行为级、寄存器传输级和门级三个层次设计;

● 可读性好、移植性强,其源文件既是程序又是文档,便于复用和交流;

● 支持自顶向下的设计和基于库(Library-based)的设计;

● 支持同步、异步及随机电路的设计;

● 与工艺无关,生命周期长。

VHDL语言主要应用在行为层和寄存器传输层,这两层可充分发挥出VHDL面向高层的优势。利用VHDL实现数字电路的实质是利用综合工具将高层次描述转化为低层次门级描述,其中综合可分为三个层次:高层次综合(High-Level Synthesis)、逻辑综合(Logic Synthesis)和版图综合(Layout Synthesis)。

3.基于VHDL的FPGA系统行为级设计

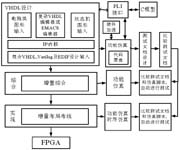

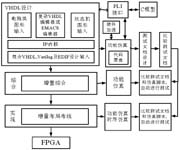

基于VHDL的FPGA设计基本流程及详细流程分别如图2和图3所示,具体包括以下重要环节:设计输入(Design Entry)、设计综合(Design Synthesis)、设计约束(Design Constraints)、设计实现(Design Implement)、设计仿真(Design Simulation)和器件编程(Device Programming)。

设计输入主要采用HDL(硬件描述语言)、ECS(Engineering Schematic Capture,原理图编辑器)和FSM(Finite State Machine,有限状态机);

设计综合就是依据逻辑设计描述和约束条件,利用开发工具进行优化处理,将HDL文件转变为硬件电路实现方案,其实质就是优化设计目标的过程;

设计约束主要包括设计规则约束、时间约束、面积约束三种,通常时间约束的优先级高于面积约束;

设计实现对于FPGA分为编译规划、布局布线(PAR,Place And Route)、程序比特流文件产生;对于CPLD则是编译、配置、比特流文件产生;

设计仿真分为功能仿真和时序时延仿真。功能仿真在设计输入之后、综合之前进行,只进行功能验证,又称为前仿真。时序时延仿真在综合和布局布线之后进行,能够得到目标器件的详细时序时延信息,又称为后仿真;

器件编程是指在功能仿真与时序时延仿真正确的前提下,将综合后形成的位流编程下载到具体的FPGA/CPLD芯片中,又称芯片配置。FPGA/CPLD编程下载通常可使用JTAG编程器、PROM文件格式器和硬件调试器三种方式,其中JTAG(Joint Test Action Group,联合测试行动组)是工业标准的IEEE 1149.1边界扫描测试的访问接口,用作编程功能可省去专用的编程接口,减少系统引出线,有利于各可编程逻辑器件编程接口的统一,因此应用广泛。

1.FPGA设计层次分析

FPGA设计包括描述层次及描述领域两方面内容。通常设计描述分为6个抽象层次,从高到低依次为:系统层、算法层、寄存器传输层、逻辑层、电路层和版图层。对每一层又分别有三种不同领域的描述:行为域描述、结构域描述和物理域描述。

系统层是系统最高层次的抽象描述,针对于电子系统整体性能。算法层又称为行为层,它是在系统级性能分析和结构划分后对每个模块的功能描述。算法层所描述的功能、行为最终要用数字电路来实现。而数字电路本质上可视为由寄存器和组合逻辑电路组成,其中寄存器负责信号存储,组合逻辑电路负责信号传输。寄存器传输层描述正是从信号存储、传输的角度去描述整个系统。寄存器和组合逻辑本质上是由逻辑门构成,逻辑层正是从逻辑门组合及连接角度去描述整个系统。

FPGA各个描述层次及综合技术关系如图1所示。传统的综合工具是将寄存器传输级(RTL)的描述转化为门级描述。随着以行为设计为主要标志的新一代系统设计理论的不断成熟,能够将系统行为级描述转化为RTL描述的高层次综合技术不断涌现。

作为现代集成电路设计的重点与热点,FPGA设计一般采用自顶向下、由粗到细、逐步求精的方法。设计最顶层是指系统的整体要求,最下层是指具体的逻辑电路实现。自顶向下是将数字系统的整体逐步分解为各个子系统和模块,若子系统规模较大则进一步分解为更小的子系统和模块,层层分解,直至整个系统中各子模块关系合理、便于设计实现为止。

2.VHDL在FPGA设计中的应用

集成电路设计规模及复杂度不断增大,用传统原理图方法进行系统级芯片设计已不能满足设计要求,而硬件描述语言(HDL,Hardware Description Language)在进行大规模数字系统设计时具有诸多优势,因此利用硬件描述语言进行系统行为级设计已成为FPGA与ASIC设计的主流。目前最流行、最具代表性的硬件描述语言是美国国防部(DOD)开发的VHDL(VHSIC Hardware Description Language)和GDA(Gateway Design Automation)公司开发的Verilog HDL。

VHSIC代表Very High Speed Integrated Circuit,因此VHDL即甚高速集成电路硬件描述语言。VHDL语法严格,1987年即成为IEEE标准,即IEEE STD 1076-1987,1993年进一步修订成为IEEE STD 1076-1993。

VHDL作为IEEE标准,已得到众多EDA公司支持,其主要优点有:

● 描述能力强,支持系统行为级、寄存器传输级和门级三个层次设计;

● 可读性好、移植性强,其源文件既是程序又是文档,便于复用和交流;

● 支持自顶向下的设计和基于库(Library-based)的设计;

● 支持同步、异步及随机电路的设计;

● 与工艺无关,生命周期长。

VHDL语言主要应用在行为层和寄存器传输层,这两层可充分发挥出VHDL面向高层的优势。利用VHDL实现数字电路的实质是利用综合工具将高层次描述转化为低层次门级描述,其中综合可分为三个层次:高层次综合(High-Level Synthesis)、逻辑综合(Logic Synthesis)和版图综合(Layout Synthesis)。

3.基于VHDL的FPGA系统行为级设计

基于VHDL的FPGA设计基本流程及详细流程分别如图2和图3所示,具体包括以下重要环节:设计输入(Design Entry)、设计综合(Design Synthesis)、设计约束(Design Constraints)、设计实现(Design Implement)、设计仿真(Design Simulation)和器件编程(Device Programming)。

设计输入主要采用HDL(硬件描述语言)、ECS(Engineering Schematic Capture,原理图编辑器)和FSM(Finite State Machine,有限状态机);

设计综合就是依据逻辑设计描述和约束条件,利用开发工具进行优化处理,将HDL文件转变为硬件电路实现方案,其实质就是优化设计目标的过程;

设计约束主要包括设计规则约束、时间约束、面积约束三种,通常时间约束的优先级高于面积约束;

设计实现对于FPGA分为编译规划、布局布线(PAR,Place And Route)、程序比特流文件产生;对于CPLD则是编译、配置、比特流文件产生;

设计仿真分为功能仿真和时序时延仿真。功能仿真在设计输入之后、综合之前进行,只进行功能验证,又称为前仿真。时序时延仿真在综合和布局布线之后进行,能够得到目标器件的详细时序时延信息,又称为后仿真;

器件编程是指在功能仿真与时序时延仿真正确的前提下,将综合后形成的位流编程下载到具体的FPGA/CPLD芯片中,又称芯片配置。FPGA/CPLD编程下载通常可使用JTAG编程器、PROM文件格式器和硬件调试器三种方式,其中JTAG(Joint Test Action Group,联合测试行动组)是工业标准的IEEE 1149.1边界扫描测试的访问接口,用作编程功能可省去专用的编程接口,减少系统引出线,有利于各可编程逻辑器件编程接口的统一,因此应用广泛。

电子 集成电路 电路 EDA 自动化 FPGA PCB 仿真 CPLD 半导体 Xilinx Altera VHDL Verilog MCU 单片机 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)