如何利用开关稳压器为GSPS ADC 供电

时间:04-06

来源:互联网

点击:

简介

模数转换器 (ADC) 在任何依赖外部(模拟)世界收集信息进行 (数字)处理的系统中都是不可或缺的组成部分。从通信接收机到数字测试和测量再到军事和航空航天—此处仅举数例—这些 系统在不同的应用中各有不同。硅片处理技术的发展(比如65 nm CMOS 和28 nm CMOS)使高速ADC 得以跨越GSPS(每秒千兆) 门槛。对于系统设计人员来说,这意味着能用于数字处理的采样 带宽越来越宽。出于环境和成本方面的考虑,系统设计人员不断 尝试降低总功耗。一般而言,ADC 制造商建议采用低噪声LDO (低压差)稳压器为GSPS(或RF 采样)ADC 供电,以便达到最 高性能。然而,这种方式的输电网络 (PDN) 效率不高。设计人员 对于使用开关稳压器直接为GSPS ADC 供电且不会大幅降低 ADC 性能的方法呼声渐高。

解决方案是谨慎地进行PDN 部署和布局布线,确保ADC 性能不受影响。本文讨论了线性和开关电源的不同之处,并表明GSPS ADC 与DC-DC 转换器搭配使用可大幅改善系统能效,且不会影响ADC 性能。本文通过输电网络组合探讨GSPS ADC 性能,并对成本和性能进行了对比分析。

通常建议GSPS ADC 使用的PDN

高带宽、高采样速率ADC(或GSPS ADC)可以具有多个电源 域(比如AVDD 或DVDD)。随着尺寸的缩小,不仅电源域的 数量增加,为ADC 供电所需的不同电压数量也有所增加。例如,AD9250是一款14 位、170 MSPS/250 MSPS、JESD204B 双通道 模数转换器,采用180 nm CMOS 工艺制造,具有3 个域:AVDD、 DVDD 和DRVDD。然而,所有3 个域都具有相同的电压:1.8 V。

现在,来看一下AD9680:一款14 位、1.25 GSPS/1 GSPS/820 MSPS/500 MSPS JESD204B 双通道模数转换器,采用65 nm CMOS 工艺制造。这款GSPS ADC 具有7 个不同的域(AVDD1、 AVDD1_SR、AVDD2、AVDD3、DVDD、DRVDD 和SPIVDD), 以及3 个不同的电压:1.25 V、2.5 V 和3.3 V。

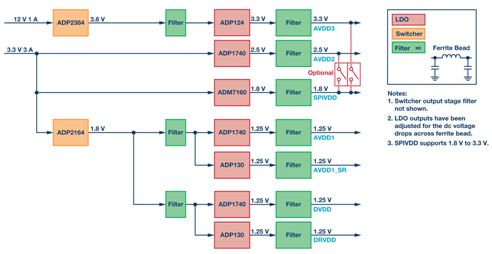

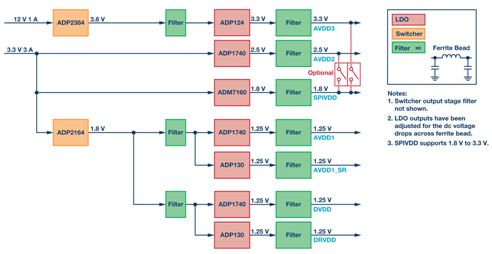

ADP2384和ADP2164 DC-DC 转换器用于使电压下降到可控水 平,以便LDO 能够在不进入热关断的情况下进行稳压操作。这 些电源域和各种电压的日益普及是在这些采样速率下工作所必 需的。它们可以确保各种电路域(比如采样、时钟、数字和串行 器)之间具有正确的隔离,同时使性能最优。正是因为这个原因, ADC 制造商才设计了评估板,并推荐详细的电源设计方案,确保 最大程度降低风险,使性能最大化。例如,图1 显示了AD9680 评估板使用的默认 PDN 的功能框图。根据 Vita57.1 规格,电源输 入来自 FMC(FPGA 夹层卡)连接器供应的12 V/1 A 和3.3 V/3 A 电源。

图1. 用于AD9680 评估板的默认PDN。

显而易见,这是一种昂贵的解决方案,有7 个LDO 稳压器,每 个域一个。这款PDN 也许是性能最优的,但肯定不是最具性价 比或运行成本效率最高的。系统设计人员认为部署含有多个 ADC 的系统非常有难度。例如,相控阵雷达方案包含成百个 AD9680,全都以同步方式工作。要求系统设计人员为上百个ADC 的每一个电压域都分配一个LDO 稳压器是不合理的。

用于GSPS ADC 的更简单的PDN

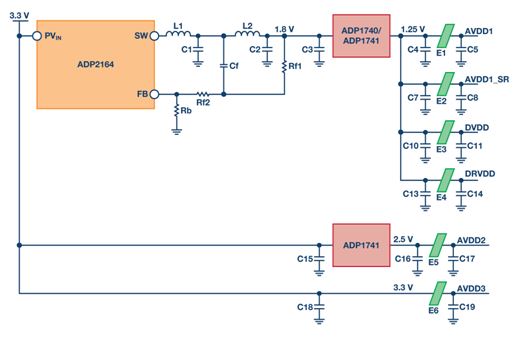

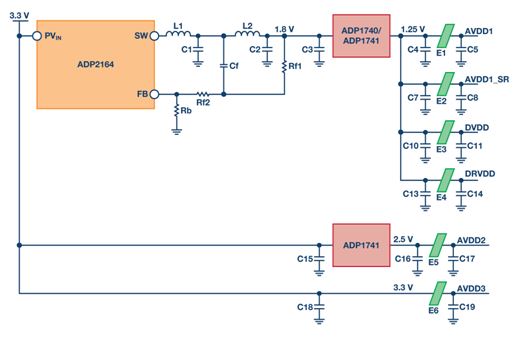

一种更具性价比的PDN 设计方案是将具有同样电压值(比如所 有的1.25 V 模拟域)的域组合起来,然后用同一个LDO 来驱 动。这样可以减少元件数(以及物料清单—BOM—成本),这 可能适合某些设计。其简化PDN 如图2 所示;该图为AD9680 评估板的部署。在该部署中,整个AD9680 都可以使用3.3 V 输入供电。

图2. AD9680评估板的简化PDN。

驱动AD9680 的DC-DC 转换器

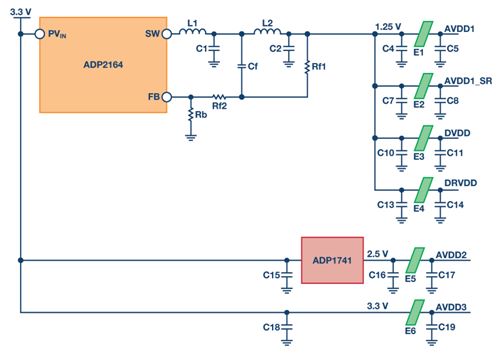

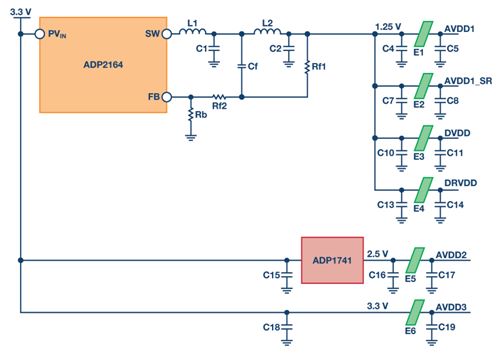

通过移除为1.25 V 域供电的单个LDO,还可进一步简化PDN。 这是最高效、最具性价比的解决方案。这种方案的困难之处在于 确保DC-DC 转换器的操作稳定性,从而不影响ADC 性能。 ADP2164 驱动AD9680 所有1.25 V 域(AVDD1、AVDD1_SR、 DVDD 和DRVDD)的PDN 如图3 所示。

图3. 使用DC-DC转换器为AD9680 供电。

比较不同的PDN

对上文讨论的3 个PDN 以及第4 个网络进行测试;第4 个网络 采用基准电源为AD9680 评估板供电。表1 列出了AD9680 评估 板上部署的各种输电网络。

表1. 输电网络列表

由于SPIVDD 可以支持1.8 V 至3.3 V 且被认为属于非关键节点, 因此它采用1.8 V LDO 输出供电。在一般系统部署中,SPIVDD 可连接2.5 V 或3.3 V 域。也就是说,在那些SPI 总线由很多ADC 与DAC 共享的系统中,仍旧应当监控SPIVDD 连接。如有这种 情况,那么必须非常仔细,确保正常的SPI 操作不会导致SPIVDD 域产生电源瞬变。如果SPIVDD 变得低于阈值电平,那么这些电 源瞬变可能会触发上电复位 (POR) 的情况。

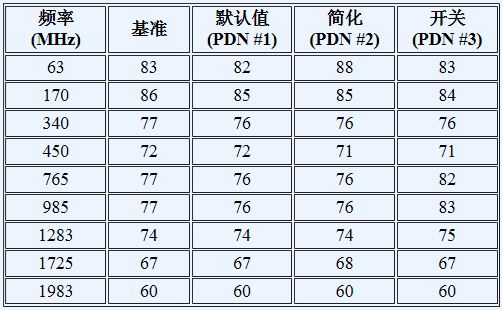

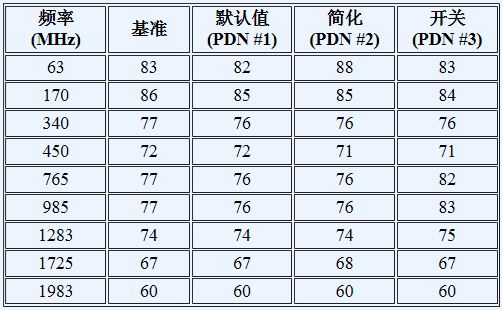

表2. SNR 性能对比 (dBFS)

表3. SFDR 性能对比 (dBFS)

表2 和表3 分别显示了AD9680 使用各种PDN 的SNR 和SFDR 性能。根据AD9680 数据手册提供各种奈奎斯特区的前端网络和 寄存器建议设置。

仅使用DC-DC 转换器为AD9680 的1.25 V 域供电的PDN (PDN #3) 在各种输入频率下显示出了良好的性能。这证明了可以组合 域,并在不损失大量ADC 性能的情况下以高效率、高性价比的 方式为它们供电。采用基准源的PDN 具有最佳的噪声性能,因 为它是噪声最低的电源。然而,值得注意的是PDN #3 始终比默 认网络 (PDN #1) 具有更好的SNR 性能。这可能是由于LDO 具 有良好的低频清除特性,但对于电路中存在高于几百kHz 的情况 却无能为力。这可以解释PDN #3 的0.2 dB 优势。

模数转换器 (ADC) 在任何依赖外部(模拟)世界收集信息进行 (数字)处理的系统中都是不可或缺的组成部分。从通信接收机到数字测试和测量再到军事和航空航天—此处仅举数例—这些 系统在不同的应用中各有不同。硅片处理技术的发展(比如65 nm CMOS 和28 nm CMOS)使高速ADC 得以跨越GSPS(每秒千兆) 门槛。对于系统设计人员来说,这意味着能用于数字处理的采样 带宽越来越宽。出于环境和成本方面的考虑,系统设计人员不断 尝试降低总功耗。一般而言,ADC 制造商建议采用低噪声LDO (低压差)稳压器为GSPS(或RF 采样)ADC 供电,以便达到最 高性能。然而,这种方式的输电网络 (PDN) 效率不高。设计人员 对于使用开关稳压器直接为GSPS ADC 供电且不会大幅降低 ADC 性能的方法呼声渐高。

解决方案是谨慎地进行PDN 部署和布局布线,确保ADC 性能不受影响。本文讨论了线性和开关电源的不同之处,并表明GSPS ADC 与DC-DC 转换器搭配使用可大幅改善系统能效,且不会影响ADC 性能。本文通过输电网络组合探讨GSPS ADC 性能,并对成本和性能进行了对比分析。

通常建议GSPS ADC 使用的PDN

高带宽、高采样速率ADC(或GSPS ADC)可以具有多个电源 域(比如AVDD 或DVDD)。随着尺寸的缩小,不仅电源域的 数量增加,为ADC 供电所需的不同电压数量也有所增加。例如,AD9250是一款14 位、170 MSPS/250 MSPS、JESD204B 双通道 模数转换器,采用180 nm CMOS 工艺制造,具有3 个域:AVDD、 DVDD 和DRVDD。然而,所有3 个域都具有相同的电压:1.8 V。

现在,来看一下AD9680:一款14 位、1.25 GSPS/1 GSPS/820 MSPS/500 MSPS JESD204B 双通道模数转换器,采用65 nm CMOS 工艺制造。这款GSPS ADC 具有7 个不同的域(AVDD1、 AVDD1_SR、AVDD2、AVDD3、DVDD、DRVDD 和SPIVDD), 以及3 个不同的电压:1.25 V、2.5 V 和3.3 V。

ADP2384和ADP2164 DC-DC 转换器用于使电压下降到可控水 平,以便LDO 能够在不进入热关断的情况下进行稳压操作。这 些电源域和各种电压的日益普及是在这些采样速率下工作所必 需的。它们可以确保各种电路域(比如采样、时钟、数字和串行 器)之间具有正确的隔离,同时使性能最优。正是因为这个原因, ADC 制造商才设计了评估板,并推荐详细的电源设计方案,确保 最大程度降低风险,使性能最大化。例如,图1 显示了AD9680 评估板使用的默认 PDN 的功能框图。根据 Vita57.1 规格,电源输 入来自 FMC(FPGA 夹层卡)连接器供应的12 V/1 A 和3.3 V/3 A 电源。

图1. 用于AD9680 评估板的默认PDN。

显而易见,这是一种昂贵的解决方案,有7 个LDO 稳压器,每 个域一个。这款PDN 也许是性能最优的,但肯定不是最具性价 比或运行成本效率最高的。系统设计人员认为部署含有多个 ADC 的系统非常有难度。例如,相控阵雷达方案包含成百个 AD9680,全都以同步方式工作。要求系统设计人员为上百个ADC 的每一个电压域都分配一个LDO 稳压器是不合理的。

用于GSPS ADC 的更简单的PDN

一种更具性价比的PDN 设计方案是将具有同样电压值(比如所 有的1.25 V 模拟域)的域组合起来,然后用同一个LDO 来驱 动。这样可以减少元件数(以及物料清单—BOM—成本),这 可能适合某些设计。其简化PDN 如图2 所示;该图为AD9680 评估板的部署。在该部署中,整个AD9680 都可以使用3.3 V 输入供电。

图2. AD9680评估板的简化PDN。

驱动AD9680 的DC-DC 转换器

通过移除为1.25 V 域供电的单个LDO,还可进一步简化PDN。 这是最高效、最具性价比的解决方案。这种方案的困难之处在于 确保DC-DC 转换器的操作稳定性,从而不影响ADC 性能。 ADP2164 驱动AD9680 所有1.25 V 域(AVDD1、AVDD1_SR、 DVDD 和DRVDD)的PDN 如图3 所示。

图3. 使用DC-DC转换器为AD9680 供电。

比较不同的PDN

对上文讨论的3 个PDN 以及第4 个网络进行测试;第4 个网络 采用基准电源为AD9680 评估板供电。表1 列出了AD9680 评估 板上部署的各种输电网络。

表1. 输电网络列表

由于SPIVDD 可以支持1.8 V 至3.3 V 且被认为属于非关键节点, 因此它采用1.8 V LDO 输出供电。在一般系统部署中,SPIVDD 可连接2.5 V 或3.3 V 域。也就是说,在那些SPI 总线由很多ADC 与DAC 共享的系统中,仍旧应当监控SPIVDD 连接。如有这种 情况,那么必须非常仔细,确保正常的SPI 操作不会导致SPIVDD 域产生电源瞬变。如果SPIVDD 变得低于阈值电平,那么这些电 源瞬变可能会触发上电复位 (POR) 的情况。

表2. SNR 性能对比 (dBFS)

表3. SFDR 性能对比 (dBFS)

表2 和表3 分别显示了AD9680 使用各种PDN 的SNR 和SFDR 性能。根据AD9680 数据手册提供各种奈奎斯特区的前端网络和 寄存器建议设置。

仅使用DC-DC 转换器为AD9680 的1.25 V 域供电的PDN (PDN #3) 在各种输入频率下显示出了良好的性能。这证明了可以组合 域,并在不损失大量ADC 性能的情况下以高效率、高性价比的 方式为它们供电。采用基准源的PDN 具有最佳的噪声性能,因 为它是噪声最低的电源。然而,值得注意的是PDN #3 始终比默 认网络 (PDN #1) 具有更好的SNR 性能。这可能是由于LDO 具 有良好的低频清除特性,但对于电路中存在高于几百kHz 的情况 却无能为力。这可以解释PDN #3 的0.2 dB 优势。

ADC CMOS LDO 开关电源 电压 电路 FPGA 连接器 总线 DAC 滤波器 仿真 ADI 电子 PCB 电流 电感 变压器 电容 电阻 相关文章:

- S3C2440A嵌入式手持终端电源管理系统设计(01-11)

- 基于CAN通信的电源监控系统的设计(04-06)

- 基于MSP430单片机的电源监控管理系统(04-20)

- 适用于全球交流电源的单节锂离子电池充电器设计(06-07)

- GPIB芯片TNT4882在多路程控电源中的应用(06-08)

- AD7656的原理及在继电保护产品中的应用(06-18)