基于FPGA的WPC标准无线充电器接收器解决方案

时间:02-11

来源:互联网

点击:

作者:Louis Tang,飞兆半导体

摘要:

随着无线充电器技术的蓬勃发展,以及越来越多的智能手机用户被各种充电电缆所困扰,方便易用的无线充电器将被普遍接受和采用。尽管目前有三种不同的无线充电器标准,但WPC Qi标准更常用于智能手机应用。本文将介绍基于FPGA解决方案的无线充电器接收器系统的架构。无线充电器接收器严格遵循最新的WPC Qi标准。接收器系统包含一个模拟模块和一个FPGA模块。模拟模块由分立式组件组成,包括全桥整流器模块、V/I检测和AD控制模块以及DC-DC模块。FPGA模块充当数字内核,其内嵌通信模块、控制模块、计算模块和收发器模块。它使用Verilog语言和状态机对FPGA编程。最后,通过测试和验证,无线充电器接收器在多个主要OEM的无线充电器发射器上工作极佳。

1. 背景

随着无线充电器技术的蓬勃发展,以及越来越多的智能手机用户被各种充电电缆所困扰,方便易用的无线充电器将被普遍接受和采用。目前有三种不同的无线充电器标准:WPC (Qi)、PMA和A4WP。WPC Qi标准更常用于智能手机应用。现在,许多智能手机OEM已推出支持WPC标准的无线充电器解决方案。本文将重点介绍WPC标准的无线充电器接收器解决方案,及其与基于FPGA的详细系统架构的关系。

2. WPC标准概述

WPC Qi标准提供无线充电器系统的详细说明,包括通信和传输协议。功率始终从充电板传输至移动设备。充电板包含一个称为功率发射器(由主线圈组成)的子系统,而移动设备包含一个称为功率接收器(由次级线圈组成)的子系统。

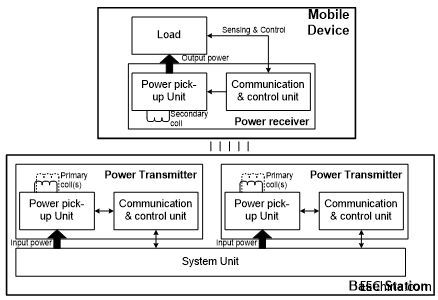

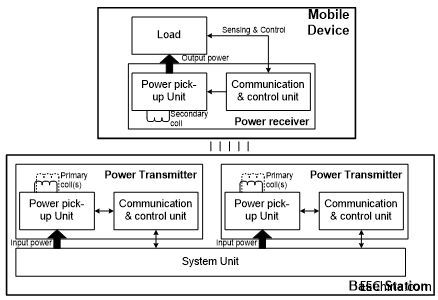

图1说明了基本系统配置。如图所示,功率发射器由两个主要功能单元组成,即功率转换单元和通信与控制单元。 控制与通信单元将转换的功率调节至功率接收器请求的水平。功率接收器则由一个功率拾取单元和一个通信与控制单元组成。

功率接收器位于手机端,因此接下来将主要介绍功率接收器系统,并说明基于FPGA的无线充电器接收器解决方案。

图1:基本系统配置

3. 基于FPGA的功率接收器系统概述

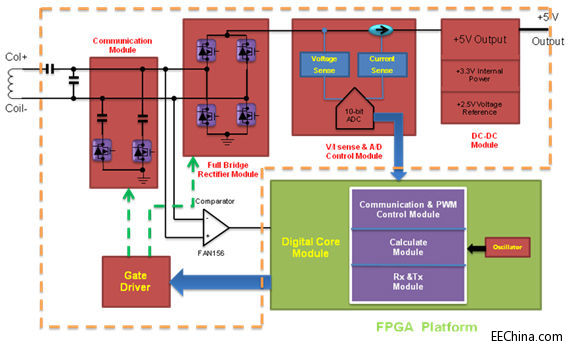

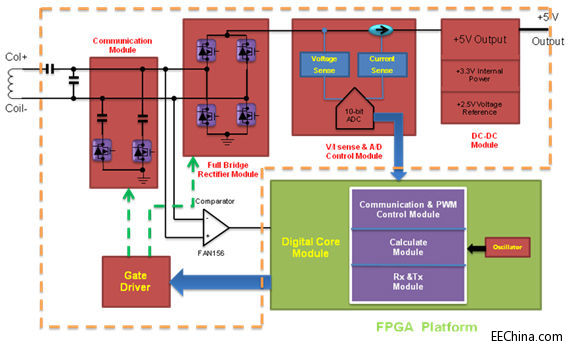

根据WPC Qi标准,功率接收器系统将包含一个功率拾取单元和一个通信与控制单元。示例中将详细介绍一个完全满足WPC Qi标准要求的接收器解决方案。 图2显示基于FPGA的功率接收器系统的架构。

图2:系统架构

如图2中所示,接收器系统包含两个子系统,一个是模拟模块,另一个是数字模块。模拟模块由分立式器件组成,包括全桥整流器模块、V/I检测和AD控制模块、通信模块和DC-DC模块。数字模块内置在FPGA中,使用Verilog语言编写程序。数字内核模块可分为三个主要子模块: 第一个是通信和PWM控制模块,第二个是计算模块,第三个是Rx和Tx(接收器和发射器)模块。下面更为详细地介绍了这些模块。

4. 模拟模块

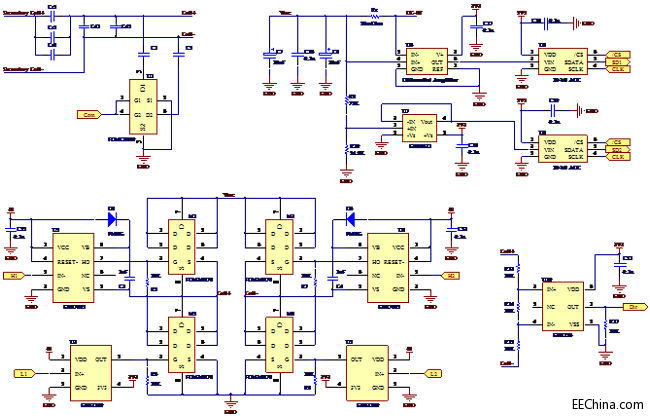

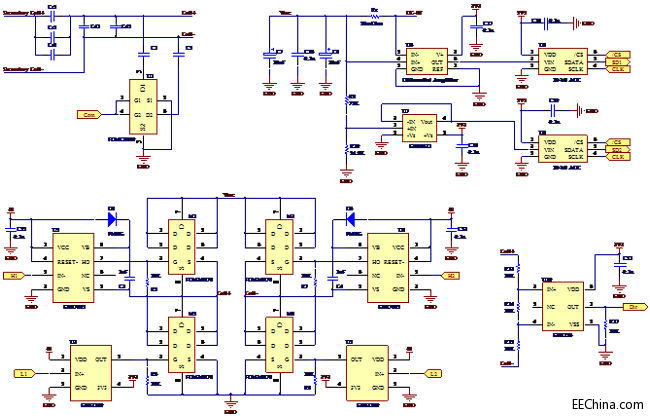

次级线圈是模拟模块的供电来源;主线圈和次级线圈组成一个完整的无芯谐振变压器。通过电磁耦合,交变磁场将在次级线圈产生交流电源,然后全桥整流器将交流转换为直流。图3显示部分模拟模块的原理图。

图3:部分模拟模块的原理图

4.1 全桥整流器

在此解决方案中,FAN156 (U10)比较器、FDMA8878(M1、M2、M3、M4)N沟道MOSFET、FAN7085和FAN3180(U2、U3、U4、U5)MOSFET驱动器组成全桥整流器。FAN156器件的输出信号直接馈入FPGA,然后FPGA向全桥整流器提供控制信号H1、L1、H2和L2。

FAN156比较器用于检测线圈两端的极性。如原理图中所示,如果线圈+为正极,线圈-为负极,则FAN156比较器向FPGA提供“H”信号。类似地,如果线圈+为负极,而线圈-为正极,则FAN156比较器向FPGA提供“L”信号。然后PWM控制模块将根据这些输入提供输出。从全桥整流器角度来看,如果线圈+为正极,线圈-为负极,则N沟道MOSFET的M1和M4应导通,而M2和M3应关断。类似地,如果线圈+为负极,线圈-为正极,则N沟道MOSFET的M2和M3应导通,而M1和M4应关断。这样就构成一个整流循环,在M1和M4打开与M2和M3闭合之间或M2和M3打开与M1和M4闭合之间应存在死区时间。这是因为有一个潜在风险,例如,当FPGA发送指令使M1和M4导通时,同时M2和M3也导通并将关断,因此M1和M2将构成一个低阻抗路径。应避免这种情况。需要死区时间以确保M2在M1导通之前关断。在此解决方案中,可在FPGA PWM控制模块中添加死区时间。图4说明了PWM控制模块的时序图。 请注意,“1”指逻辑“H”,“0”指逻辑“L”,FAN7085为负逻辑。

图4:PWM控制模块时序图

4.2 V/I检测和AD控制模块

V/I检测和AD模块负责电压和电流数据采集,这些参数对于FPGA控制模块至关重要。在此解决方案中,10位ADC(U8、U9)、差分放大器(U6)和FAN4931器件(U7)组成V/I检测和AD控制模块。一个20毫欧精密电阻用于检测电流,差分放大器则放大该精密电阻上的压降。例如,将差分放大器设置为100 V/V增益,且ADC的参考电压为2.5 V,因此可检测到的最大电流为1.25 A,并且理论精度小于2 mA。

精密分压电阻R9和R10用于检测整流DC电压Vrec;如果R9=75 K且R10=24.9 K(如原理图中所示),由于ADC的参考电压为2.5 V,因此最大可检测电压为10 V,理论精度小于10 mV。FAN4931器件用作电压跟随器,以实现ADC和电阻分压器之间的阻抗匹配。

ADC、CS和CLK的控制信号来自FPGA控制模块。其输出数据将馈入FPGA,计算模块将利用此数据计算收到的功率,而控制模块将利用此数据作为verilog程序的输入信号。

摘要:

随着无线充电器技术的蓬勃发展,以及越来越多的智能手机用户被各种充电电缆所困扰,方便易用的无线充电器将被普遍接受和采用。尽管目前有三种不同的无线充电器标准,但WPC Qi标准更常用于智能手机应用。本文将介绍基于FPGA解决方案的无线充电器接收器系统的架构。无线充电器接收器严格遵循最新的WPC Qi标准。接收器系统包含一个模拟模块和一个FPGA模块。模拟模块由分立式组件组成,包括全桥整流器模块、V/I检测和AD控制模块以及DC-DC模块。FPGA模块充当数字内核,其内嵌通信模块、控制模块、计算模块和收发器模块。它使用Verilog语言和状态机对FPGA编程。最后,通过测试和验证,无线充电器接收器在多个主要OEM的无线充电器发射器上工作极佳。

1. 背景

随着无线充电器技术的蓬勃发展,以及越来越多的智能手机用户被各种充电电缆所困扰,方便易用的无线充电器将被普遍接受和采用。目前有三种不同的无线充电器标准:WPC (Qi)、PMA和A4WP。WPC Qi标准更常用于智能手机应用。现在,许多智能手机OEM已推出支持WPC标准的无线充电器解决方案。本文将重点介绍WPC标准的无线充电器接收器解决方案,及其与基于FPGA的详细系统架构的关系。

2. WPC标准概述

WPC Qi标准提供无线充电器系统的详细说明,包括通信和传输协议。功率始终从充电板传输至移动设备。充电板包含一个称为功率发射器(由主线圈组成)的子系统,而移动设备包含一个称为功率接收器(由次级线圈组成)的子系统。

图1说明了基本系统配置。如图所示,功率发射器由两个主要功能单元组成,即功率转换单元和通信与控制单元。 控制与通信单元将转换的功率调节至功率接收器请求的水平。功率接收器则由一个功率拾取单元和一个通信与控制单元组成。

功率接收器位于手机端,因此接下来将主要介绍功率接收器系统,并说明基于FPGA的无线充电器接收器解决方案。

图1:基本系统配置

3. 基于FPGA的功率接收器系统概述

根据WPC Qi标准,功率接收器系统将包含一个功率拾取单元和一个通信与控制单元。示例中将详细介绍一个完全满足WPC Qi标准要求的接收器解决方案。 图2显示基于FPGA的功率接收器系统的架构。

图2:系统架构

如图2中所示,接收器系统包含两个子系统,一个是模拟模块,另一个是数字模块。模拟模块由分立式器件组成,包括全桥整流器模块、V/I检测和AD控制模块、通信模块和DC-DC模块。数字模块内置在FPGA中,使用Verilog语言编写程序。数字内核模块可分为三个主要子模块: 第一个是通信和PWM控制模块,第二个是计算模块,第三个是Rx和Tx(接收器和发射器)模块。下面更为详细地介绍了这些模块。

4. 模拟模块

次级线圈是模拟模块的供电来源;主线圈和次级线圈组成一个完整的无芯谐振变压器。通过电磁耦合,交变磁场将在次级线圈产生交流电源,然后全桥整流器将交流转换为直流。图3显示部分模拟模块的原理图。

图3:部分模拟模块的原理图

4.1 全桥整流器

在此解决方案中,FAN156 (U10)比较器、FDMA8878(M1、M2、M3、M4)N沟道MOSFET、FAN7085和FAN3180(U2、U3、U4、U5)MOSFET驱动器组成全桥整流器。FAN156器件的输出信号直接馈入FPGA,然后FPGA向全桥整流器提供控制信号H1、L1、H2和L2。

FAN156比较器用于检测线圈两端的极性。如原理图中所示,如果线圈+为正极,线圈-为负极,则FAN156比较器向FPGA提供“H”信号。类似地,如果线圈+为负极,而线圈-为正极,则FAN156比较器向FPGA提供“L”信号。然后PWM控制模块将根据这些输入提供输出。从全桥整流器角度来看,如果线圈+为正极,线圈-为负极,则N沟道MOSFET的M1和M4应导通,而M2和M3应关断。类似地,如果线圈+为负极,线圈-为正极,则N沟道MOSFET的M2和M3应导通,而M1和M4应关断。这样就构成一个整流循环,在M1和M4打开与M2和M3闭合之间或M2和M3打开与M1和M4闭合之间应存在死区时间。这是因为有一个潜在风险,例如,当FPGA发送指令使M1和M4导通时,同时M2和M3也导通并将关断,因此M1和M2将构成一个低阻抗路径。应避免这种情况。需要死区时间以确保M2在M1导通之前关断。在此解决方案中,可在FPGA PWM控制模块中添加死区时间。图4说明了PWM控制模块的时序图。 请注意,“1”指逻辑“H”,“0”指逻辑“L”,FAN7085为负逻辑。

图4:PWM控制模块时序图

4.2 V/I检测和AD控制模块

V/I检测和AD模块负责电压和电流数据采集,这些参数对于FPGA控制模块至关重要。在此解决方案中,10位ADC(U8、U9)、差分放大器(U6)和FAN4931器件(U7)组成V/I检测和AD控制模块。一个20毫欧精密电阻用于检测电流,差分放大器则放大该精密电阻上的压降。例如,将差分放大器设置为100 V/V增益,且ADC的参考电压为2.5 V,因此可检测到的最大电流为1.25 A,并且理论精度小于2 mA。

精密分压电阻R9和R10用于检测整流DC电压Vrec;如果R9=75 K且R10=24.9 K(如原理图中所示),由于ADC的参考电压为2.5 V,因此最大可检测电压为10 V,理论精度小于10 mV。FAN4931器件用作电压跟随器,以实现ADC和电阻分压器之间的阻抗匹配。

ADC、CS和CLK的控制信号来自FPGA控制模块。其输出数据将馈入FPGA,计算模块将利用此数据计算收到的功率,而控制模块将利用此数据作为verilog程序的输入信号。

飞兆 半导体 无线充电 无线充电器 FPGA 收发器 Verilog PWM 变压器 比较器 MOSFET 电压 电流 ADC 放大器 电阻 相关文章:

- 用于低成本高效率离线LED驱动器的初级端调节技术(05-14)

- 通过初级端调节满足充电器能效规范(10-29)

- 大功率LED照明恒流驱动电源的设计(10-15)

- 利用低端栅极驱动器IC进行系统开发(12-21)

- 选择高压场效应管实现节能(06-13)

- 确定功率MOSFET的适用性(07-27)