基于ADSP-BF561的车辆辅助驾驶系统硬件设计

时间:04-04

来源:互联网

点击:

引言

20世纪八十年代以来.电子技术和计算机技术快速发展,汽车行驶安全方面的研究也进入了一个崭新的领域。其发展方向主要体现在智能化的汽车主被动安全研究,其中安全辅助驾驶是当前国际智能交通系统研究的重要内容之一。目前CCD或CMOS摄像机配合性能优良和价格低廉的DSP处理器在车辆安全辅助驾驶领域中的应用也不断增加。其中ADI公司的Blackfin系列处理器基于ADI和Intel公司联合开发的微信号架构(Micro Signal Architecture.MSA).应用于交通标志识别、智能灯光控制、车道变换辅助、盲点识别、后视摄像机和停车辅助、自适应巡航系统(Adaptive Cruise Control,ACCl、夜间辅助驾驶和智能安全气囊等。因此对Black6n系列处理器的硬件开发为整个系统提供良好的研究平台和开发环境。

1 车辆辅助驾驶系统框架设计

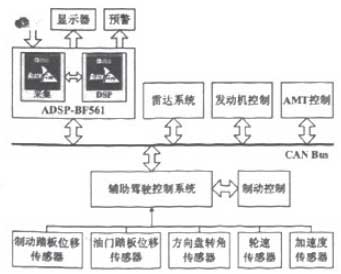

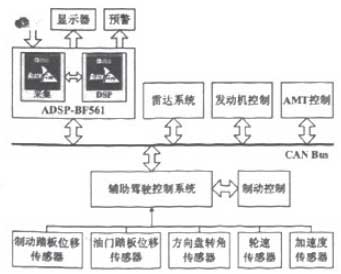

图1系统总体框架

车辆辅助驾驶的主要目的是为了提高汽车行驶的安全性。通过安装在车辆上的各种传感器获得车辆、道路状况以及周围车辆状况等信息.为驾驶员提供有效的预警信号.并在一定的条件下对车辆实施安全控制。系统主要由视觉系统、雷达系统、辅助驾驶控制系统、机械式自动变速控制系统、发动机控制系统、制动控制系统组成,感知车辆状态的传感有制动踏板位移传感器、油门踏板位移传感器、转向角度传感器、车轮转速传感器、加速度传感器,其框架结构如图1所示。

1.1环境感知系统

视觉传感器采用AIR-7010C CCD摄像机.通过ADV7183接入ADSP-BF561并行输入输出外围接口单元进行视频解码,雷达系统采用IBEO公司的LD-ML多层激光雷达系统.经过视觉处理算法后的图像数据与雷达数据进行数据融合.最终得出障碍物的有效信息,并通过CAN总线发送至辅助驾驶控制单元进行策略控制。

1.2底层控制系统

系统通过CAN总线获取有效的车辆行驶状态信息和车辆行驶环境信息,监控车辆的纵向和横向行驶安全,在一定的行驶条件下对车辆纵向行驶进行干预控制。辅助驾驶控制策略单元通过获取环境感知传感器与车辆状态传感器而对发动机转速的控制、机械式自动变速器fAM,I')档位和离合器的控制、制动系统的控制。

2 硬件系统的组成与设计

Blackfin处理器架构基于一个10级RISC MCU/DSP流水线和一个专为实现最佳代码密度而设计的混合16/32位指令集架构.除此之外还包含加速视频和图像处理的指令,因此Blackfin系列的处理器应用于通信、图像、语音等方面,ADSP-BF561是目前Blackfin家族中性能最高的一款处理器,其特点如下:

1)2个对称最高频率可达600MHz的高性能Blackfin内核;

2)每个内核包括2个16位MAC、2个40位ALU、4个8位视频ALU以及1个40位移位器:

3)内核电压0.8V-1.2V,兼容3.3V及2.5V I/O;,

4)328K Bytes片内存储器.每个内核32Kbytes的Ll指令SRAM/Cache、64Kbytes的L1数据SRAM/Cache、4KBytes的L1临时数据SRAM,128Kbytes共享的L2 SRAM:

5)2个并行输入/输出外围接口单元(PPI),支持ITU-R656视频数据格式:2个双通道全双工同步串行接13,支持8个立体声璐通道:2个16通道DMA控制器和1个内部存储器DMA控制器;12个通用32-bit定时肘数器;支持IrDA的UART;2个“看门狗”定时器;48个可编程标志引脚;1x-63x倍频的片内PLL。

2.1电源及复位电路

在设计电源电路时.需要考虑电源的负载能力、可靠性和稳定性。同时需要考虑系统需要多少种电源.ADSP-BF56l外部I/O供电电压为3.3V.内核供电电压为1.2V.因此系统需要+5V、+3.3V、+1.2V.首先通过DC-DC2405把车上的+24v转换成+5V.然后通过LT1765把+5V转换成+3.3V.ADP3336把+3.3v转换成+1.2v。复位电路采用ADM708复位芯片.并在电路中加入手动按钮。实现手动复位功能.方便程序的调试。

2.2时钟电路

有源品振信号质量好、比较稳定、连接简单和不需要复杂的配置电路。因此ADSP-BF561系统输入时钟采用30MHz的外部有源品振然后通过其内部锁相环PLL把频率进行相应的倍频作为ADSP-BF561的总线频率和SDRAM的时钟频率,同时由于并行输入,输出外围接13和视频编解码芯片的时钟需要,需要把27MHz有源晶振通过IDT2305分成4路输出。

2.3存储扩展电路

SDRAM是同步寻址存储器,由块、行和列组成.全部读店操作锁定于一个处理器源时钟,一旦处理器对SDRAM进行初始化。该存储器必须不断更新,以确保能保持它的状态.SDRAM的时钟速率可变,工业上最常用的是PCI00和PCI33,最高时钟频率分别为100MHz和133MHz。ADSP-BF561拥有SDRAM控制器(SDC)与SDRAM的无缝连接,其连接如图2(a)所示,系统采用MT48LCl6M16A2,容量为32MHz,最高频率为133MHz。

ADSP-BF561具有异步存储器控制器(AMc),与SDRAM控制器共享数据和地址引脚。当上电复位或者软件初始化复位后.处理器采样复位配置寄存器BMODE引脚,执行引导功能。系统采用BMODEIO为由8116位Flash引导模式,并选用NORFLASH作为引导代码存储器,所选芯片为容量8MB的M29W640DT.其连接方式如图2(b)所示。

a) SDRAM

b)Flash

图2存储器连接

2.4并行输入/输出外围接口电路

ADSP-BF561提供两个可直接与并行A/D和D/A转换器、符合ITU-601/656标准的视频编码和解码器以及与其他通用外设连接的并行接13(PPI),每个PPI包括一个专用时钟引脚,由时钟电路产生。3个帧同步引脚和16个数据引脚。通过视频解码器ADV7183与ADSP-BF561的PPl0连接.视频编码器ADV7179与ADSP-BF561的PPll连接.从而实现车辆辅助驾驶系统中的环境感知传感和人机界面功能.其连接如图3所示。

图3并行输入/输出连接

2.5 CAN接口电路

CAN(Controller Area Network)总线,即控制器局域网总线.是一种有效支持分布式控制或实时控制的串行通信网络.目前已广泛用于汽车等控制领域。利用ADSP-BF561处理器串行SPI总线接口单元与CAN控制器MCP2515芯片的无缝连接.通过对转换芯片内部寄存器的操作.并通过CAN接收器SN65230芯片实现数据的收发。

20世纪八十年代以来.电子技术和计算机技术快速发展,汽车行驶安全方面的研究也进入了一个崭新的领域。其发展方向主要体现在智能化的汽车主被动安全研究,其中安全辅助驾驶是当前国际智能交通系统研究的重要内容之一。目前CCD或CMOS摄像机配合性能优良和价格低廉的DSP处理器在车辆安全辅助驾驶领域中的应用也不断增加。其中ADI公司的Blackfin系列处理器基于ADI和Intel公司联合开发的微信号架构(Micro Signal Architecture.MSA).应用于交通标志识别、智能灯光控制、车道变换辅助、盲点识别、后视摄像机和停车辅助、自适应巡航系统(Adaptive Cruise Control,ACCl、夜间辅助驾驶和智能安全气囊等。因此对Black6n系列处理器的硬件开发为整个系统提供良好的研究平台和开发环境。

1 车辆辅助驾驶系统框架设计

图1系统总体框架

车辆辅助驾驶的主要目的是为了提高汽车行驶的安全性。通过安装在车辆上的各种传感器获得车辆、道路状况以及周围车辆状况等信息.为驾驶员提供有效的预警信号.并在一定的条件下对车辆实施安全控制。系统主要由视觉系统、雷达系统、辅助驾驶控制系统、机械式自动变速控制系统、发动机控制系统、制动控制系统组成,感知车辆状态的传感有制动踏板位移传感器、油门踏板位移传感器、转向角度传感器、车轮转速传感器、加速度传感器,其框架结构如图1所示。

1.1环境感知系统

视觉传感器采用AIR-7010C CCD摄像机.通过ADV7183接入ADSP-BF561并行输入输出外围接口单元进行视频解码,雷达系统采用IBEO公司的LD-ML多层激光雷达系统.经过视觉处理算法后的图像数据与雷达数据进行数据融合.最终得出障碍物的有效信息,并通过CAN总线发送至辅助驾驶控制单元进行策略控制。

1.2底层控制系统

系统通过CAN总线获取有效的车辆行驶状态信息和车辆行驶环境信息,监控车辆的纵向和横向行驶安全,在一定的行驶条件下对车辆纵向行驶进行干预控制。辅助驾驶控制策略单元通过获取环境感知传感器与车辆状态传感器而对发动机转速的控制、机械式自动变速器fAM,I')档位和离合器的控制、制动系统的控制。

2 硬件系统的组成与设计

Blackfin处理器架构基于一个10级RISC MCU/DSP流水线和一个专为实现最佳代码密度而设计的混合16/32位指令集架构.除此之外还包含加速视频和图像处理的指令,因此Blackfin系列的处理器应用于通信、图像、语音等方面,ADSP-BF561是目前Blackfin家族中性能最高的一款处理器,其特点如下:

1)2个对称最高频率可达600MHz的高性能Blackfin内核;

2)每个内核包括2个16位MAC、2个40位ALU、4个8位视频ALU以及1个40位移位器:

3)内核电压0.8V-1.2V,兼容3.3V及2.5V I/O;,

4)328K Bytes片内存储器.每个内核32Kbytes的Ll指令SRAM/Cache、64Kbytes的L1数据SRAM/Cache、4KBytes的L1临时数据SRAM,128Kbytes共享的L2 SRAM:

5)2个并行输入/输出外围接口单元(PPI),支持ITU-R656视频数据格式:2个双通道全双工同步串行接13,支持8个立体声璐通道:2个16通道DMA控制器和1个内部存储器DMA控制器;12个通用32-bit定时肘数器;支持IrDA的UART;2个“看门狗”定时器;48个可编程标志引脚;1x-63x倍频的片内PLL。

2.1电源及复位电路

在设计电源电路时.需要考虑电源的负载能力、可靠性和稳定性。同时需要考虑系统需要多少种电源.ADSP-BF56l外部I/O供电电压为3.3V.内核供电电压为1.2V.因此系统需要+5V、+3.3V、+1.2V.首先通过DC-DC2405把车上的+24v转换成+5V.然后通过LT1765把+5V转换成+3.3V.ADP3336把+3.3v转换成+1.2v。复位电路采用ADM708复位芯片.并在电路中加入手动按钮。实现手动复位功能.方便程序的调试。

2.2时钟电路

有源品振信号质量好、比较稳定、连接简单和不需要复杂的配置电路。因此ADSP-BF561系统输入时钟采用30MHz的外部有源品振然后通过其内部锁相环PLL把频率进行相应的倍频作为ADSP-BF561的总线频率和SDRAM的时钟频率,同时由于并行输入,输出外围接13和视频编解码芯片的时钟需要,需要把27MHz有源晶振通过IDT2305分成4路输出。

2.3存储扩展电路

SDRAM是同步寻址存储器,由块、行和列组成.全部读店操作锁定于一个处理器源时钟,一旦处理器对SDRAM进行初始化。该存储器必须不断更新,以确保能保持它的状态.SDRAM的时钟速率可变,工业上最常用的是PCI00和PCI33,最高时钟频率分别为100MHz和133MHz。ADSP-BF561拥有SDRAM控制器(SDC)与SDRAM的无缝连接,其连接如图2(a)所示,系统采用MT48LCl6M16A2,容量为32MHz,最高频率为133MHz。

ADSP-BF561具有异步存储器控制器(AMc),与SDRAM控制器共享数据和地址引脚。当上电复位或者软件初始化复位后.处理器采样复位配置寄存器BMODE引脚,执行引导功能。系统采用BMODEIO为由8116位Flash引导模式,并选用NORFLASH作为引导代码存储器,所选芯片为容量8MB的M29W640DT.其连接方式如图2(b)所示。

a) SDRAM

b)Flash

图2存储器连接

2.4并行输入/输出外围接口电路

ADSP-BF561提供两个可直接与并行A/D和D/A转换器、符合ITU-601/656标准的视频编码和解码器以及与其他通用外设连接的并行接13(PPI),每个PPI包括一个专用时钟引脚,由时钟电路产生。3个帧同步引脚和16个数据引脚。通过视频解码器ADV7183与ADSP-BF561的PPl0连接.视频编码器ADV7179与ADSP-BF561的PPll连接.从而实现车辆辅助驾驶系统中的环境感知传感和人机界面功能.其连接如图3所示。

图3并行输入/输出连接

2.5 CAN接口电路

CAN(Controller Area Network)总线,即控制器局域网总线.是一种有效支持分布式控制或实时控制的串行通信网络.目前已广泛用于汽车等控制领域。利用ADSP-BF561处理器串行SPI总线接口单元与CAN控制器MCP2515芯片的无缝连接.通过对转换芯片内部寄存器的操作.并通过CAN接收器SN65230芯片实现数据的收发。

电子 CMOS DSP ADI 传感器 总线 CAN总线 MCU 电压 看门狗 电路 IDT 解码器 编码器 嵌入式 相关文章:

- 电子技术的革新先锋(11-21)

- ispMACH4000Z CPLD在消费类电子产品中的应用(01-24)

- 现代汽车电子技术综述(06-24)

- 新技术、新应用让传感器深入汽车电子设备的各个角落(05-11)

- RFID技术在商用汽车生产及使用中的应用(05-11)

- 模糊控制在汽车离合器中的应用(05-11)