利用数字隔离器技术增强工业电机控制性能

时间:11-25

来源:互联网

点击:

摘要:本文介绍了数字隔离器技术,来增强工业电机控制性能并对其进行分类,介绍了隔离方法、进行了延迟特性比较,缝隙数字隔离器技术对电子控制系统的系统影响,给出应用实例,予以工程师参考。

1 隔离类型简介

隔离用户和敏感的电子部件是电机控制系统的重要考虑事项。安全隔离用于保护用户免受有害电压影响,功能隔离则专门用来保护设备和器件。电机控制系统可能包含各种各样的隔离器件,例如:驱动电路中的隔离式栅极驱动器;检测电路中的隔离式ADC、放大器和传感器;以及通信电路中的隔离式SPI、RS-485、标准数字隔离器。无论是出于安全原因,还是为了优化性能,都要求精心选择这些器件。

虽然隔离是很重要的系统考虑,但它也存在缺点:会提高功耗,跨过隔离栅传输数据会产生延迟,而且会增加系统成本。传统上系统设计师求助于光耦合器解决方案,多年来,它是系统隔离的当然选择。最近十年来,基于磁耦合(变压器传输)方法的数字隔离器提供了一种可行且在很多时候更优越的替代方案;从系统角度考虑,它还具备系统设计师可能尚未认识到的优点。 本文将讨论这两种隔离解决方案,重点论述磁隔离对延迟时序性能的改善,以及由此给电机控制应用在系统层面带来的好处。

2 隔离方法

光耦合器利用光作为主要传输方法,如图1所示。 发送侧包括一个LED,高电平信号开启LED,低电平信号关闭LED。 接收侧利用光电检测器将接收到的光信号转换回电信号。 隔离由LED与光电检测器之间的塑封材料提供,但也可利用额外的隔离层(通常基于聚合物)予以增强。

光耦合器的最大缺点之一是:随着LED老化,其辐射特性会漂移,设计人员必须考虑这一额外问题。 LED退化导致时序性能随着时间和温度而漂移。因此,传播和上升/下降时间会受影响,使设计复杂化,尤其是考虑到本文后面要处理的问题。

光耦合器的性能扩展性也会受到影响。为了提高数据速率,必须克服光耦合器固有的寄生电容问题,该问题会导致功耗升高。寄生电容还会提供耦合机制,导致基于光耦合的隔离器的CMTI(共模瞬变抗扰度)性能劣于竞争对手。

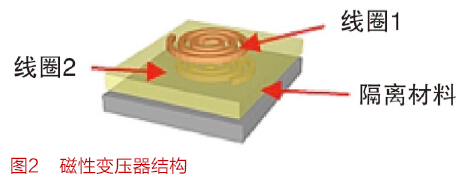

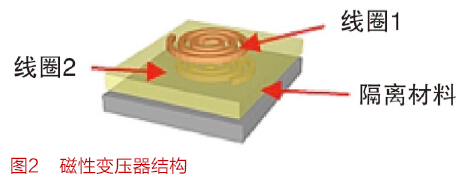

磁隔离器(基于变压器)已大规模应用十多年,是光耦合器的有效替代方案。这类隔离器基于标准CMOS技术,采用磁耦合传输方案,隔离层由聚酰亚胺或二氧化硅构成,如图2所示。以低电流脉冲方式通过线圈传输,产生一个磁场,磁场穿过隔离栅,在隔离栅另一侧的第二线圈中感生一个电流。 由于采用标准CMOS结构,其在功耗和速度方面具有明显优势,而且不存在光耦合器相关的寿命偏差问题。 此外,由于基于变压器的隔离器中存在较低的寄生电容,它们的CMTI性能优于基于光耦合器的隔离器。

基于变压器的隔离器还允许使用常见处理模块(防止杂散输入信号)和高级传输编解码机制。 这样就可以实现双向数据传输,使用不同编码方案来优化功耗与传输速率的关系,以及后文提到的将重要信号更快速、更一致地传输到隔离栅另一端。

3 延迟特性比较

所有隔离器都有一个非常重要但常常被轻视的特性是其传播延迟。此特性衡量信号(可以是驱动信号或故障检测信号)沿任一方向跨过隔离栅所需的时间。 技术不同,传播延迟差别很大。 通常提供的是典型延迟值,但系统设计师特别关注最大延迟,它是设计电机控制系统需要考虑的重要特性。表1给出了光耦合器和磁隔离栅极驱动器的传播延迟和延迟偏斜值示例。

如表1所示,磁隔离在最大延迟和延迟可重复性(偏斜)方面优势明显。这样,电机控制设计人员对设计将更有信心,无需增加时序裕量以满足栅极驱动器特性。对于电机控制系统的性能和安全,这都有着非常重要的意义。

4 对电机控制系统的系统影响

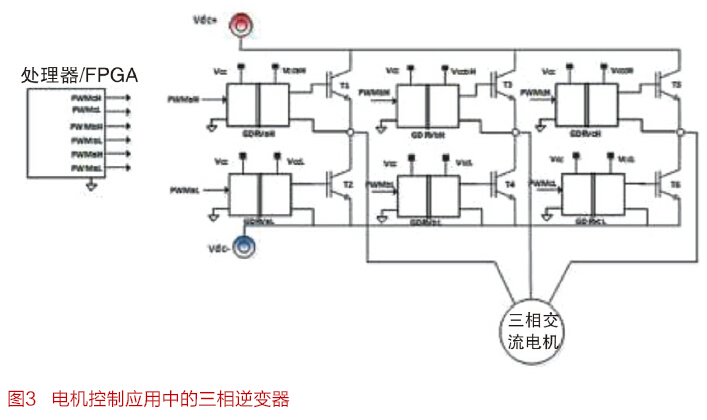

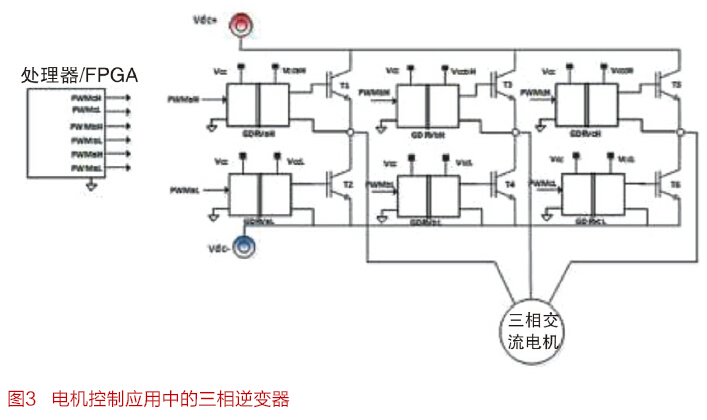

图3显示了交流电机控制应用中采用的典型三相逆变器。 该逆变器由直流总线供电,直流电源通常是通过二极管桥式整流器和容性/感性-容性滤波器直接从交流电源产生。在大部分工业应用中,直流总线电压在300V至1,000V范围内。采用脉宽调制(PWM)方案,以5kHz至10 kHz的频率切换功率晶体管T1至T6,从而在电机端子上产生可变电压、可变频率的三相正弦交流电压。

PWM信号(如PWMaH和PWMaL)在电机控制器(一般用处理器和/或FPGA实现)中产生。 这些信号一般是低压信号,参考处理器接地轨。为了正确开启和关闭功率晶体管,逻辑电平信号的电压电平和电流源能力必须放大,另外还必须进行电平转换,从而以相关功率晶体管发射极为接地基准。 根据处理器在系统中的位置,这些信号可能还需要安全绝缘。

这些功能由栅极驱动器执行(比如GDRVaL/GDRVaH等,如图3所示)。每个栅极驱动器IC都需要一个以处理器地为基准的原边电源电压和一个以晶体管发射极为基准的副边电源。副边电源的电压电平必须能够开启功率晶体管(通常为15V),并有足够的电流驱动能力来给晶体管栅极充电和放电。

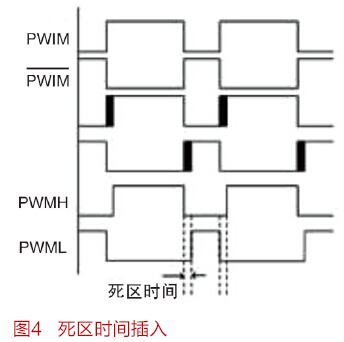

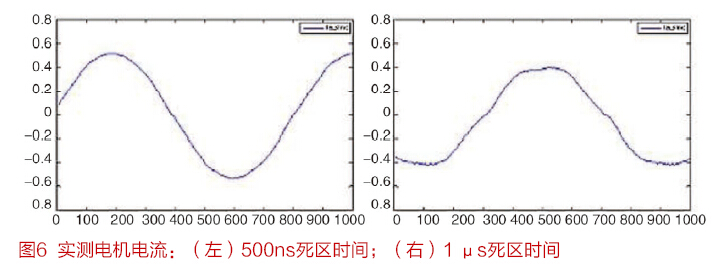

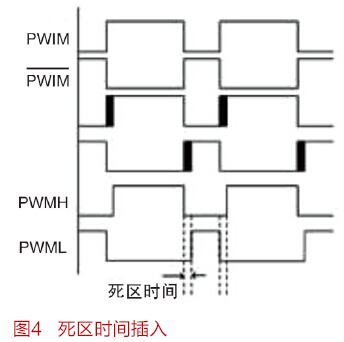

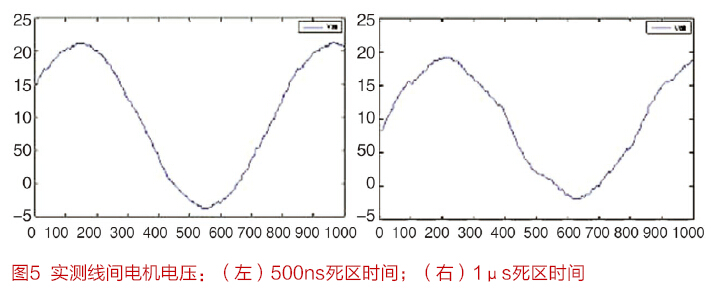

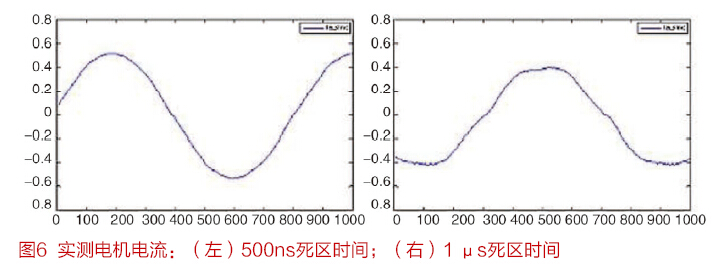

功率晶体管有一个有限的开关时间,因此,高端和低端晶体管之间的脉宽调制波形中必须插入一个消隐或死区时间,如图4所示。 这是为了防止两个晶体管意外同时打开,引起高压直流总线短路,进而造成系统故障和/或损坏风险。 死区时间的长度由两个因素决定:晶体管开关时间和栅极驱动器传播延迟失配(包括失配的任何漂移)。换言之,死区时间必须考虑PWM信号从处理器到高端和低端栅极驱动器之间的晶体管栅极的任何传播时间差异。

死区时间的作用是扭曲施加于电机的平均电压,尤其是在低速运转时。实际上,死区时间会带来以下近似恒定幅度的误差电压:

其中,Verror为误差电压,tdead为死区时间,ton和toff为晶体管开启和关闭延迟时间,TS为PWM开关周期,Vdc为直流总线电压,Vsat为功率晶体管的导通状态压降,Vd为二极管导通电压。

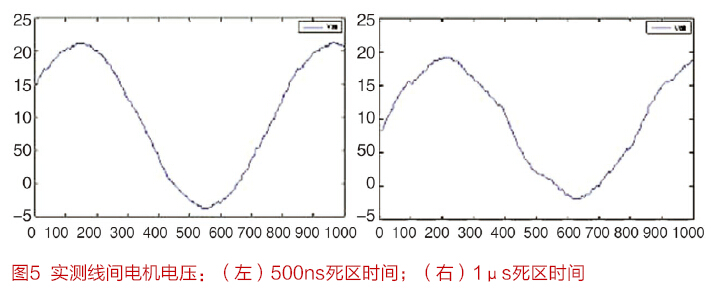

当一个相位段中的电流改变方向时,误差电压改变符号,因此,当线路电流过零时,电机线间电压发生阶跃变化。这会引起正弦基波电压的谐波,进而在电机中产生谐波电流。对于开环驱动采用的较大低阻抗电机,这是一个特别重要的问题,因为谐波电流可能很大,导致低速振动、扭矩纹波和谐波加热。

在以下条件下,死区时间对电机输出电压失真的影响最严重:

● 高直流总线电压 ;

● 长死区时间 ;

● 高开关频率 ;

● 低速工作,特别是在控制算法未添加任何补偿的开环驱动中 。

低速工作很重要,因为正是在这种模式下,施加的电机电压在任何情况下都非常低,死区时间导致的误差电压可能是所施加电机电压的很大一部分。此外,低速下感应扭矩纹波的影响更有害,因为对系统惯性的滤波在较高速度下是不可用。

在所有这些参数中,死区时间长度是唯一受隔离式栅极驱动器技术影响的参数。死区时间长度的一部分是由功率晶体管的开关延迟时间决定的,但其余部分与传播延迟失配有关。 在这方面,光隔离器显然不如磁隔离技术。

1 隔离类型简介

隔离用户和敏感的电子部件是电机控制系统的重要考虑事项。安全隔离用于保护用户免受有害电压影响,功能隔离则专门用来保护设备和器件。电机控制系统可能包含各种各样的隔离器件,例如:驱动电路中的隔离式栅极驱动器;检测电路中的隔离式ADC、放大器和传感器;以及通信电路中的隔离式SPI、RS-485、标准数字隔离器。无论是出于安全原因,还是为了优化性能,都要求精心选择这些器件。

虽然隔离是很重要的系统考虑,但它也存在缺点:会提高功耗,跨过隔离栅传输数据会产生延迟,而且会增加系统成本。传统上系统设计师求助于光耦合器解决方案,多年来,它是系统隔离的当然选择。最近十年来,基于磁耦合(变压器传输)方法的数字隔离器提供了一种可行且在很多时候更优越的替代方案;从系统角度考虑,它还具备系统设计师可能尚未认识到的优点。 本文将讨论这两种隔离解决方案,重点论述磁隔离对延迟时序性能的改善,以及由此给电机控制应用在系统层面带来的好处。

2 隔离方法

光耦合器利用光作为主要传输方法,如图1所示。 发送侧包括一个LED,高电平信号开启LED,低电平信号关闭LED。 接收侧利用光电检测器将接收到的光信号转换回电信号。 隔离由LED与光电检测器之间的塑封材料提供,但也可利用额外的隔离层(通常基于聚合物)予以增强。

光耦合器的最大缺点之一是:随着LED老化,其辐射特性会漂移,设计人员必须考虑这一额外问题。 LED退化导致时序性能随着时间和温度而漂移。因此,传播和上升/下降时间会受影响,使设计复杂化,尤其是考虑到本文后面要处理的问题。

光耦合器的性能扩展性也会受到影响。为了提高数据速率,必须克服光耦合器固有的寄生电容问题,该问题会导致功耗升高。寄生电容还会提供耦合机制,导致基于光耦合的隔离器的CMTI(共模瞬变抗扰度)性能劣于竞争对手。

磁隔离器(基于变压器)已大规模应用十多年,是光耦合器的有效替代方案。这类隔离器基于标准CMOS技术,采用磁耦合传输方案,隔离层由聚酰亚胺或二氧化硅构成,如图2所示。以低电流脉冲方式通过线圈传输,产生一个磁场,磁场穿过隔离栅,在隔离栅另一侧的第二线圈中感生一个电流。 由于采用标准CMOS结构,其在功耗和速度方面具有明显优势,而且不存在光耦合器相关的寿命偏差问题。 此外,由于基于变压器的隔离器中存在较低的寄生电容,它们的CMTI性能优于基于光耦合器的隔离器。

基于变压器的隔离器还允许使用常见处理模块(防止杂散输入信号)和高级传输编解码机制。 这样就可以实现双向数据传输,使用不同编码方案来优化功耗与传输速率的关系,以及后文提到的将重要信号更快速、更一致地传输到隔离栅另一端。

3 延迟特性比较

所有隔离器都有一个非常重要但常常被轻视的特性是其传播延迟。此特性衡量信号(可以是驱动信号或故障检测信号)沿任一方向跨过隔离栅所需的时间。 技术不同,传播延迟差别很大。 通常提供的是典型延迟值,但系统设计师特别关注最大延迟,它是设计电机控制系统需要考虑的重要特性。表1给出了光耦合器和磁隔离栅极驱动器的传播延迟和延迟偏斜值示例。

如表1所示,磁隔离在最大延迟和延迟可重复性(偏斜)方面优势明显。这样,电机控制设计人员对设计将更有信心,无需增加时序裕量以满足栅极驱动器特性。对于电机控制系统的性能和安全,这都有着非常重要的意义。

4 对电机控制系统的系统影响

图3显示了交流电机控制应用中采用的典型三相逆变器。 该逆变器由直流总线供电,直流电源通常是通过二极管桥式整流器和容性/感性-容性滤波器直接从交流电源产生。在大部分工业应用中,直流总线电压在300V至1,000V范围内。采用脉宽调制(PWM)方案,以5kHz至10 kHz的频率切换功率晶体管T1至T6,从而在电机端子上产生可变电压、可变频率的三相正弦交流电压。

PWM信号(如PWMaH和PWMaL)在电机控制器(一般用处理器和/或FPGA实现)中产生。 这些信号一般是低压信号,参考处理器接地轨。为了正确开启和关闭功率晶体管,逻辑电平信号的电压电平和电流源能力必须放大,另外还必须进行电平转换,从而以相关功率晶体管发射极为接地基准。 根据处理器在系统中的位置,这些信号可能还需要安全绝缘。

这些功能由栅极驱动器执行(比如GDRVaL/GDRVaH等,如图3所示)。每个栅极驱动器IC都需要一个以处理器地为基准的原边电源电压和一个以晶体管发射极为基准的副边电源。副边电源的电压电平必须能够开启功率晶体管(通常为15V),并有足够的电流驱动能力来给晶体管栅极充电和放电。

功率晶体管有一个有限的开关时间,因此,高端和低端晶体管之间的脉宽调制波形中必须插入一个消隐或死区时间,如图4所示。 这是为了防止两个晶体管意外同时打开,引起高压直流总线短路,进而造成系统故障和/或损坏风险。 死区时间的长度由两个因素决定:晶体管开关时间和栅极驱动器传播延迟失配(包括失配的任何漂移)。换言之,死区时间必须考虑PWM信号从处理器到高端和低端栅极驱动器之间的晶体管栅极的任何传播时间差异。

死区时间的作用是扭曲施加于电机的平均电压,尤其是在低速运转时。实际上,死区时间会带来以下近似恒定幅度的误差电压:

其中,Verror为误差电压,tdead为死区时间,ton和toff为晶体管开启和关闭延迟时间,TS为PWM开关周期,Vdc为直流总线电压,Vsat为功率晶体管的导通状态压降,Vd为二极管导通电压。

当一个相位段中的电流改变方向时,误差电压改变符号,因此,当线路电流过零时,电机线间电压发生阶跃变化。这会引起正弦基波电压的谐波,进而在电机中产生谐波电流。对于开环驱动采用的较大低阻抗电机,这是一个特别重要的问题,因为谐波电流可能很大,导致低速振动、扭矩纹波和谐波加热。

在以下条件下,死区时间对电机输出电压失真的影响最严重:

● 高直流总线电压 ;

● 长死区时间 ;

● 高开关频率 ;

● 低速工作,特别是在控制算法未添加任何补偿的开环驱动中 。

低速工作很重要,因为正是在这种模式下,施加的电机电压在任何情况下都非常低,死区时间导致的误差电压可能是所施加电机电压的很大一部分。此外,低速下感应扭矩纹波的影响更有害,因为对系统惯性的滤波在较高速度下是不可用。

在所有这些参数中,死区时间长度是唯一受隔离式栅极驱动器技术影响的参数。死区时间长度的一部分是由功率晶体管的开关延迟时间决定的,但其余部分与传播延迟失配有关。 在这方面,光隔离器显然不如磁隔离技术。

电子 电压 电路 ADC 放大器 传感器 变压器 LED 电容 CMOS 电流 逆变器 总线 二极管 滤波器 PWM FPGA ADI IGBT 电阻 DSP 相关文章:

- 一种新型防伪读码器的设计(01-01)

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 航天器DC/DC变换器的可靠性设计(02-12)

- 我国科学家人脸与笔迹识别领域获突破(04-29)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于nRF2401智能小区无线抄表系统集中器设计(04-30)