一种新型防伪读码器的设计

时间:01-01

来源:互联网

点击:

假冒伪劣商品一直是世界的公害,随着仿造技术水平的不断提高,被仿造产品的范围也越来越大,仿造品的数量也日趋惊人,小到一粒药片,大到飞机、汽车零部件,几乎所有正牌、名牌产品,都被假冒行为所困扰,假货充斥着大部分的市场。而且造假者不但仿造产品更有甚至仿造正品的防伪标志,对于这样的假冒伪劣产品只有少数的质量专业人员才能辨认,消费者根本无法辨认产品的真伪,从而导致上当受骗,同时企业也遭受了很大的损失,危及名优企业生存发展。针对众多的造假现象,生产厂家也采取了不同的防伪措施,目前市场上的防伪手段大致包括:视觉防伪技术、电子识别防伪技术、数码防伪技术等。在分析当前数码防伪系统存在的不足的基础上,本文提出了一种新型的数码防伪系统。

防伪读码器的总体设计方案

1 总体设计方案

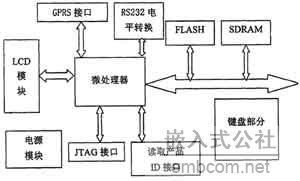

本设计所实现的硬件平台主要由微处理器单元、存储器单元、串口电平转换、液晶显示模块、电源单元和JTAG接口单元组成,硬件功能框图如图1所示。其中串口有两种功能,一种是与上位机进行通信,通过它可以在线下载程序;另一种功能是与GPRS模块进行数据交换。读码器提供的GPRS网络接口中除了包括串口的数据线外,还包括电源线和控制线。

2 系统工作原理

读码器是系统的核心部分,由产品经销商持有,它是产品生产厂家分配给经销商的,作用是读取产品中的信息(即产品出厂时由厂家分配的ID号),然后连接并登陆远端的企业数据库进行查询验证。连接网络时必须通过身份验证,验证通过才允许登录,否则拒绝登陆。对于读码器,厂家亲自将预先选定的密钥存放在其中,这一部分对外界是完全保密的。验证时,将读码器与产品包装上的接口连接,按照事先设定好的通信协议读出其中的信息,存放在读码器中。此时需要进行网络查询,在进行查询前必须通过身份验证登陆查询网站。首先,由读码器发送登陆请求,服务器接到请求后发送一个随机的数据串回来,读码器使用自己的密钥对其进行加密,然后将这段密文发送回去。服务器收到以后,先是解密验证,如果是自己发送过去的原数据,则通过验证,允许登录,否则提示“密钥错误,登陆失败”。成功登陆以后,读码器将产品序列号的密文发送给服务器,由服务器解密并恢复编码并进行查询,若查询失败,则返回提示:“该产品并非是XX企业生产的正品,谨防假冒!”否则,将以密文的形式返回产品的验证信息,由读码器进行解密并显示提示信息,该信息包括:产品的物流渠道、厂家、生产信息等。此时,读码器正处于等待状态,如果产品成功出售,通过按键向服务器返回相关提示信息,由服务器记录下来该信息,即产品出售的时间和地点,以备二次查询;如果没有成功出售则通过不同的按键发送信息,提示服务器“该产品没有卖出”。至此,验证完毕。

防伪读码器的设计与实现

1 存储器设计

微处理器S3C44BOX的存储控制器可以为片外存储器访问提供必要的控制信号。每个地址空间的数据总线宽度是可以通过编程或引脚连接来配置的,由于系统上电启动或复位后总是从0X00000000地址开始执行,Boo映射后的地址就是0X00000000,所以必须在第一次访问ROM前设置Bank0的数据总线宽度。系统中将OM0通过上拉电阻与VDD相连接,OM1通过下拉电阻与GND相连接,即Bank0选用的是16位的数据总线宽度。

除了Bank0以外的其他地址空间可以在系统的启动代码中通过编程予以设置,具体是通过设置存储器控制专用寄存器BWSCON来实现的。存储器控制专用寄存器包括总线宽度/等待控制寄存器、Bank控制寄存器、刷新控制寄存器、Bank大小控制寄存器和模式寄存器设置寄存器,各个寄存器的每一数据位的具体含义请参考数据手册。

根据所选择的Flash和SDRAM,系统各地址空间的数据总线宽度都设置为16位,存储模式为小端模式,不使用等待状态,不使用UB/LB。

2 串口设计

ARMS3C44BOX的UART单元带两个异步串行口,皆可工作于中断和DMA模式,各带有16字节的FIFO。最大波特率115.2K。DART单元包括可编程波特率、红外发送/接收、1个或2个停止位、5/6/7/8位数据宽度和奇偶校验位。每个DART有7种状态:溢出错误、校验错误、帧错误、暂停态、接收缓冲区准备好、发送缓冲区空、发送移位缓冲器空等,这些状态可以由相应的UTRSTATn/UERSTATn表示,并且与发送接收缓冲区相对应的有错误缓冲区。波特率可以通过控制波特率寄存器进行设置。每一个DART的波特率发生器为收/发器提供一个连续时钟,时钟源可选为S3C44BOX的内部系统时钟。波特率的时钟通过一个16位分频器分频后产生,16位分频器的值由寄存器UBRdivn寄存器具体说明。

根据系统功能的需要,读码器在调试过程中需要与PC进行通信,所以需要在微处理器和PC之间设计电平转换电路。另外,系统与存放产品功号的芯片需要进行通信,这里不需要电平转换,系统在GPRS接口中直接将串口线引出,其中的部分引脚即可作为与存储芯片连接的接口,连接电路如图2所示。

防伪读码器的总体设计方案

1 总体设计方案

本设计所实现的硬件平台主要由微处理器单元、存储器单元、串口电平转换、液晶显示模块、电源单元和JTAG接口单元组成,硬件功能框图如图1所示。其中串口有两种功能,一种是与上位机进行通信,通过它可以在线下载程序;另一种功能是与GPRS模块进行数据交换。读码器提供的GPRS网络接口中除了包括串口的数据线外,还包括电源线和控制线。

图1 系统原理框图

2 系统工作原理

读码器是系统的核心部分,由产品经销商持有,它是产品生产厂家分配给经销商的,作用是读取产品中的信息(即产品出厂时由厂家分配的ID号),然后连接并登陆远端的企业数据库进行查询验证。连接网络时必须通过身份验证,验证通过才允许登录,否则拒绝登陆。对于读码器,厂家亲自将预先选定的密钥存放在其中,这一部分对外界是完全保密的。验证时,将读码器与产品包装上的接口连接,按照事先设定好的通信协议读出其中的信息,存放在读码器中。此时需要进行网络查询,在进行查询前必须通过身份验证登陆查询网站。首先,由读码器发送登陆请求,服务器接到请求后发送一个随机的数据串回来,读码器使用自己的密钥对其进行加密,然后将这段密文发送回去。服务器收到以后,先是解密验证,如果是自己发送过去的原数据,则通过验证,允许登录,否则提示“密钥错误,登陆失败”。成功登陆以后,读码器将产品序列号的密文发送给服务器,由服务器解密并恢复编码并进行查询,若查询失败,则返回提示:“该产品并非是XX企业生产的正品,谨防假冒!”否则,将以密文的形式返回产品的验证信息,由读码器进行解密并显示提示信息,该信息包括:产品的物流渠道、厂家、生产信息等。此时,读码器正处于等待状态,如果产品成功出售,通过按键向服务器返回相关提示信息,由服务器记录下来该信息,即产品出售的时间和地点,以备二次查询;如果没有成功出售则通过不同的按键发送信息,提示服务器“该产品没有卖出”。至此,验证完毕。

防伪读码器的设计与实现

1 存储器设计

微处理器S3C44BOX的存储控制器可以为片外存储器访问提供必要的控制信号。每个地址空间的数据总线宽度是可以通过编程或引脚连接来配置的,由于系统上电启动或复位后总是从0X00000000地址开始执行,Boo映射后的地址就是0X00000000,所以必须在第一次访问ROM前设置Bank0的数据总线宽度。系统中将OM0通过上拉电阻与VDD相连接,OM1通过下拉电阻与GND相连接,即Bank0选用的是16位的数据总线宽度。

除了Bank0以外的其他地址空间可以在系统的启动代码中通过编程予以设置,具体是通过设置存储器控制专用寄存器BWSCON来实现的。存储器控制专用寄存器包括总线宽度/等待控制寄存器、Bank控制寄存器、刷新控制寄存器、Bank大小控制寄存器和模式寄存器设置寄存器,各个寄存器的每一数据位的具体含义请参考数据手册。

根据所选择的Flash和SDRAM,系统各地址空间的数据总线宽度都设置为16位,存储模式为小端模式,不使用等待状态,不使用UB/LB。

2 串口设计

ARMS3C44BOX的UART单元带两个异步串行口,皆可工作于中断和DMA模式,各带有16字节的FIFO。最大波特率115.2K。DART单元包括可编程波特率、红外发送/接收、1个或2个停止位、5/6/7/8位数据宽度和奇偶校验位。每个DART有7种状态:溢出错误、校验错误、帧错误、暂停态、接收缓冲区准备好、发送缓冲区空、发送移位缓冲器空等,这些状态可以由相应的UTRSTATn/UERSTATn表示,并且与发送接收缓冲区相对应的有错误缓冲区。波特率可以通过控制波特率寄存器进行设置。每一个DART的波特率发生器为收/发器提供一个连续时钟,时钟源可选为S3C44BOX的内部系统时钟。波特率的时钟通过一个16位分频器分频后产生,16位分频器的值由寄存器UBRdivn寄存器具体说明。

根据系统功能的需要,读码器在调试过程中需要与PC进行通信,所以需要在微处理器和PC之间设计电平转换电路。另外,系统与存放产品功号的芯片需要进行通信,这里不需要电平转换,系统在GPRS接口中直接将串口线引出,其中的部分引脚即可作为与存储芯片连接的接口,连接电路如图2所示。

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 航天器DC/DC变换器的可靠性设计(02-12)

- 我国科学家人脸与笔迹识别领域获突破(04-29)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于nRF2401智能小区无线抄表系统集中器设计(04-30)

- 新型锁相环芯片全面提升红外无线麦克风产品性能(05-04)