混合仿真下DDS的改进研究与实现

时间:07-30

来源:互联网

点击:

据等间隔采样提取

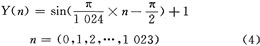

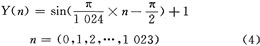

波形存储器调用LPM_ROM元件实现。为了得到1 024个10位正弦波的半周期无符号幅值样点数据,并生成相应的存储器初始化文件(*.mif文件),需要把正弦波波形移至x轴上方后进行采样。采样公式为:

在QuartusⅡ6.0软件中对DDS进行波形仿真后,把仿真结果保存为含有时间和对应样点数据的*.tbl文件。然后在VC中,依据tbl文件的存储格式,编程实现对时间和样点数据的分离提取。

尽管QuartusⅡ6.0是一款十分优秀的EDA(Elec-tronic Design Automation,电子设计自动化)开发工具,但是其仿真结果直观性差,有必要借助第三方工具来观察验证仿真结果。而且可以利用第三方工具来仿真DAC以及LPF。在本系统中,选择了信号处理函数库极其丰富、可视性很强的虚拟仪器开发平台LabWindows/CVI 8.0。

由于QuartusⅡ6.0仿真生成的tbl文件中的仿真数据在时间上并不是等间隔的,因此在LabWindows中进行滤波处理之前,必须对仿真数据进行等间隔采样。等间隔采样的方法是“递进式查找法”,采样原则是每个周期采样512个点。

4 仿真结果与分析

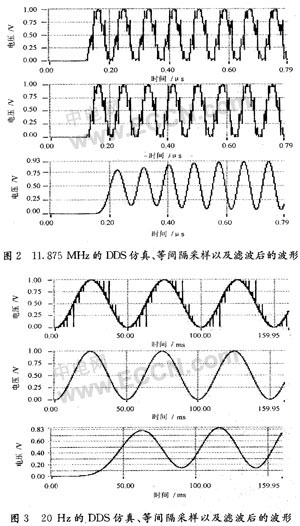

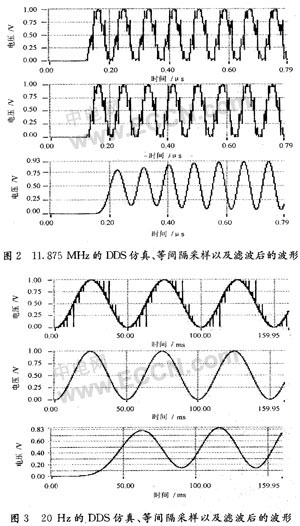

在LabWindows 8.0中使用他的高级信号分析库中的五阶切比雪夫低通滤波器函数对等间隔采样后的样点数据进行滤波,便可得到图2(11.875 MHz的DDS仿真,等间隔采样以及滤波后的波形)、图3(20 Hz的DDS仿真,等间隔采样以及滤波后的波形)的仿真结果。

由图2、图3中DDS的仿真波形中存在大量的毛刺,这主要是由于多位的波形数据传输到FPGA的管脚时存在微小的时间误差造成的,属正常现象。这可以通过后面的滤波电路消除,而图中的滤波后的波形也十分理想。图2、图3中的电压值只是归一化的电压。

5 结 语

文中详细描述了基于QuartusⅡ6.0,VC 6.0和Lab-Windows/CVI 8.0混合仿真环境下设计并实现一个改进的DDS系统的方法和过程,这个数字系统设计的特点就是设计完全避免了硬件平台的限制,同时提升了系统硬件实现的成功率。另外系统中回旋相位累加器的引入把ROM空间的开销降低50%,分辨率提升1倍。

但是,由于DDS内部的波形存储器ROM工作速度的限制,使得DDS输出的最高频率有限。而DDS的全数字结构也不可避免地引入了杂散,主要来源有:回旋相位累加器的截尾误差造成的杂散、幅度量化误差造成的杂散和DAC非理想特性造成的杂散。但是,通过滤波处理完全可以把这些杂散对波形的影响降到最低。

波形存储器调用LPM_ROM元件实现。为了得到1 024个10位正弦波的半周期无符号幅值样点数据,并生成相应的存储器初始化文件(*.mif文件),需要把正弦波波形移至x轴上方后进行采样。采样公式为:

在QuartusⅡ6.0软件中对DDS进行波形仿真后,把仿真结果保存为含有时间和对应样点数据的*.tbl文件。然后在VC中,依据tbl文件的存储格式,编程实现对时间和样点数据的分离提取。

尽管QuartusⅡ6.0是一款十分优秀的EDA(Elec-tronic Design Automation,电子设计自动化)开发工具,但是其仿真结果直观性差,有必要借助第三方工具来观察验证仿真结果。而且可以利用第三方工具来仿真DAC以及LPF。在本系统中,选择了信号处理函数库极其丰富、可视性很强的虚拟仪器开发平台LabWindows/CVI 8.0。

由于QuartusⅡ6.0仿真生成的tbl文件中的仿真数据在时间上并不是等间隔的,因此在LabWindows中进行滤波处理之前,必须对仿真数据进行等间隔采样。等间隔采样的方法是“递进式查找法”,采样原则是每个周期采样512个点。

4 仿真结果与分析

在LabWindows 8.0中使用他的高级信号分析库中的五阶切比雪夫低通滤波器函数对等间隔采样后的样点数据进行滤波,便可得到图2(11.875 MHz的DDS仿真,等间隔采样以及滤波后的波形)、图3(20 Hz的DDS仿真,等间隔采样以及滤波后的波形)的仿真结果。

由图2、图3中DDS的仿真波形中存在大量的毛刺,这主要是由于多位的波形数据传输到FPGA的管脚时存在微小的时间误差造成的,属正常现象。这可以通过后面的滤波电路消除,而图中的滤波后的波形也十分理想。图2、图3中的电压值只是归一化的电压。

5 结 语

文中详细描述了基于QuartusⅡ6.0,VC 6.0和Lab-Windows/CVI 8.0混合仿真环境下设计并实现一个改进的DDS系统的方法和过程,这个数字系统设计的特点就是设计完全避免了硬件平台的限制,同时提升了系统硬件实现的成功率。另外系统中回旋相位累加器的引入把ROM空间的开销降低50%,分辨率提升1倍。

但是,由于DDS内部的波形存储器ROM工作速度的限制,使得DDS输出的最高频率有限。而DDS的全数字结构也不可避免地引入了杂散,主要来源有:回旋相位累加器的截尾误差造成的杂散、幅度量化误差造成的杂散和DAC非理想特性造成的杂散。但是,通过滤波处理完全可以把这些杂散对波形的影响降到最低。

FPGA 电路 Quartus 仿真 DAC 滤波器 EDA 电子 自动化 虚拟仪器 低通滤波器 电压 相关文章:

- 基于FPGA安全封装的身份认证模型研究(05-27)

- ARM在数字化远程视频监控系统的应用(05-20)

- FPGA在弹上信息处理机中的应用(04-15)

- 如何充满信心地设计军用SDR产品(07-25)

- 关于安防应用中图像处理难点分析及处理器选择(07-14)

- 基于 SoPC 的震动信号采集设备设计(08-14)