基于 SoPC 的震动信号采集设备设计

时间:08-14

来源:互联网

点击:

在工程结构测试和分析中,震动信号的采集是一项基础性的工作,其采集的速度、精度和稳定度对测试的结果分析有重要的意义。震动数据分析技术的不断提高要求速度更快、精度更高、功能更强、成本更低的数据采集系统。AD7329恰好满足这些要求,它集成了可编程输入范围切换矩阵、高精度基准源和高性能 A/D转换单元于一体,而Nios Ⅱ嵌入式软核CPU具有数据吞吐率高、配置灵活、可升级性强等特点,是一款性价比很高的微控制器,结合两者并通过高速SPI总线进行通信,构成了高速、高精度震动信号采集设备。

SoPC与Nios Ⅱ嵌入式系统简介

SoPC(System On Programmable Chip,可编程的片上系统)是Altera公司提出来的一种灵活、高效的SoC解决方案。它将处理器、存储器、I/O口等系统设计需要的功能模块集成到一个可编程器件上,构成一个可编程的片上系统。SoPC是PLD和ASIC技术融合的结果,可以认为SoPC代表了半导体产业未来的发展方向。

Nios Ⅱ系列32位RISC嵌入式处理器具有超过200DMIP的性能,在低成本FPGA中实现成本只有35美分。由于处理器是软核形式,具有很大的灵活性,可以在多种系统设置组合中进行选择,满足成本和功能要求。采用Nios Ⅱ处理器进行设计,可以帮助用户将产品迅速推向市场,延长产品生命周期,防止出现处理器逐渐过时的情况。

AD7329模/数转换器

AD7329是ADI公司推出的基于iCMOS(industrial CMOS)工艺的8通道12位精度1MSa/s采样速度的逼近型模/数转换器。iCMOS是一种结合了高电压CMOS和低电压CMOS的特殊工艺,使得高精度模拟器件操作电压的范围达到了33V,远远高于上一代器件所能承受的极限。由于采用了此种新的工艺,AD7329在实现双极性输入的同时提高了精度,并且减小了功耗和体积。

AD7329可以实现真正的双极性输入,并且具有4种可编程输入范围,即±10V,±5V,±2.5V和0~+10V,每个模拟输入通道可以被独立设置。同时模拟输入通道也可配置成单端输入模式、差分输入模式以及伪差分模式。该器件内置了一个2.5V的基准源,同时也允许外部基准的输入,在外部基准为3V时双极性模拟输入的范围是±12V。该器件采用的是SPI高速串行接口,总线时钟频率可以稳定工作在20MHz,在给ADC提供时钟的同时完成数据的传输。

系统原理与组成

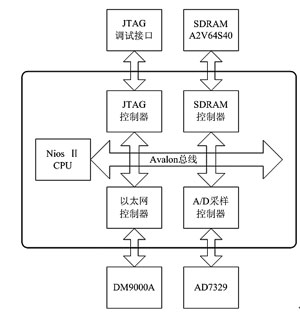

系统组成框图如图1所示,包括Nios Ⅱ嵌入式处理器、Avalon总线、JTAG控制器和调试接口、SDRAM、DM9000A网络接口以及AD7329采样控制模块。

图1 系统结构框图

在A/D采样控制器的控制下,AD7329采集得到的电压信号通过SPI接口传送到控制器的FIFO中,当数据量达到FIFO的75%时,控制器产生中断,通知CPU读取数据。CPU收到中断后,启动DMA,将A/D采样控制器FIFO中的数据传送到以太网控制器的FIFO中,而后利用 NicheStack协议栈采用UDP方式将数据发送到网上。JTAG控制器和调试接口用来软硬件调试和系统软硬件程序的配置。SDRAM用来运行软件程序和提供FIFO的物理空间。

AD7329与Nios Ⅱ接口的设计

1 接口硬件设计

SPI(Serial Peripheral Interface)即串行外围设备接口是Motorola公司推出的一种同步串行接口。SPI总线是一种4线同步总线,占用较少的I/O资源。Nios Ⅱ与外界SPI接口通信可采用软件控制I/O、Mege IP Core以及自定义外设等方法。

软件控制I/O是利用CPU执行程序来模拟SPI接口的时序从而完成通信,其特点是设计简单、使用方便,但是由于CPU长时间进行时序模拟,不能发挥出高速信号处理的优势,故不适合本设计;Mege IP Core是Altera公司(或第三方)推出的可以实现特定功能的IP核,通过将它集成到SoPC系统中,可以快速构成SPI接口,但利用此种方法只能完成基本的通信功能,不能实现更多的扩展,故本设计不采用;自定义外设即定制基于Avalon的用户外设,通过自行设计SPI硬件控制器,在实现通信功能的同时,使其具有采样通道控制、FIFO缓冲以及DMA功能,使CPU不再参与通信操作,而利用DMA中断进行采样数据的传输,可以极大的提高CPU利用率,故本设计采用此种方法。

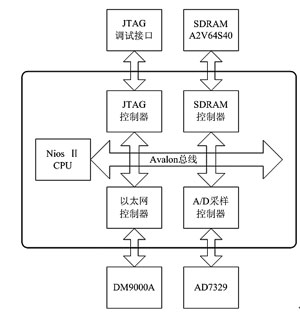

本设计采用Verilog硬件描述语言对自定义的A/D采样控制器进行设计。如图2所示,控制器与Avalon总线通过data_bus、 addr、pro_clk、WR、RD以及interrupt进行通信,接受CPU的控制指令和回传采样数据;控制器与AD7329通过miso、 mosi、sclk以及CS进行通信,完成采集的控制和数据的传输。控制器设计好后利用SoPC Builder对其封装成一个元件(也可称之为IP核),而后可以像Altera提供的Mege IP Core外设一样使用。

图2 SPI原理图

2 接口软件实现

为了实现A/D采样控制器的功能,除了硬件设计外,还需要开发相应的硬件抽象层(HAL)驱动程序。HAL可以看作是一个支持应用程序开发的软件平台,它提供API函数接口,屏蔽硬件访问细节,虽然占用了一些额外的资源,但大大增加了应用程序的开发速度和可移植性。

驱动开发的第一步就是创建一个用于描述设备寄存器的设备头文件,在这个文件中应用清晰易懂的宏符号描述出寄存器集合,并给出其访问方法;第二步为创建驱动程序,即为应用程序编写API函数,用以完成控制器初始化、工作模式设定、SPI通信等功能;驱动程序开发完毕后,还需要把源程序文件放到约定的目录下,并为它编写一个简单的Makefile文件,这样,驱动程序才能编译到HAL系统库中。下面列出了主要的API函数:

bool Init_SPI(void); //SPI控制器初始化,返回值为0表示成功,下同

bool Init_ad7329(void); //AD7329初始化

bool Set_ad7329_InputMode(unsigned int inputmode) ; //设置模拟输入模式

bool Set_ad7329_PowerMode(unsigned int powermode); //设置输入电源范围

bool Set_ad7329_WorkMode(char workmode,char startchannl,char number);

//设置工作模式:即所选通道、通道自动切换模式

int Set_ad7329_SampleStart(void); //开始采样,返回值为采样工作模式

SoPC与Nios Ⅱ嵌入式系统简介

SoPC(System On Programmable Chip,可编程的片上系统)是Altera公司提出来的一种灵活、高效的SoC解决方案。它将处理器、存储器、I/O口等系统设计需要的功能模块集成到一个可编程器件上,构成一个可编程的片上系统。SoPC是PLD和ASIC技术融合的结果,可以认为SoPC代表了半导体产业未来的发展方向。

Nios Ⅱ系列32位RISC嵌入式处理器具有超过200DMIP的性能,在低成本FPGA中实现成本只有35美分。由于处理器是软核形式,具有很大的灵活性,可以在多种系统设置组合中进行选择,满足成本和功能要求。采用Nios Ⅱ处理器进行设计,可以帮助用户将产品迅速推向市场,延长产品生命周期,防止出现处理器逐渐过时的情况。

AD7329模/数转换器

AD7329是ADI公司推出的基于iCMOS(industrial CMOS)工艺的8通道12位精度1MSa/s采样速度的逼近型模/数转换器。iCMOS是一种结合了高电压CMOS和低电压CMOS的特殊工艺,使得高精度模拟器件操作电压的范围达到了33V,远远高于上一代器件所能承受的极限。由于采用了此种新的工艺,AD7329在实现双极性输入的同时提高了精度,并且减小了功耗和体积。

AD7329可以实现真正的双极性输入,并且具有4种可编程输入范围,即±10V,±5V,±2.5V和0~+10V,每个模拟输入通道可以被独立设置。同时模拟输入通道也可配置成单端输入模式、差分输入模式以及伪差分模式。该器件内置了一个2.5V的基准源,同时也允许外部基准的输入,在外部基准为3V时双极性模拟输入的范围是±12V。该器件采用的是SPI高速串行接口,总线时钟频率可以稳定工作在20MHz,在给ADC提供时钟的同时完成数据的传输。

系统原理与组成

系统组成框图如图1所示,包括Nios Ⅱ嵌入式处理器、Avalon总线、JTAG控制器和调试接口、SDRAM、DM9000A网络接口以及AD7329采样控制模块。

图1 系统结构框图

在A/D采样控制器的控制下,AD7329采集得到的电压信号通过SPI接口传送到控制器的FIFO中,当数据量达到FIFO的75%时,控制器产生中断,通知CPU读取数据。CPU收到中断后,启动DMA,将A/D采样控制器FIFO中的数据传送到以太网控制器的FIFO中,而后利用 NicheStack协议栈采用UDP方式将数据发送到网上。JTAG控制器和调试接口用来软硬件调试和系统软硬件程序的配置。SDRAM用来运行软件程序和提供FIFO的物理空间。

AD7329与Nios Ⅱ接口的设计

1 接口硬件设计

SPI(Serial Peripheral Interface)即串行外围设备接口是Motorola公司推出的一种同步串行接口。SPI总线是一种4线同步总线,占用较少的I/O资源。Nios Ⅱ与外界SPI接口通信可采用软件控制I/O、Mege IP Core以及自定义外设等方法。

软件控制I/O是利用CPU执行程序来模拟SPI接口的时序从而完成通信,其特点是设计简单、使用方便,但是由于CPU长时间进行时序模拟,不能发挥出高速信号处理的优势,故不适合本设计;Mege IP Core是Altera公司(或第三方)推出的可以实现特定功能的IP核,通过将它集成到SoPC系统中,可以快速构成SPI接口,但利用此种方法只能完成基本的通信功能,不能实现更多的扩展,故本设计不采用;自定义外设即定制基于Avalon的用户外设,通过自行设计SPI硬件控制器,在实现通信功能的同时,使其具有采样通道控制、FIFO缓冲以及DMA功能,使CPU不再参与通信操作,而利用DMA中断进行采样数据的传输,可以极大的提高CPU利用率,故本设计采用此种方法。

本设计采用Verilog硬件描述语言对自定义的A/D采样控制器进行设计。如图2所示,控制器与Avalon总线通过data_bus、 addr、pro_clk、WR、RD以及interrupt进行通信,接受CPU的控制指令和回传采样数据;控制器与AD7329通过miso、 mosi、sclk以及CS进行通信,完成采集的控制和数据的传输。控制器设计好后利用SoPC Builder对其封装成一个元件(也可称之为IP核),而后可以像Altera提供的Mege IP Core外设一样使用。

图2 SPI原理图

2 接口软件实现

为了实现A/D采样控制器的功能,除了硬件设计外,还需要开发相应的硬件抽象层(HAL)驱动程序。HAL可以看作是一个支持应用程序开发的软件平台,它提供API函数接口,屏蔽硬件访问细节,虽然占用了一些额外的资源,但大大增加了应用程序的开发速度和可移植性。

驱动开发的第一步就是创建一个用于描述设备寄存器的设备头文件,在这个文件中应用清晰易懂的宏符号描述出寄存器集合,并给出其访问方法;第二步为创建驱动程序,即为应用程序编写API函数,用以完成控制器初始化、工作模式设定、SPI通信等功能;驱动程序开发完毕后,还需要把源程序文件放到约定的目录下,并为它编写一个简单的Makefile文件,这样,驱动程序才能编译到HAL系统库中。下面列出了主要的API函数:

bool Init_SPI(void); //SPI控制器初始化,返回值为0表示成功,下同

bool Init_ad7329(void); //AD7329初始化

bool Set_ad7329_InputMode(unsigned int inputmode) ; //设置模拟输入模式

bool Set_ad7329_PowerMode(unsigned int powermode); //设置输入电源范围

bool Set_ad7329_WorkMode(char workmode,char startchannl,char number);

//设置工作模式:即所选通道、通道自动切换模式

int Set_ad7329_SampleStart(void); //开始采样,返回值为采样工作模式

嵌入式 总线 Altera SoC 半导体 FPGA ADI CMOS 电压 ADC Verilog 仿真 Quartus 传感器 相关文章:

- 基于ARM与DSP的嵌入式运动控制器设计(04-25)

- 多核及虚拟化技术在工业和安全领域的应用(05-23)

- 基于ARM核的AT75C220及其在指纹识别系统中的应用(05-24)

- 基于FPGA安全封装的身份认证模型研究(05-27)

- 基于nRF2401智能无线火灾监控系统设计(04-01)

- 智能视频多媒体技术的应用(05-31)