基于Nios II的过程控制实验装置的研究

时间:06-21

来源:互联网

点击:

|

4. 软件设计

4.1 基于Nios IDE的软件设计

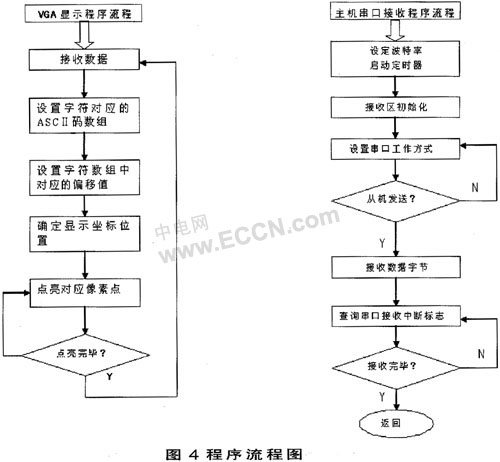

由SOPC Builder构建成的硬件系统首先必须下载到FPGA中,在FPGA上生成对应外设的引脚,然后才能够通过IDE烧程序给外设,使外设可以正常的运行。也就是说对主程序部分必须要在IDE模式下进行调试,这是整个过程中感觉效率比较低的地方,每次修改的程序都必须通过再次运行Run As Hardware重新编译才能写入硬件中,造成调试进度很慢。程序可以在SRAM或SDRAM上运行。为了保证断电后数据不丢失,采用FLASH Programmer把数据写入FLASH,然后把CPU的ResetAddress地址指向FLASH。通电后系统会自动对FPGA进行配置,并运行内部程序。该部分的程序主要是设置多个串口通信的时序以及VGA显示的内容。程序流程图如图4所示。

|

5. 结果分析

经过检测和调试,系统的整体功能完全可以正常实现。系统采用Nios软核结合可编程逻辑阵列对旋风预热器的仿真模型的模拟工作状态进行检测和控制。实现了多线程的串口通信和VGA的显示,充分发挥了FPGA快速响应的实用性特点和支持CPU操作的强大功能。使用SOPC Builder可以方便的对系统的扩展部分和自定义部分进行添加和删除,根据需要开发自己的IP核优化系统。充分利用SOPC的特点来缩短设计和开发周期。

利用SOPC Builder配置了四个串口来完成这一要求,而这一特殊用法却是其它处理器如单片机,ARAM等无法实现的。

FPGA Quartus VHDL Verilog 总线 Altera 仿真 传感器 单片机 LED LCD 电压 显示器 电路 电阻 相关文章:

- 基于FPGA安全封装的身份认证模型研究(05-27)

- ARM在数字化远程视频监控系统的应用(05-20)

- FPGA在弹上信息处理机中的应用(04-15)

- 如何充满信心地设计军用SDR产品(07-25)

- 关于安防应用中图像处理难点分析及处理器选择(07-14)

- 基于 SoPC 的震动信号采集设备设计(08-14)