宽带多速率解调器的设计与实现

时间:11-25

来源:互联网

点击:

2.3 载波恢复电路的实现

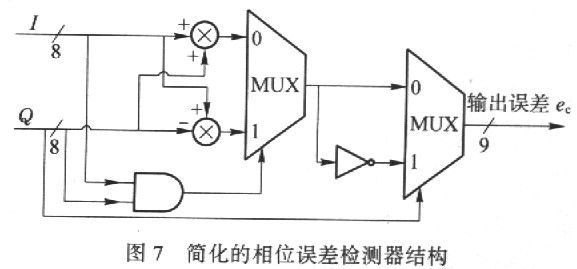

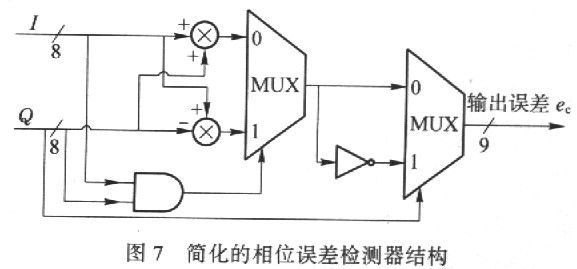

载波恢复电路可根据图2给出的结构实现.其中的相位误差检测器可作如下简化.

与图2中的结构相比,式(2)节省了两个乘法器,其结构如图7所示.

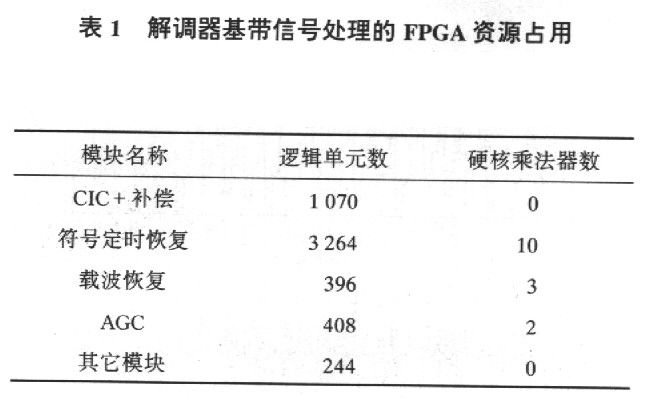

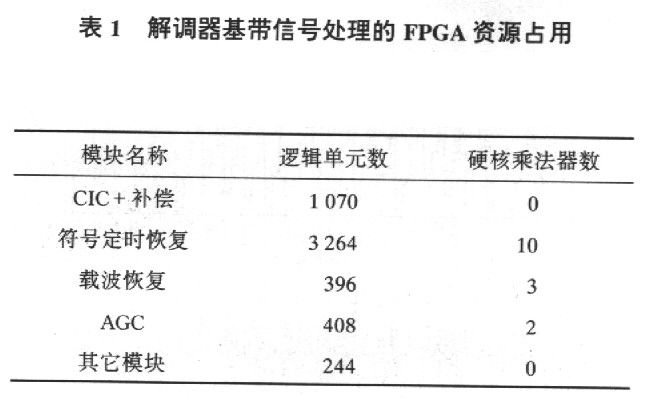

高速解调器的基带信号处理子模块均用Verilog硬件描述语言实现.表1为在Xilinx公司的VirtexⅡxC2V1000-5 FPGA芯片中实现上述模块的资源占用情况.

3 性能测试结果

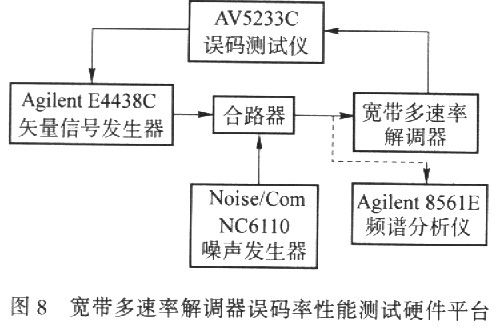

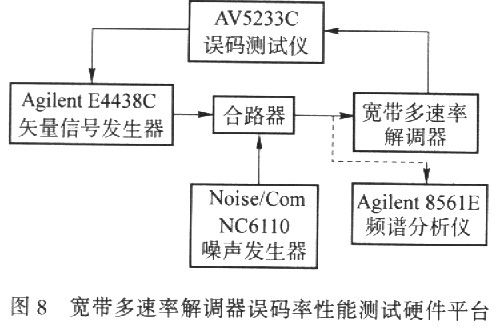

对宽带多速率解调器进行了中频环路的误码率性能测试,测试平台如图8所示.

矢量信号发生器选用Agilent公司的E4438C,其最高符号速率可达50 MS/s;噪声发生器为Noise/Com公司的NC6110;信号功率和噪声功率通过Agilent公司的频谱分析仪8561E测量,然后将测得的SNR转换为相应的Eb/No.

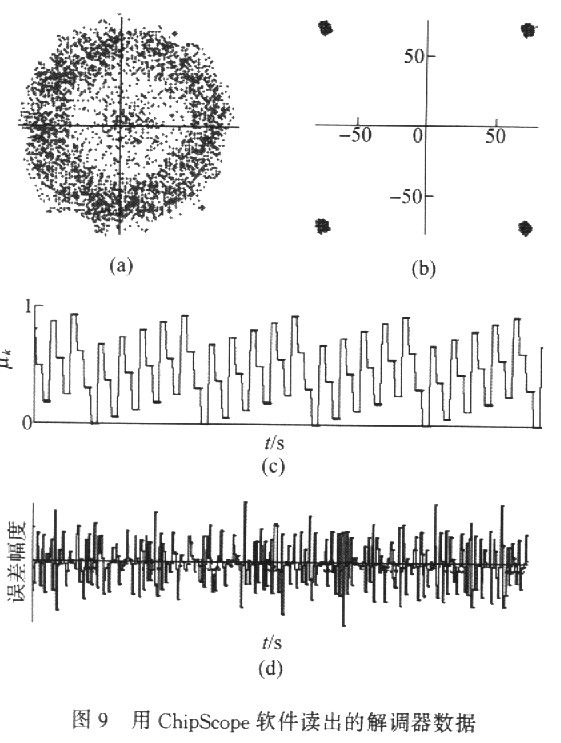

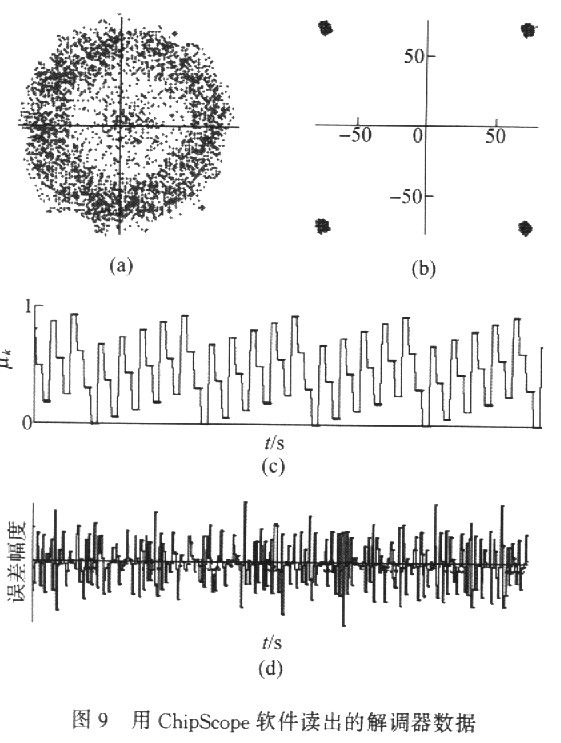

图9为宽带多速率解调器工作时,利用xilinx公司的ChipSeope软件,通过JTAG口读出的数据其中,图9a为A/D采样后进入FPGA的基带信号星座图;图9b为解调器完成符号定时恢复和载波恢复后输出的信号星座图;图9c为小数间隔μk随时间的变化;图9d为环路滤波器输出的误差信号.由于采样速率与符号速率为整数倍关系,因此小数间隔μk具有周期性,在几个固定值之间变化.实际应用中,A/D的采样速率与符号速率可能是无理数倍关系,这时小数间隔μk的取值将不再具有周期性.

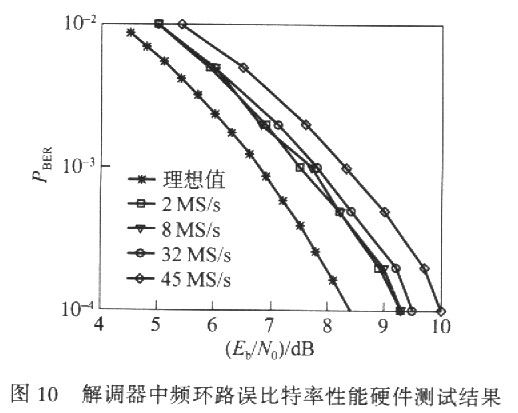

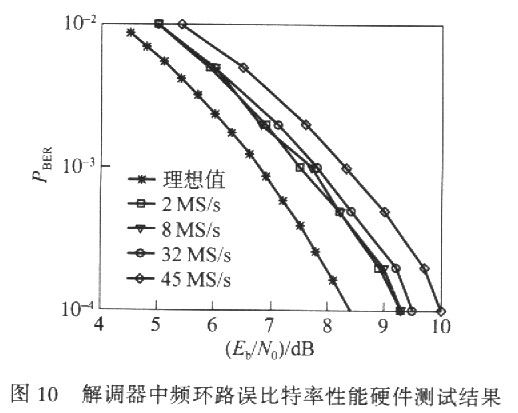

误码率测试结果如图10所示.测试结果表明,作者设计实现的宽带多速率解调器可对高达45 MS/s符号速率的QPSK信号进行解调.与理论值相比,在误比特率相同的条件下,在符号速率2~10 MS/s范围内,Eh/No相差小于1.0 dB,在45 MS/s时相差小于1.6 dB.

解调器在45MS/s时性能损失的原因在于A/D的采样率小于100 MHz,因此对于45 MS/s的QP-SK信号,每个符号的采样点数小于2.3,因此带来插值定时恢复结构性能的恶化,引起误码率上升提高A/D的采样速率或设计低采样率下性能更好的插值滤波器,将会进一步提高解调器在高符号速率下的性能.

载波恢复电路可根据图2给出的结构实现.其中的相位误差检测器可作如下简化.

与图2中的结构相比,式(2)节省了两个乘法器,其结构如图7所示.

高速解调器的基带信号处理子模块均用Verilog硬件描述语言实现.表1为在Xilinx公司的VirtexⅡxC2V1000-5 FPGA芯片中实现上述模块的资源占用情况.

3 性能测试结果

对宽带多速率解调器进行了中频环路的误码率性能测试,测试平台如图8所示.

矢量信号发生器选用Agilent公司的E4438C,其最高符号速率可达50 MS/s;噪声发生器为Noise/Com公司的NC6110;信号功率和噪声功率通过Agilent公司的频谱分析仪8561E测量,然后将测得的SNR转换为相应的Eb/No.

图9为宽带多速率解调器工作时,利用xilinx公司的ChipSeope软件,通过JTAG口读出的数据其中,图9a为A/D采样后进入FPGA的基带信号星座图;图9b为解调器完成符号定时恢复和载波恢复后输出的信号星座图;图9c为小数间隔μk随时间的变化;图9d为环路滤波器输出的误差信号.由于采样速率与符号速率为整数倍关系,因此小数间隔μk具有周期性,在几个固定值之间变化.实际应用中,A/D的采样速率与符号速率可能是无理数倍关系,这时小数间隔μk的取值将不再具有周期性.

误码率测试结果如图10所示.测试结果表明,作者设计实现的宽带多速率解调器可对高达45 MS/s符号速率的QPSK信号进行解调.与理论值相比,在误比特率相同的条件下,在符号速率2~10 MS/s范围内,Eh/No相差小于1.0 dB,在45 MS/s时相差小于1.6 dB.

解调器在45MS/s时性能损失的原因在于A/D的采样率小于100 MHz,因此对于45 MS/s的QP-SK信号,每个符号的采样点数小于2.3,因此带来插值定时恢复结构性能的恶化,引起误码率上升提高A/D的采样速率或设计低采样率下性能更好的插值滤波器,将会进一步提高解调器在高符号速率下的性能.

仿真 FPGA 滤波器 低通滤波器 电路 Verilog Xilinx 信号发生器 频谱分析仪 相关文章:

- 扩大ARM SoC的验证覆盖缩短仿真时间(07-20)

- Proteus在单片机系统设计中的应用(04-21)

- 仿真扩展芯片(EEC)简化高速汽车嵌入式处理器的集成(06-03)

- 使用仿真和虚拟化的嵌入式设计(09-06)

- PIC单片机的应用设计技巧(07-03)

- DDS流水线结构的改进(07-31)