带RF输出的全数字调制器设计

时间:11-25

来源:互联网

点击:

软件定义无线电(SDR)终端促进了物理层功能的可编程实现。很多研究工作已经应用DSP和FPGA实现物理层的基带功能。

SDR无线电是如此定义的电台,其天线后面的某段实现了数字化。其后电台可用柔性及可配置的功能模块来实现DSP算法。随着技术的进步,数字化可以在天线后,或非常接近于天线,如此几乎所有的无线电功能都可以使用高速可编程的DSP引擎通过软件实现。

目前的无线电结合了模拟和数字构造模块。RF功能还是适合模拟电路实现,而基带功能更适合于DSP的实现。数字化前端(DFE)常用来连接RF及基带处理。DEF通常能够处理10MH左右的频率信号,常被称为数字中频(IF)。因此,重要的模拟模块留在了RF和IF之间。

数字RF收发器可扩展软件定义功能到射频频段。所有数字发射机的关键优势是高效的功率放大;数字化合并多通道信号;以及软件的可编程或可重配置性。

使用全数字发射机,整个发射机可以用DSP或FPGA实现,可以利用CMOS技术增强中的性能。除了与SDR兼容,基于DSP的RF系统可补偿RF通道的不平衡性。因此,直接在射频产生数字信号吸引了很多研究人员和工程师的兴趣。

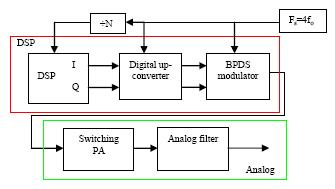

一种比较传统的方法使用带通delta-sigma调制在无线电频率上产生二进制信号。二进制信号可与开关模式功率放大器(PA)一起使用以实现比其他功放技术更高的效率(图1)。这种体系结构的限制是带通delta-sigma (BPDS)调制在中心频率的四倍处运行,达到几千兆赫。为了适应如此高的频率操作,定制的IC必须仔细设计,不具备重新编程能力。

另外一种方式是用脉宽调制(PWM)数字合成二进制RF信号。PWM是很久以前提出的一种模拟调制,但是最近流行起来,特别是在数字音频放大应用上。D类音频PA,由PWM音频信号驱动,可达到90%以上的效率。Delta-sigma类型调制也可用于数字PWM,但与BPDS方式比较运行在较低频率。然而,delta-sigma环路倾向于比BPDS更复杂,由于其较低的过采样率和PWM有关的非线性。

测试配置使用存储在测试模式发生器中的离线计算的信号源。在本例中,设计了一个实时系统来演示使用数字PWM的RF信号数字发生器的能力。

数字RFPWM 发生器

由数字功放技术推动的数字PWM,数字信号无须依靠数模转换器(DAC)就可以直接转换成高功率模拟信号。由于全数字音频系统越来越受到关注,数字功放已经在数字音频应用上开始流行。

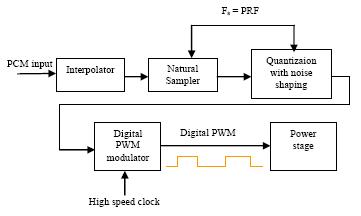

在数字PWM,脉宽以高速时钟离散化。因此,采样计数器可根据高速参考时钟产生数字PWM波形(图2)。内插器增加PCM输入的采样频率到适合PWM调制的水平。该频率经常称为脉冲重复频率(PRF)。

正常采样器是均匀采样数字信号为基础计算正常采样信号值。显然当采用PWM时,正常采样信号基带失真远小于均匀采样。

出于实现考虑,量化需确保高速参考时钟运行在适当地频率上。例如,PCM的原始输入是44.1 kHz,16倍内插器将导致705.6 kHz的PRF。若脉宽量化到16位,高速参考时钟必须达到46-GHz。假如只需要8位量化脉宽的话,高速参考时钟可至180 MHz。因此,用适当的技术实现将比较容易。噪音成型技术,delta-sigma调制技术,常被用来抑制量化引入的基带噪声。

处理密集的模块、正常采样器、及噪音成型量化的采样频率PRF。这是该工作的主要动机——主要的信号处理算法在较低的PRF而不是RF频率上执行。

全数字RFPWM

全数字RF PWM称为正交积分噪音成型(INS),是用于量化及噪音成型模块的一种算法。其主要目标是抑制基带脉宽量化处理过程引入的噪声功率。它不同于其它在反馈环中引入非线性项的算法。不考虑INS算法的细节的话,正交INS可看成是2个独立的PWM调制器,分别用于复信号的同相(I)和正交分量(Q)。

这些脉宽调制使用以前描述过的相同体系结构。这些PWM输出的是基带信号,需要进一步和数字本机振荡器信号混合形成RF带通信号。假如基带PWM及数字本机振荡器信号都是二进制,混合操作只不过是简单的逻辑XOR操作。

另一种简化该混频操作的方法是使数字本振的同相支路取取当0, 1, 0, -1三值,正交支路取-1, 0, 1, 0。这样,数字混频器只输出-Q, I, Q, -I 序列。当I及Q都是二进制PWM信号时,混频器的输出也将是二进制的。为了保证本振信号是2种格式中的一种,取样频率必须是4倍本振频率。来自2个数字混频器的信号组合成需要的RF信号。

对于PWM调制的信号,信号信息在脉冲宽度中承载。因为脉冲宽度定义为上升沿和下降沿之间的持续时间,在基带PWM后过度区将被保留。然而,在同相和正交本振信号之间存在90度的相位差。因此,需要特别小心的是必须确信基带PWM与他们的本振信号分别是同步的的。因为采样率设置在4倍的本振频率,相差等于1/4周期。

基带PWM同相、正交波形是分别生成的:内部引入四分之一相差来补充同相和正交本振信号之间的相差。研究基带PWM和RFPWM的定时波形,本振信号是三值格式,而组合输出RFPWM信号是二进制。此外,两个基带PWM都分别同步到其本振信号的上升沿。

SDR无线电是如此定义的电台,其天线后面的某段实现了数字化。其后电台可用柔性及可配置的功能模块来实现DSP算法。随着技术的进步,数字化可以在天线后,或非常接近于天线,如此几乎所有的无线电功能都可以使用高速可编程的DSP引擎通过软件实现。

目前的无线电结合了模拟和数字构造模块。RF功能还是适合模拟电路实现,而基带功能更适合于DSP的实现。数字化前端(DFE)常用来连接RF及基带处理。DEF通常能够处理10MH左右的频率信号,常被称为数字中频(IF)。因此,重要的模拟模块留在了RF和IF之间。

数字RF收发器可扩展软件定义功能到射频频段。所有数字发射机的关键优势是高效的功率放大;数字化合并多通道信号;以及软件的可编程或可重配置性。

使用全数字发射机,整个发射机可以用DSP或FPGA实现,可以利用CMOS技术增强中的性能。除了与SDR兼容,基于DSP的RF系统可补偿RF通道的不平衡性。因此,直接在射频产生数字信号吸引了很多研究人员和工程师的兴趣。

一种比较传统的方法使用带通delta-sigma调制在无线电频率上产生二进制信号。二进制信号可与开关模式功率放大器(PA)一起使用以实现比其他功放技术更高的效率(图1)。这种体系结构的限制是带通delta-sigma (BPDS)调制在中心频率的四倍处运行,达到几千兆赫。为了适应如此高的频率操作,定制的IC必须仔细设计,不具备重新编程能力。

|

采用BPDS的数字发射机 |

另外一种方式是用脉宽调制(PWM)数字合成二进制RF信号。PWM是很久以前提出的一种模拟调制,但是最近流行起来,特别是在数字音频放大应用上。D类音频PA,由PWM音频信号驱动,可达到90%以上的效率。Delta-sigma类型调制也可用于数字PWM,但与BPDS方式比较运行在较低频率。然而,delta-sigma环路倾向于比BPDS更复杂,由于其较低的过采样率和PWM有关的非线性。

测试配置使用存储在测试模式发生器中的离线计算的信号源。在本例中,设计了一个实时系统来演示使用数字PWM的RF信号数字发生器的能力。

数字RFPWM 发生器

由数字功放技术推动的数字PWM,数字信号无须依靠数模转换器(DAC)就可以直接转换成高功率模拟信号。由于全数字音频系统越来越受到关注,数字功放已经在数字音频应用上开始流行。

在数字PWM,脉宽以高速时钟离散化。因此,采样计数器可根据高速参考时钟产生数字PWM波形(图2)。内插器增加PCM输入的采样频率到适合PWM调制的水平。该频率经常称为脉冲重复频率(PRF)。

|

组成数字PWM系统的信号处理模块 |

正常采样器是均匀采样数字信号为基础计算正常采样信号值。显然当采用PWM时,正常采样信号基带失真远小于均匀采样。

出于实现考虑,量化需确保高速参考时钟运行在适当地频率上。例如,PCM的原始输入是44.1 kHz,16倍内插器将导致705.6 kHz的PRF。若脉宽量化到16位,高速参考时钟必须达到46-GHz。假如只需要8位量化脉宽的话,高速参考时钟可至180 MHz。因此,用适当的技术实现将比较容易。噪音成型技术,delta-sigma调制技术,常被用来抑制量化引入的基带噪声。

处理密集的模块、正常采样器、及噪音成型量化的采样频率PRF。这是该工作的主要动机——主要的信号处理算法在较低的PRF而不是RF频率上执行。

全数字RFPWM

全数字RF PWM称为正交积分噪音成型(INS),是用于量化及噪音成型模块的一种算法。其主要目标是抑制基带脉宽量化处理过程引入的噪声功率。它不同于其它在反馈环中引入非线性项的算法。不考虑INS算法的细节的话,正交INS可看成是2个独立的PWM调制器,分别用于复信号的同相(I)和正交分量(Q)。

这些脉宽调制使用以前描述过的相同体系结构。这些PWM输出的是基带信号,需要进一步和数字本机振荡器信号混合形成RF带通信号。假如基带PWM及数字本机振荡器信号都是二进制,混合操作只不过是简单的逻辑XOR操作。

另一种简化该混频操作的方法是使数字本振的同相支路取取当0, 1, 0, -1三值,正交支路取-1, 0, 1, 0。这样,数字混频器只输出-Q, I, Q, -I 序列。当I及Q都是二进制PWM信号时,混频器的输出也将是二进制的。为了保证本振信号是2种格式中的一种,取样频率必须是4倍本振频率。来自2个数字混频器的信号组合成需要的RF信号。

对于PWM调制的信号,信号信息在脉冲宽度中承载。因为脉冲宽度定义为上升沿和下降沿之间的持续时间,在基带PWM后过度区将被保留。然而,在同相和正交本振信号之间存在90度的相位差。因此,需要特别小心的是必须确信基带PWM与他们的本振信号分别是同步的的。因为采样率设置在4倍的本振频率,相差等于1/4周期。

基带PWM同相、正交波形是分别生成的:内部引入四分之一相差来补充同相和正交本振信号之间的相差。研究基带PWM和RFPWM的定时波形,本振信号是三值格式,而组合输出RFPWM信号是二进制。此外,两个基带PWM都分别同步到其本振信号的上升沿。

无线电 DSP FPGA 模拟电路 收发器 射频 CMOS 放大器 PWM DAC 振荡器 滤波器 仿真 电路 Xilinx 相关文章:

- 基于DSP的单兵作战用机器人控制系统设计(07-25)

- 应用处理器连接汽车和消费电子两大领域(02-26)

- TMS320C6000嵌入式系统优化编程的研究(04-08)

- TI首席科学家展望2020年处理器架构和DSP的发展(10-24)

- 基于JTAG接口实现ARM的FPGA在线配置(04-24)

- 数字信号处理器的市场竞争及技术发展趋势(06-24)