基于ARM嵌入式平台的X86译码SOC架构设计

时间:11-05

来源:互联网

点击:

3 片上总线结构

在ARM SoC体系结构中,有Master和Slave这两个重要的概念。Master是ARM SoC体系结构中的主单元,他可以向总线发出请求并且对传输进行初始化,例如对存储器进行读/写操作,典型的Master可以是CPU,DSP,DMA。Slave是ARM SoC体系结构中的从单元,典型的Slave为片上或者片外存储器,它们都有自己惟一的地址范围。Master发起读/写操作时,在初始化中会给出读/写操作的地址,而地址译码器则根据这个地址决定哪个Slave被Master选中,然后相应的Slave做出相应。

在AHB系统中,若有2个Master常需要AccessBus,则系统的Performance必定会下降。为了解决这个问题。ARM提出了MulTI-layer AHB,其基本构想是2个Master走不同的Bus去访问Slave,如果访问的Slave不同,则两个Master可以同步的进行Transfer。若彼此访问一个Slave,则根据优先级去判断要先处理谁的Transfer。

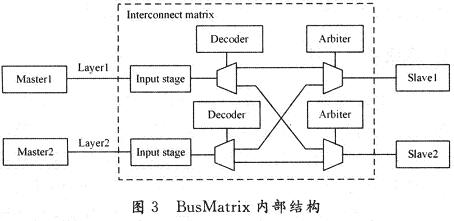

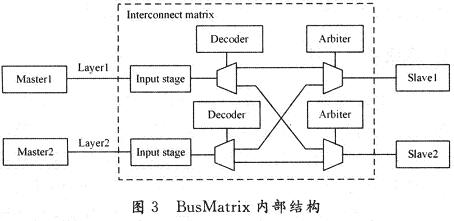

该总线结构使用了Multi_layerbus switch(BusMatrix)模块。AHB BusMatrix的设计可以分为3个部分:输入级、译码级和输出级。图3为该设计所使用的结构,其中,输入和输出的个数可以根据系统的Master和Slave灵活调整。

可以看出,每个Layer都有一个译码器来决定Master要访问哪一个Slave,通过多路选择器实Master和Slave之间的Transfer。。每个Slave口都有自己的仲裁器,该仲裁器使用固定优先级,最高优先级的Layer可以优先访问对应的Slave。

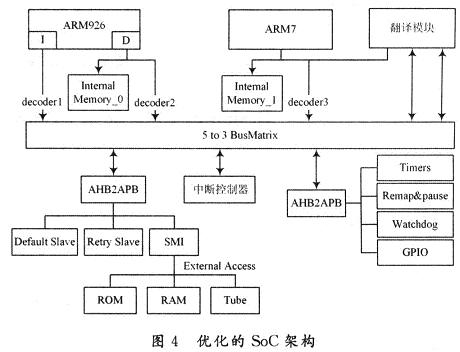

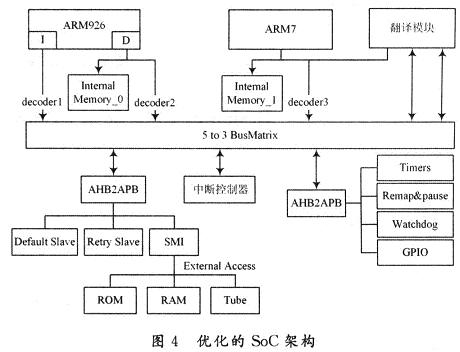

随着系统中Master和Slave的增多,Busmatrix模块的复杂度也会明显增加,如果按照系统所有的Mas-ter和Slave的个数来确定输入/输出口的个数,Busma-trix将会非常复杂,因此对系统结构进行优化变得非常必要。根据系统工作情况可以发现,翻译模块的Slave端口仅被ARM7核访问,即向翻译模块存取指令所需的地址,控制其工作,该Slave可以看作是ARM7核私有的,而不被其他Master访问。有些Slave只有在特殊情况下才被访问,因此可以将多个Slave看作一个Slave挂在BusMatrix上。优化后的SoC硬件架构如图4所示。

4 结 语

这里给出了一种具有X86到ARM二进制翻译和执行功能的SoC系统。利用Multi-layer bus SWitch(BusMatrix)模块实现Multi-layer。总线结构,在多个核不访问同一个Slave时,可以同时执行各自功能,有效提高系统的性能,且该总线结构的可扩展性强。同时根据系统工作的特点,对总线结构进行了优化,减小了总线的复杂度。

在ARM SoC体系结构中,有Master和Slave这两个重要的概念。Master是ARM SoC体系结构中的主单元,他可以向总线发出请求并且对传输进行初始化,例如对存储器进行读/写操作,典型的Master可以是CPU,DSP,DMA。Slave是ARM SoC体系结构中的从单元,典型的Slave为片上或者片外存储器,它们都有自己惟一的地址范围。Master发起读/写操作时,在初始化中会给出读/写操作的地址,而地址译码器则根据这个地址决定哪个Slave被Master选中,然后相应的Slave做出相应。

在AHB系统中,若有2个Master常需要AccessBus,则系统的Performance必定会下降。为了解决这个问题。ARM提出了MulTI-layer AHB,其基本构想是2个Master走不同的Bus去访问Slave,如果访问的Slave不同,则两个Master可以同步的进行Transfer。若彼此访问一个Slave,则根据优先级去判断要先处理谁的Transfer。

该总线结构使用了Multi_layerbus switch(BusMatrix)模块。AHB BusMatrix的设计可以分为3个部分:输入级、译码级和输出级。图3为该设计所使用的结构,其中,输入和输出的个数可以根据系统的Master和Slave灵活调整。

可以看出,每个Layer都有一个译码器来决定Master要访问哪一个Slave,通过多路选择器实Master和Slave之间的Transfer。。每个Slave口都有自己的仲裁器,该仲裁器使用固定优先级,最高优先级的Layer可以优先访问对应的Slave。

随着系统中Master和Slave的增多,Busmatrix模块的复杂度也会明显增加,如果按照系统所有的Mas-ter和Slave的个数来确定输入/输出口的个数,Busma-trix将会非常复杂,因此对系统结构进行优化变得非常必要。根据系统工作情况可以发现,翻译模块的Slave端口仅被ARM7核访问,即向翻译模块存取指令所需的地址,控制其工作,该Slave可以看作是ARM7核私有的,而不被其他Master访问。有些Slave只有在特殊情况下才被访问,因此可以将多个Slave看作一个Slave挂在BusMatrix上。优化后的SoC硬件架构如图4所示。

4 结 语

这里给出了一种具有X86到ARM二进制翻译和执行功能的SoC系统。利用Multi-layer bus SWitch(BusMatrix)模块实现Multi-layer。总线结构,在多个核不访问同一个Slave时,可以同时执行各自功能,有效提高系统的性能,且该总线结构的可扩展性强。同时根据系统工作的特点,对总线结构进行了优化,减小了总线的复杂度。

SoC ARM Linux 总线 Verilog 解码器 DSP 相关文章:

- 高带宽嵌入式应用中SoC微控制器的新型总线设计 (02-02)

- SoC前段(ARM)嵌入式系统开发实作训练(上) (02-28)

- SoC前段(ARM)嵌入式系统开发实作训练(下)(02-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 开放源码硬件简史(05-21)

- 可配置处理器技术优势详解(05-15)