用户可定制的处理器

时间:10-12

来源:互联网

点击:

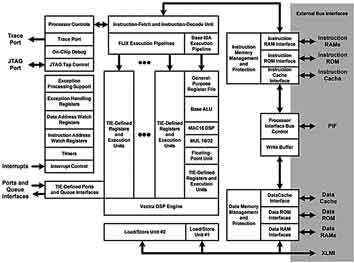

图1 Xtensa可配置处理器模块图

处理器的可扩展能力可以看做可配置的高级形式,因为它的应用更为广泛。系统设计者和应用专家可以直接探索应用的性能需求以及什么样的处理器架构和指令集才能满足这样的需求。

3 微处理器的应用将SoC设计与板级设计区分开来

RTL硬逻辑有许多优势——面积小、功耗低、性能强大。但是在大规模的SoC设计中,采用RTL硬逻辑的不利因素(设计周期长、验证困难、不够灵活)正在逐渐大过其优势。而保留了大多数RTL硬逻辑的优点,又能够缩短开发时间并降低风险的设计方法正在流行起来,这就是针对特殊应用进行优化以取代复杂RTL设计的可配置处理器。

针对应用进行优化的处理器与相应的RTL设计拥有相近的数据通路,它在基本处理器核的流水线上增加额外的运算单元,新的寄存器或寄存器文件以及芯片架构师定义的其他功能模块来实现特定的应用。

在Xtensa处理器中,这些扩展功能是利用一种名为TIE语言的类Verilog语言来描述的。TIE语言经过优化,适用于描述数据处理指令的功能并对其进行编码。用TIE语言来进行描述比RTL要简洁得多,因为它去掉了所有时序逻辑,包括状态机描述、流水线寄存器以及初始化顺序。对于固件程序员来说,处理器中用TIE语言扩展的新指令和寄存器都可以通过编译器和汇编器来进行调用。利用处理器中取指、译码、执行的流水线机制,通过C或C++高级语言编程,可以由固件程序来控制处理器数据通路上的操作。用来替代RTL模块的可扩展处理器与传统的RTL设计在结构上大同小异:更深的流水线、并行的执行单元、特殊的状态寄存器、比片内外存储器间更宽的数据接口等。这些扩展后的处理器保留了原来RTL设计强大的运算能力和数据接口格式。

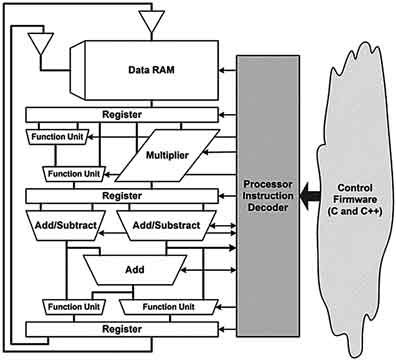

可扩展处理器对数据通路的控制机制则与RTL设计中依靠硬件状态机切换状态大为不同。实际上,操作的顺序完全由处理器上运行的固件程序控制,如图2所示。用跳转指令来实现控制操作,load/store指令来实现内存操作,通用和专用计算指令来实现数据运算操作。

图2 可编程的功能模块:数据通路+处理器+软件程序

移动电话领域中的Viterbi解码的例子可以很好地说明可扩展处理器可以替代RTL硬逻辑。

GSM标准利用Viterbi解码将信息从包含噪声的信道中提取出来。解码过程中会用到包括8次逻辑计算(4次加法、2次比较、2次选择)的蝶形运算,从接收到的数据流中每解码一个符号需要8次蝶形运算。如果采用通用RISC处理器,需要50~80个指令周期完成一次Viterbi蝶形运算,即使在TI高端的超长指令字DSP 320C64xx上,也需要1.75个周期。

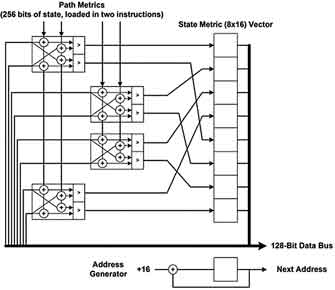

利用TIE语言,设计者可以为Xtensa处理器增加一条专门完成Viterbi蝶形运算的指令,使用处理器的128位宽I/O总线一次取8个符号数据,如图3所示为处理器添加运算单元和地址产生逻辑,这样完成一次Viterbi蝶形运算只需要0.16个周期。在未扩展的Xtensa处理器上执行Viterbi蝶形运算需要42个周期,也就是说,通过增加蝶形运算的专用硬件(大约11000门电路),就获得了250倍的性能提升。

图3 Viterbi蝶形算法硬件模块

4 结论

如今,软件模块硬逻辑化的现象非常普遍。在开发协议标准的早期,通常采用基于处理器的实现方法,一些常见的标准,如视频领域的MPEG2算法,3G通信领域的W-CDMA算法、安全加密领域的SSL和triple-DES算法,都是由处理器实现逐渐过渡到RTL硬逻辑实现。但是这种过渡正在被软硬件实现方法间巨大的性能与设计难度差别所限制。可配置与可扩展处理器的出现带来了一种新的设计方法,既可以方便快速的进行芯片开发,灵活适应新的协议标准,又具有足够小的芯片面积和功耗,从而可以进行大规模的生产。

SoC 自动化 嵌入式 总线 FPGA 仿真 DSP Verilog 电路 相关文章:

- 高带宽嵌入式应用中SoC微控制器的新型总线设计 (02-02)

- SoC前段(ARM)嵌入式系统开发实作训练(上) (02-28)

- SoC前段(ARM)嵌入式系统开发实作训练(下)(02-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 开放源码硬件简史(05-21)

- 可配置处理器技术优势详解(05-15)