基于TR600芯片的过程调用设计与硬件实现

时间:09-17

来源:互联网

点击:

2 存取算于对存储体交叉访问技术

存取算子对存储体交叉访问机制解决了存取算子访问局部性与过程调用中参数传递的全局性之间的矛盾。由于在指令体系设计时,将Is存取算子设计成与SDRAM存储体一一对应的关系,这就使得存取算子只能固定访问单块存储体。而对于过程调用,主调过程实参传递可来自于任意存储体,被调过程的形参却只能指向某一个存储体.这就要求主调过程要将实参转移到形参指定的存储体内,才能正确执行调用;而在数据转移过程中,可能引起数据相关,并且浪费数据转移时间。本设计的解决方法是对LS存取算子做变换,使其能够访问所有存储体,避免数据转移,并称其为存取算子对存储体的交叉访问。

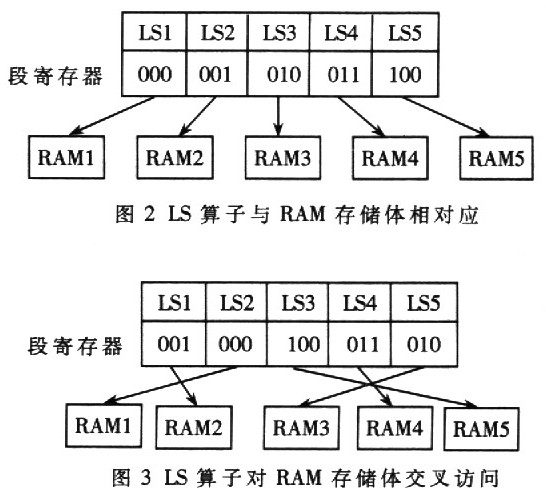

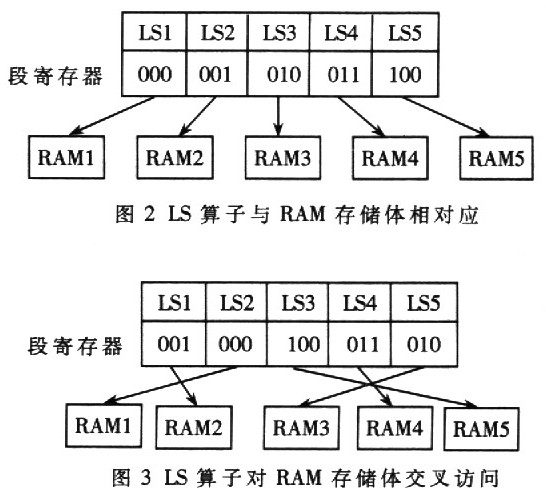

为了在过程调用时使存取算子能够访问任意存储体,使被调过程形参可以指向任意存储体,采用在体系中添加段寄存器配置,标识存取算子访问存储体的信息的方法。因此用户可以通过设置段寄存器的值来动态改变璐存取算子对SDRAM存储体的访问关系。在初始化状态,段寄存器中的值表示LS存取算子与存储体访问是一一对应的,如图2所示。在存储体交叉访问时,过程调用指令通过重置段寄存器值,改变存取算子与存储体的对应关系,并在执行调用过程中保持不变,如图3所示。段寄存器值由过程调用指令来动态配置,用户在使用过程中调用指令时,要参照指令格式的要求,在具体指令域装载段寄存器的配置信息。段寄存器值经过译码器译码产生存储体控制信息,再经过逻辑运算产生每个存储体的控制信号,包括:输入输出数据通路选择信号以及存储体的使能、读写、地址控制信号。

在TR600芯片体系结构中包含5块独立编址的SDRAM存储体,指令体系提供5个LS存取控制算子,分别为LSl控制读写RAMl、LS2控制读写RAM2……LS5控制读写RAM5。相应地,体系中提供5个3位段寄存器,标识过程调用时存取算子与存储体的对应关系。考虑到语音算法存在多重嵌套过程调用,每次过程调用时都可能发生存储体交叉访问的情况,因此设计了6层段寄存器阵列分别标·代表“或”操作识每次调用时存取算子与Rij表示第i层第j个段寄存器存储体的对应关系,如图4所示。执行过程调用指令时,段寄存器被重新配置,同时将过程调用的嵌套次数保存在层计数器。通过对层计数器输出的译码,产生段寄存器的层控制信息,包括段寄存器使能和段寄存器输出选择控制。通过段寄存器阵列的变换,实现每个存取算子对存储体访问的控制转换.再经过段译码器译码及逻辑运算产生存储体控制信号。例如,存储体RAMI使能信号(RAM1_E)可由5个段译码器译码产生的RAMl控制信号做逻辑“或”运算产生,变换逻辑运算即可以产生存储体的读写信号、地址控制信号和输入输出选择控制信号(本文不做详细论述)。

3 技术特点

(1)TR600芯片体系结构中重叠寄存器窗口技术采用可重组思想设计寄存器堆结构,提高了存储灵活性,适应了语音算法在过程调用中数据规格多样性的特点;多层窗口寄存器结构和寄存器堆局部可见的特点,解决了过程调用时的现场保护和参数传递问题,不需要设计现场保护参数的专用部件,减少了系统的时空开销。

(2)存储体交叉访问机制采用段寄存器标识存取算子与存储体的对应关系,由过程调用指令配置段寄存器.避免了因为参数传递而进行的存储体之间的数据转移;同时提供了清晰易读、编程灵活的指令界面,屏蔽了逻辑设计的复杂性,方便了用户指令编程。但过程调用功能的硬件实现与应用环境及体系结构是密不可分的,设计者应依据具体情况调整实现方案,如窗口寄存器堆的分层数目及段寄存器的层数,要根据具体算法中过程调用的最大嵌套层数而定,存取算子对存储体的交叉访问要依据体系结构提供的指令界面而定等,因为这些设计都具有灵活性和多样性。

本文论述的过程调用功能硬件实现方法也可以为其他应用设计借鉴,例如.在网络体系结构中,对多种通信协议的硬件实现以及RPC远程过程调用的实现都具有一定的参考价值。

存取算子对存储体交叉访问机制解决了存取算子访问局部性与过程调用中参数传递的全局性之间的矛盾。由于在指令体系设计时,将Is存取算子设计成与SDRAM存储体一一对应的关系,这就使得存取算子只能固定访问单块存储体。而对于过程调用,主调过程实参传递可来自于任意存储体,被调过程的形参却只能指向某一个存储体.这就要求主调过程要将实参转移到形参指定的存储体内,才能正确执行调用;而在数据转移过程中,可能引起数据相关,并且浪费数据转移时间。本设计的解决方法是对LS存取算子做变换,使其能够访问所有存储体,避免数据转移,并称其为存取算子对存储体的交叉访问。

为了在过程调用时使存取算子能够访问任意存储体,使被调过程形参可以指向任意存储体,采用在体系中添加段寄存器配置,标识存取算子访问存储体的信息的方法。因此用户可以通过设置段寄存器的值来动态改变璐存取算子对SDRAM存储体的访问关系。在初始化状态,段寄存器中的值表示LS存取算子与存储体访问是一一对应的,如图2所示。在存储体交叉访问时,过程调用指令通过重置段寄存器值,改变存取算子与存储体的对应关系,并在执行调用过程中保持不变,如图3所示。段寄存器值由过程调用指令来动态配置,用户在使用过程中调用指令时,要参照指令格式的要求,在具体指令域装载段寄存器的配置信息。段寄存器值经过译码器译码产生存储体控制信息,再经过逻辑运算产生每个存储体的控制信号,包括:输入输出数据通路选择信号以及存储体的使能、读写、地址控制信号。

在TR600芯片体系结构中包含5块独立编址的SDRAM存储体,指令体系提供5个LS存取控制算子,分别为LSl控制读写RAMl、LS2控制读写RAM2……LS5控制读写RAM5。相应地,体系中提供5个3位段寄存器,标识过程调用时存取算子与存储体的对应关系。考虑到语音算法存在多重嵌套过程调用,每次过程调用时都可能发生存储体交叉访问的情况,因此设计了6层段寄存器阵列分别标·代表“或”操作识每次调用时存取算子与Rij表示第i层第j个段寄存器存储体的对应关系,如图4所示。执行过程调用指令时,段寄存器被重新配置,同时将过程调用的嵌套次数保存在层计数器。通过对层计数器输出的译码,产生段寄存器的层控制信息,包括段寄存器使能和段寄存器输出选择控制。通过段寄存器阵列的变换,实现每个存取算子对存储体访问的控制转换.再经过段译码器译码及逻辑运算产生存储体控制信号。例如,存储体RAMI使能信号(RAM1_E)可由5个段译码器译码产生的RAMl控制信号做逻辑“或”运算产生,变换逻辑运算即可以产生存储体的读写信号、地址控制信号和输入输出选择控制信号(本文不做详细论述)。

3 技术特点

(1)TR600芯片体系结构中重叠寄存器窗口技术采用可重组思想设计寄存器堆结构,提高了存储灵活性,适应了语音算法在过程调用中数据规格多样性的特点;多层窗口寄存器结构和寄存器堆局部可见的特点,解决了过程调用时的现场保护和参数传递问题,不需要设计现场保护参数的专用部件,减少了系统的时空开销。

(2)存储体交叉访问机制采用段寄存器标识存取算子与存储体的对应关系,由过程调用指令配置段寄存器.避免了因为参数传递而进行的存储体之间的数据转移;同时提供了清晰易读、编程灵活的指令界面,屏蔽了逻辑设计的复杂性,方便了用户指令编程。但过程调用功能的硬件实现与应用环境及体系结构是密不可分的,设计者应依据具体情况调整实现方案,如窗口寄存器堆的分层数目及段寄存器的层数,要根据具体算法中过程调用的最大嵌套层数而定,存取算子对存储体的交叉访问要依据体系结构提供的指令界面而定等,因为这些设计都具有灵活性和多样性。

本文论述的过程调用功能硬件实现方法也可以为其他应用设计借鉴,例如.在网络体系结构中,对多种通信协议的硬件实现以及RPC远程过程调用的实现都具有一定的参考价值。

- 单芯片集成电路优化自适应转向大灯系统的设计 (07-12)

- 基于FPGA的液晶显示控制器设计(02-17)

- DJ1001-063一风扇单片微电脑集成电路图(04-09)

- 嵌入式系统是嵌入式软件与IC发展基础(11-03)

- 应用处理器连接汽车和消费电子两大领域(02-26)

- ARM、FPGA和DSP的特点和区别是什么?(05-08)