基于FPGA的液晶显示控制器设计

液晶显示器由于具有低压、微功耗、显示信息量大、体积小等特点,在移动通信终端、便携计算机、GPS卫星定位系统等领域有广泛用途,成为使用量最大的显示器件。液晶显示控制器作为液晶驱动电路的核心部件通常由集成电路组成,通过为液晶显示系统提供时序信号和显示数据来实现液晶显示。本设计是一种基于FPGA(现场可编程门阵列)的液晶显示控制器。与集成电路控制器相比,FPGA更加灵活,可以针对小同的液晶显示模块更改时序信号和显示数据。FPGA的集成度、复杂度和面积优势使得其日益成为一种颇具吸引力的高性价比ASIC替代方案。本文选用Xilinx公司的SpananIII系列XC3S200器件,利用硬件描述语言Verilog设计了液晶显示拧制器,实现了替代专用集成电路驱动控制LCD的作用。

1 功能分析与设计要求

液晶显示模块(LCM)采用深圳拓扑微LM2028、STN图形点阵液晶显示模块,5.7in,320×240点阵,逻辑电压输入为3.0~5.0V,4位控制接口,具有行列驱动电路,白光LED背光源。表l为该液晶显示模块的引脚功能描述。

液晶显示器的扫描方式是逐行扫描,当一行被选通以后,这一行中的各列信号同时加到列上,并维持一个扫描行的时间。这一行维持时间结束后,即选通下一行,同时各列电极也施加下一行的显示电压。

列驱动器逻辑电路由移位寄存器和锁存器构成,在一个显示数据位移脉冲信号CP作用下,将一组显示数据(4位)位移到寄存器中并保持。当下一个CP到来后。移位寄存器中第1位显示数据被移至第2位,这样在80个CP脉冲作用下,一行显示数据被存入寄存器后,寄存器并口对接锁存器,在锁存脉冲LP的作用下,该行数据被锁存到锁存器内输出给列电极。锁存脉冲LP的间隔为一个行周期,而行移位脉冲间隔也为一个行周期,因此二者是一致的。

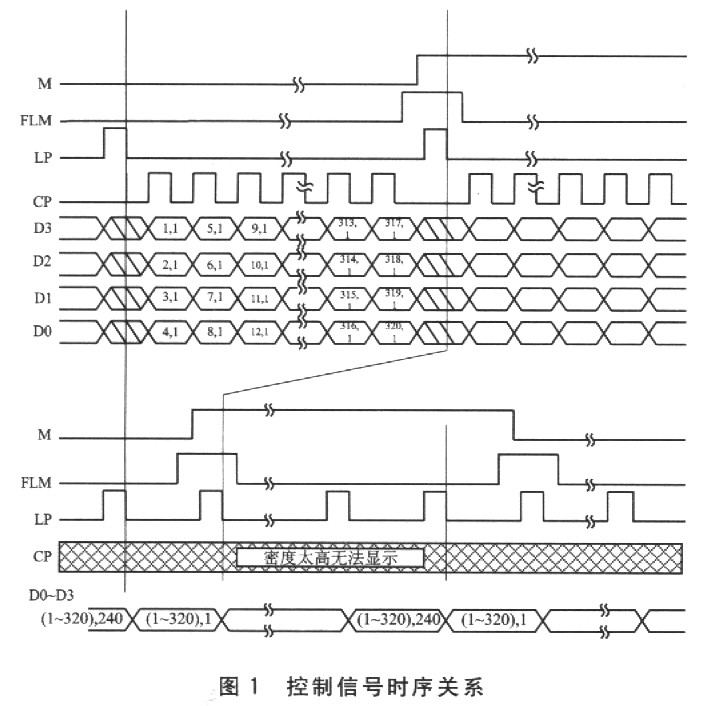

帧扫描信号FLM即为行选通信号,脉宽为一行时间,在行移位脉冲LP作用下,存入移位寄存器后逐行位移,在一帧的最后一行输出高电平,代表下一帧的开始。M为液晶显示交流驱动波形信号,即一帧改变一次波形的极性,防止液晶单方向扭曲变形。更为详细的时序关系如图1所示。

2 设计与实现

2.1 液晶控制器总体设计

本设计的液晶显示器刷新频率为70 Hz,每一帧周期为14.28ms,每一行周期为60μs,时钟信号CP的频率为2 MHz,将一行数据输入列移位寄存器的时间为40μs,因此每一行设计了20μs的空白时间。

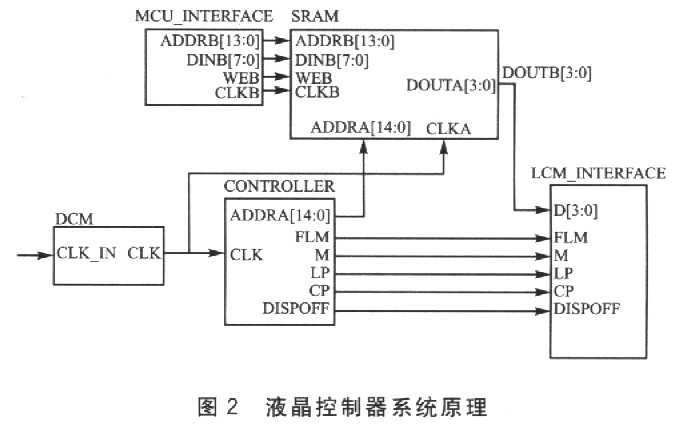

液晶控制器系统原理如图2所示。时钟模块采用Xilinx公司的Coregen IP工具定制,数字时钟管理器DCM模块将FPGA 50 MHz时钟信号CLK_IN 25分频为2 MHz控制器时钟信号CLK。DCM采用了数字延迟锁相环技术来消除时钟相位的位移,提供比自行分频更稳定的时钟信号,以满足控制系统要求。CONTROLLER模块为LCM提供满足图l所示时序要求的控制信号CP、LP、FLM、M、DISPOFF,并且同步产生SRAM的读地址ADDRA[14:0]。

SRAM为内存模块。为了提高输入LCD的数据流速度.设计了32K×4位的舣端口内存,可同时实现读/写,并实现数据格式的转化,由上位机MCU输入的8位数据转为输入LCM列驱动器的4位数据;B端口由MCU_INTERFACE与上位机MCU连接,由MCU微控制器将显示数据写入内存SRAM。其中,ADDRB[13:0]控制16K×8位的写地址,DINB[7:O]为写入数据,WEB为写有效控制,CLKB为写时钟;A端口由CONTROLLER模块控制读地址ADDRA[14:0],读时钟CLKA由系统时钟信号CLK控制,DOUTA[3:0]将数据写入LCM列驱动器。

2.2 控制模块设计

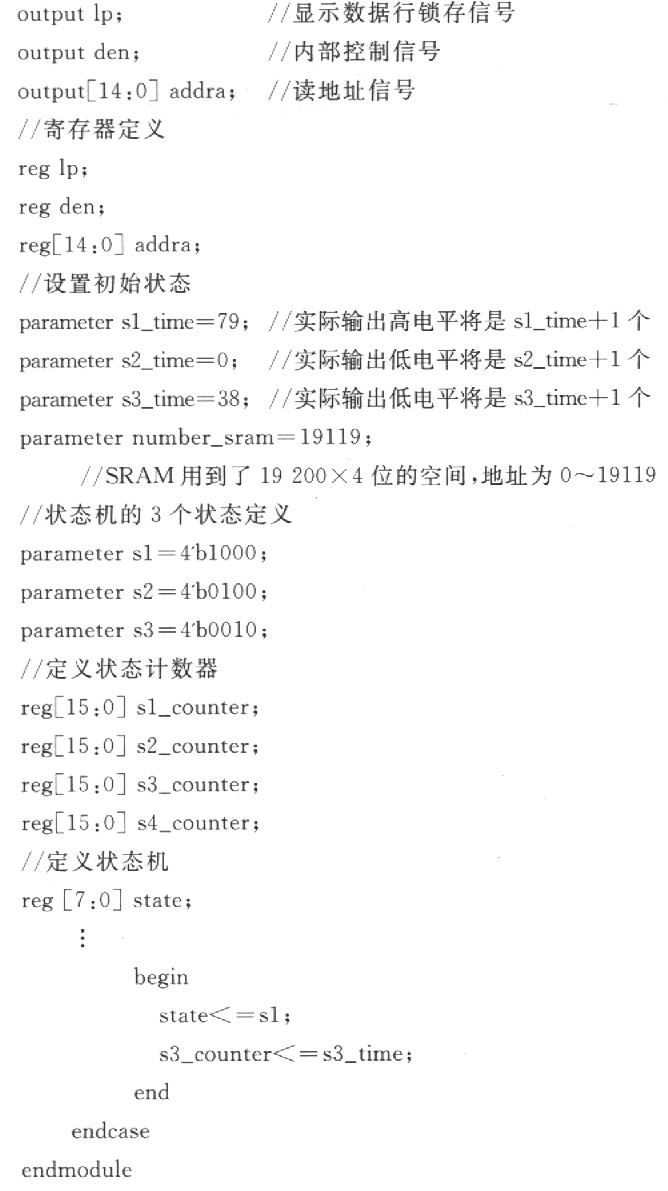

应用状态机的方法,用Verilog硬件描述语言设计控制模块CONTROLLER。CLK为2 MHz输入时钟信号。LP和内部控制信号DEN由状态机1控制产生,FLM由状态机2控制产生,M由状态机3控制产生,CP信号和ADDRA[14:0]根据CLK和DEN信号控制得到。状态机1有3个状态:状态1,LP为O,DEN为1,持续80个CLK脉冲后转向状态2;状态2,LP为l,DEN为0,持续1个CLK脉冲后转向状态3;状态3,LP为O,DEN为O,持续39个CLK脉冲后转向状态1。状态机2有2个状态:状态1,FLM为l,持续1个LP周期时间,即120个CLK脉冲;状态2,FLM为O,持续剩下的239个LP周期,即28 680个CLK脉冲。状态机3有2个状态,状态l,M为1。持续1个FLM周期时间,即28800个CLK脉冲;状态2,M为0,也持续1个FLM周期时间。CP信号和ADDRA由于含有空白信号,所以由内部控制信号DEN和时钟信号CLK得到。以下为设计的源代码初始化部分:

3 仿真、下载测试分析

在ISE6.3环境下完成控制器设计后,在MODELSIM6.1b环境下完成仿真测试,波形

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 从LCD电极读数的单片机接口技术(01-15)

- 嵌入式Linux下彩色LCD驱动的设计与实现(03-09)

- LCD部分专业术语解释(03-06)

- 点阵LCD的驱动显控原理(上册)(03-20)

- LG选用赛普拉斯CapSense 触摸感应解决方案(05-03)