基于AD9238的高速高精度ADC采集系统

时间:07-23

来源:互联网

点击:

3 系统的具体实现

运行时,若AD9238的SENSE接地,系统将采用内部基准(VREF=1 V),此时的输入差分模拟信号范围为VPP。如将DFS接高,则AD输出数据的格式为二进制补码。

MUX_SESECT接高电平,则可保证A通道数据从通道A输出,B通道数据从通道B输出。AD9238的OEBA、OEBB由MCU控制。

为了使两个通道AD同时工作,提高系统效率。设计时可采用两个FIFO来独立地将两路AD输出数据进行存储。由于AD的数据输出为12位,FIFO存储宽度为18位,故可将FIFO输入端的空脚接地,输出端空脚悬空。

将AD时钟(本设计采用40 MHz)直接与FIFO的WCLK相连,可使FIFO同步将AD采样数据写入,实际上.FIFO的RCLK由MCU控制,FIFO的WEN、REN也由MCU控制。

FIFO的满标志(FF)应接到MCU的外部中断引脚。同时,FF与MCU的控制信号(CONTROL)会通过与非门共同作用于AD的PDWN引脚。MCU通过CONTROL来控制AD的启动。当CONTROL为1时,若FF为1(FIFO不为写满状态)且与非门输出PDWN为0,则启动AD转换;若FF为0且PDWN为0,则关闭AD转换。而如CONTROL为0,无论FF状态如何,PDWN均为0,即不启动AD转换。

AD转换启动后,若FIFO写满,则为0,这样,PDWN也为0,此时硬件将AD通道关闭。同时,MCU进人中断服务程序并读FIFO,然后通过USB总线将读得的数据传给PC机。

将FIFO12位输出数据的高4位和低8位分别接到锁存芯片74HC574,并将74HC574的输出端接到AN2131Q的数据总线上,AN2131Q便可通过片选信号选通要读的FIFO和74HC574,然后分两字节将12位数据读入。

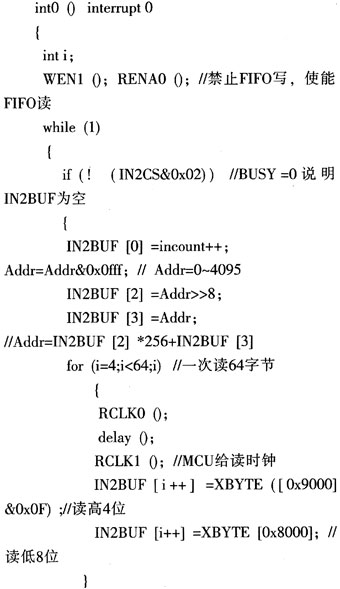

AN2131Q的数据总线和地址总线是独立的,访问外部数据存储器可直接通过一条MOVX指令来实现。USB传输采用块传输,一次传输的最大字节数为64。进入中断程序的源代码如下:

4 系统PCB设计注意事项

4.1 电源和地线的处理

为了降低并抑制整个系统的噪声,其系统电源和地的处理尤为重要。采用的方法是在电源、地线之间加去耦电容。设计时应在每个电源引脚都就近接上去耦电容,并尽量加宽电源、地线宽度,最好是地线比电源线宽。数字电路部分可用大面积铜层做地线,并在板上把没有用上的地方都与地相连接,以作为地线使用。

4.2 模拟电路和数字电路的共地处理

本系统是由数字电路和模拟电路混合构成的,因此,在PCB设计时要考虑他们之间的互相干扰问题。对信号线来说,高频信号线要尽可能远离敏感的模拟电路器件,而且走线要尽可能短而等长。对地线来说,板内数字地和模拟地是分开的,应采用单点接地的方式,并通过一个磁珠将两者连接起来。事实上,整个PCB对外界应只有一个结点。

4.3 过孔的处理

高速数字电路中,过孔的寄生电感往往会给电路带来较大的负面影响。因此,在PCB设计中尽量做到以下几点:

(1) PCB板上的信号走线尽量不换层,也就是说,尽量不要使用不必要的过孔。

(2) 电源和地要就近打过孔,过孔和管脚之间的引线越短越好,因为它们会导致电感的增加。

(3) 在信号换层的过孔附近放置一些接地的过孔,以便为信号提供最近的回路。

5 系统性能分析

高速数据采集系统的动态性能指标主要包括INL、DNL、SNR、SINAD和有效位数(ENOB)等。在本系统的测试过程中,AD采样时钟为40MHz且输入信号为20 kHz的正弦信号时,其实际测试功率谱的密度如图2所示。

图2中,主频率集中在20 kHz处,同时还有一些噪声频率,最大能量值为73.95。利用Matlab软件可以计算出SINAD为63.2 dB。根据ENOB=(SINAD-1.76)/6.02,可得出:ENOB为10.5。当输入为0 V时,理论上的AD输出值应为7FF,而实际测得的输出数据的平均值为7FB,由此可求出其偏移误差为04H;同样,输人为1 V时,测得系统的增益误差为03H。AD转换位数为12位。而被设置为1 V,则转换精度为1 V/212=0.024 mV。

6 结束语

经测试分析,本系统能对单一频率的模拟信号准确地进行数据采集和恢复。由于本系统AD的最大采样速率是40 MHz,FIFO深度为4 KB,故对速率在7.5 kHz~20 MHz的信号,写满一次FIFO足已使采样点多于一个周期,又不至出现混叠,这样就可以准确地恢复出信号。当然,为了满足各个频率范围内模拟信号的采样,也可以考虑扩大FIFO深度、改变AD采样时钟频率。总之,本文提出的这种由MCU、FIFO实现的采集系统方案比较简单,且实用可靠。

运行时,若AD9238的SENSE接地,系统将采用内部基准(VREF=1 V),此时的输入差分模拟信号范围为VPP。如将DFS接高,则AD输出数据的格式为二进制补码。

MUX_SESECT接高电平,则可保证A通道数据从通道A输出,B通道数据从通道B输出。AD9238的OEBA、OEBB由MCU控制。

为了使两个通道AD同时工作,提高系统效率。设计时可采用两个FIFO来独立地将两路AD输出数据进行存储。由于AD的数据输出为12位,FIFO存储宽度为18位,故可将FIFO输入端的空脚接地,输出端空脚悬空。

将AD时钟(本设计采用40 MHz)直接与FIFO的WCLK相连,可使FIFO同步将AD采样数据写入,实际上.FIFO的RCLK由MCU控制,FIFO的WEN、REN也由MCU控制。

FIFO的满标志(FF)应接到MCU的外部中断引脚。同时,FF与MCU的控制信号(CONTROL)会通过与非门共同作用于AD的PDWN引脚。MCU通过CONTROL来控制AD的启动。当CONTROL为1时,若FF为1(FIFO不为写满状态)且与非门输出PDWN为0,则启动AD转换;若FF为0且PDWN为0,则关闭AD转换。而如CONTROL为0,无论FF状态如何,PDWN均为0,即不启动AD转换。

AD转换启动后,若FIFO写满,则为0,这样,PDWN也为0,此时硬件将AD通道关闭。同时,MCU进人中断服务程序并读FIFO,然后通过USB总线将读得的数据传给PC机。

将FIFO12位输出数据的高4位和低8位分别接到锁存芯片74HC574,并将74HC574的输出端接到AN2131Q的数据总线上,AN2131Q便可通过片选信号选通要读的FIFO和74HC574,然后分两字节将12位数据读入。

AN2131Q的数据总线和地址总线是独立的,访问外部数据存储器可直接通过一条MOVX指令来实现。USB传输采用块传输,一次传输的最大字节数为64。进入中断程序的源代码如下:

4 系统PCB设计注意事项

4.1 电源和地线的处理

为了降低并抑制整个系统的噪声,其系统电源和地的处理尤为重要。采用的方法是在电源、地线之间加去耦电容。设计时应在每个电源引脚都就近接上去耦电容,并尽量加宽电源、地线宽度,最好是地线比电源线宽。数字电路部分可用大面积铜层做地线,并在板上把没有用上的地方都与地相连接,以作为地线使用。

4.2 模拟电路和数字电路的共地处理

本系统是由数字电路和模拟电路混合构成的,因此,在PCB设计时要考虑他们之间的互相干扰问题。对信号线来说,高频信号线要尽可能远离敏感的模拟电路器件,而且走线要尽可能短而等长。对地线来说,板内数字地和模拟地是分开的,应采用单点接地的方式,并通过一个磁珠将两者连接起来。事实上,整个PCB对外界应只有一个结点。

4.3 过孔的处理

高速数字电路中,过孔的寄生电感往往会给电路带来较大的负面影响。因此,在PCB设计中尽量做到以下几点:

(1) PCB板上的信号走线尽量不换层,也就是说,尽量不要使用不必要的过孔。

(2) 电源和地要就近打过孔,过孔和管脚之间的引线越短越好,因为它们会导致电感的增加。

(3) 在信号换层的过孔附近放置一些接地的过孔,以便为信号提供最近的回路。

5 系统性能分析

高速数据采集系统的动态性能指标主要包括INL、DNL、SNR、SINAD和有效位数(ENOB)等。在本系统的测试过程中,AD采样时钟为40MHz且输入信号为20 kHz的正弦信号时,其实际测试功率谱的密度如图2所示。

图2中,主频率集中在20 kHz处,同时还有一些噪声频率,最大能量值为73.95。利用Matlab软件可以计算出SINAD为63.2 dB。根据ENOB=(SINAD-1.76)/6.02,可得出:ENOB为10.5。当输入为0 V时,理论上的AD输出值应为7FF,而实际测得的输出数据的平均值为7FB,由此可求出其偏移误差为04H;同样,输人为1 V时,测得系统的增益误差为03H。AD转换位数为12位。而被设置为1 V,则转换精度为1 V/212=0.024 mV。

6 结束语

经测试分析,本系统能对单一频率的模拟信号准确地进行数据采集和恢复。由于本系统AD的最大采样速率是40 MHz,FIFO深度为4 KB,故对速率在7.5 kHz~20 MHz的信号,写满一次FIFO足已使采样点多于一个周期,又不至出现混叠,这样就可以准确地恢复出信号。当然,为了满足各个频率范围内模拟信号的采样,也可以考虑扩大FIFO深度、改变AD采样时钟频率。总之,本文提出的这种由MCU、FIFO实现的采集系统方案比较简单,且实用可靠。

电子 FPGA DSP MCU 电路 USB Cypress 总线 收发器 ADI ADC 电压 CMOS 电阻 放大器 PCB 电容 模拟电路 电感 相关文章:

- 利用蓝牙技术和远程信息控制单元实现汽车诊断(11-13)

- 六大特点助CMOS图像传感器席卷医疗电子应用(11-13)

- 汽车网络的分类及发展趋向(11-13)

- 多核嵌入式处理技术推动汽车技术发展(11-18)

- CAN总线的客车轻便换档系统设计与实现(02-13)

- 高性能嵌入式ARM MPU在医疗电子系统中的设计应用(05-12)