用耦合线圈拓扑改善双相降压转换器的性能

时间:01-05

来源:互联网

点击:

电容问题

输入电容用于降低从直流输入电源吸收的峰值电流,降低电路的开关操作所引入的噪声和纹波电压。输入电容必须使开关电容造成的纹波电流满足要求,应使用低ESR (等效串联电阻)的铝电解电容或陶瓷电容,避免出现较大的负载跃变时在输出端产生较大的电压瞬变。应仔细考量供应商给出的纹波电流规格对应的温度降额,一般允许10°C至20°C的温升。此外,可以利用多个小电感值、低ESL(等效串联电感)的电容并联,以降低高频振荡。

选择输出电容的关键参数是实际电容值、ESR、ESL和额定电压。这些参数会影响系统的整体稳定性、输出电压纹波以及瞬态响应,输出纹波电压包含三部分,即输出电容储存电荷的变化,电流流入、流出电容时在ESR和ESL上产生的压降。下面给出了选择电容使用的公式。

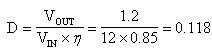

设计计算

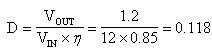

1.开启条件

VIN = 12V;VOUT = 1.2V;IOUT = 50A;η = 0.85

工作频率 = 400kHz;N = 2

N = 相数;η = 效率因子

2.电感值计算

从计算转换器功耗和输入电流入手:

POUT = VOUT x IOUT

PIN = POUT / η

PDISS = PIN – POUT

60W = 1.2V x 50A

70.58W = 60W/0.85

因此:

PDISS = 10.58W (70.58W – 60W)

IIN(AV) = PIN/VIN = 70.58W/12V = 5.882A

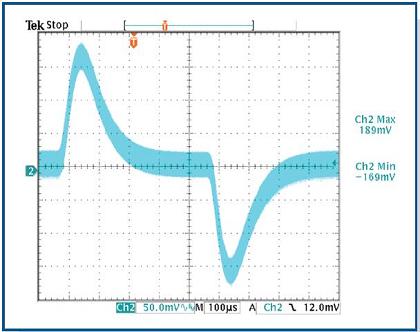

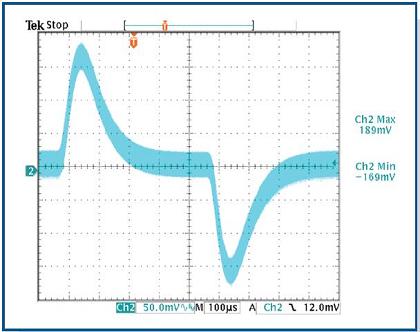

图4a:两相板,使用两个独立电感。瞬变负载;Ch2:输出电压;VIN = 12V;VOUT = 1.2V/5A–25A–5A。

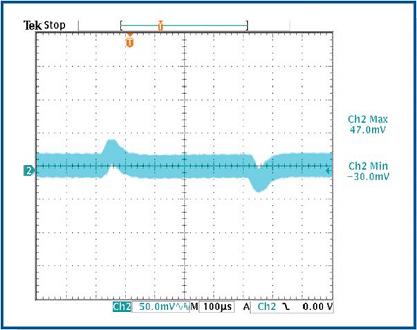

图4b:两相板,使用两个独立电感。瞬变负载;Ch2:输出电压;VIN = 12V;VOUT = 1.2V/5A–25A–5A。

图4:图中波形表示错相工作条件下,使用两个独立电感(4a)和使用一组耦合线圈(4b)情况下的瞬态响应。

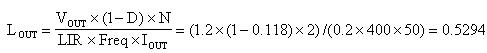

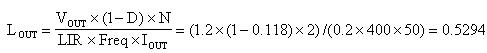

接下来,计算输出电感值:

LIR = 电感纹波电流系数 =⊿I/IOUT = 0.2

可以求解⊿I → 0.2 x IOUT (计算输出纹波时需要)。

商用化电感中最接近的电感值是0.56μH,直流电阻为0.0017欧姆。

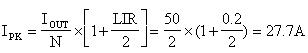

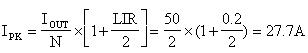

3.计算峰值电流

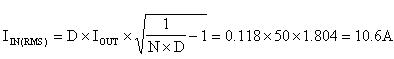

计算输入电容(CIN)

N x D = 0.235,N x D < 1

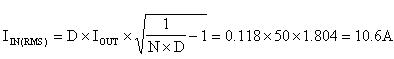

其中,IIN(RMS)为流过输入电容的纹波电流RMS值。

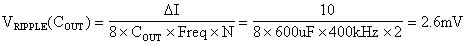

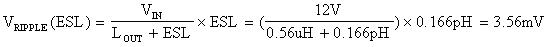

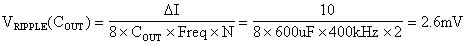

4.计算输出纹波电压(VRIPPLE)

假设:

ESR = (2.5/6) × 10-3 (输出电容的ESR)

ESL = (1/6) × 10-9 (输出电容的寄生电感ESL)

COUT = 600μF

计算VRIPPLE:

VRIPPLE (ESR) = ⊿I × ESR = 10 × 0.416 × 10-3 = 4.16mV

因此,总纹波电压VRIPPLE为:VRIPPLE (COUT) + VRIPPLE (ESL) + VRIPPLE (ESR)

得到:VRIPPLE = 10mV左右

耦合线圈拓扑对性能的改善

图4a和图4b给出了使用耦合线圈拓扑和两个独立电感情况下瞬态负载响应特性的对照,由于在耦合线圈架构中瞬态负载响应仅受漏感的制约,与自感无关,所以,采用耦合线圈拓扑大大提高了瞬态响应特性。设计中没有降低每相的电感。

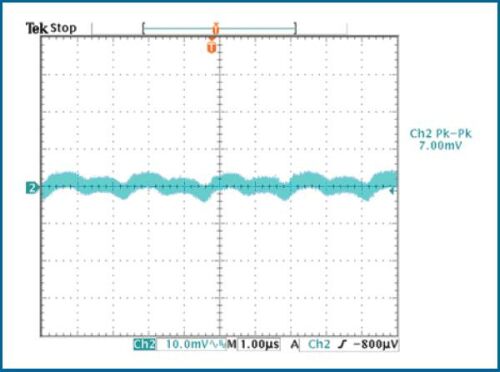

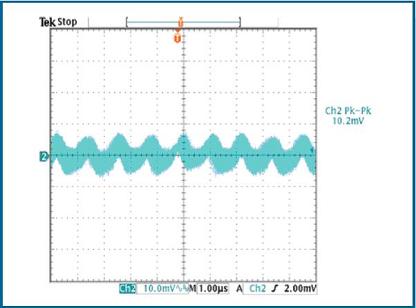

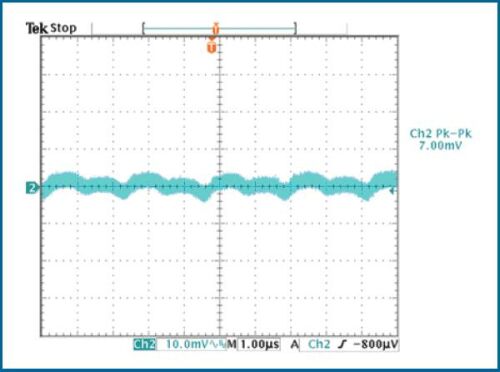

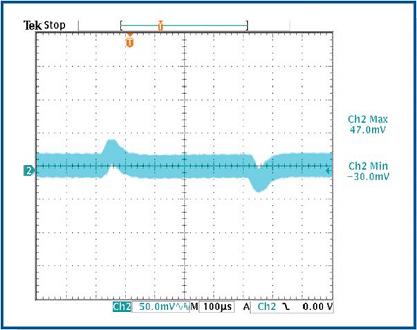

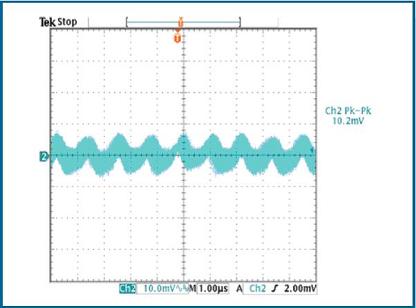

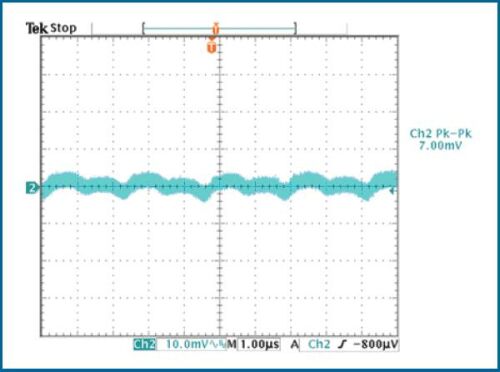

图5a

图5b

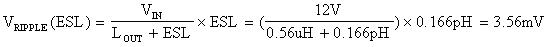

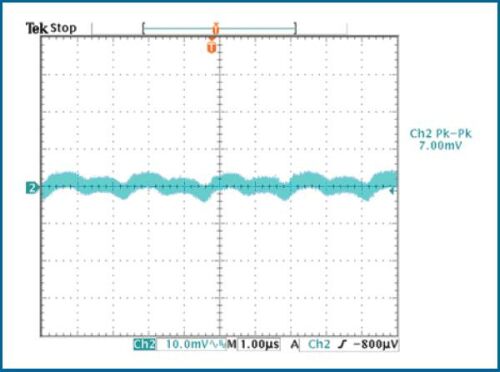

图5:使用耦合电感(耦合线圈,5a)时的输出纹波远远低于使用两个独立电感(独立线圈,5b)情况下的纹波。

图5a和图5b所示波形是两种架构下的输出电压纹波,图6所示曲线为耦合、非耦合两相转换器的效率对照。从中可以看出耦合线圈架构对效率的改善,空载时耦合线圈架构消耗较大电流,所以,轻载时耦合线圈架构效率较低;重载时,耦合线圈拓扑能够提供更高效率。

图6:使用耦合电感时,重载下能够提供更高效率;轻载下使用两个独立电感的驱动器效率略高一些。

作者:美信集成产品公司战略应用工程师Sunil Akre

输入电容用于降低从直流输入电源吸收的峰值电流,降低电路的开关操作所引入的噪声和纹波电压。输入电容必须使开关电容造成的纹波电流满足要求,应使用低ESR (等效串联电阻)的铝电解电容或陶瓷电容,避免出现较大的负载跃变时在输出端产生较大的电压瞬变。应仔细考量供应商给出的纹波电流规格对应的温度降额,一般允许10°C至20°C的温升。此外,可以利用多个小电感值、低ESL(等效串联电感)的电容并联,以降低高频振荡。

选择输出电容的关键参数是实际电容值、ESR、ESL和额定电压。这些参数会影响系统的整体稳定性、输出电压纹波以及瞬态响应,输出纹波电压包含三部分,即输出电容储存电荷的变化,电流流入、流出电容时在ESR和ESL上产生的压降。下面给出了选择电容使用的公式。

设计计算

1.开启条件

VIN = 12V;VOUT = 1.2V;IOUT = 50A;η = 0.85

工作频率 = 400kHz;N = 2

N = 相数;η = 效率因子

2.电感值计算

从计算转换器功耗和输入电流入手:

POUT = VOUT x IOUT

PIN = POUT / η

PDISS = PIN – POUT

60W = 1.2V x 50A

70.58W = 60W/0.85

因此:

PDISS = 10.58W (70.58W – 60W)

IIN(AV) = PIN/VIN = 70.58W/12V = 5.882A

图4a:两相板,使用两个独立电感。瞬变负载;Ch2:输出电压;VIN = 12V;VOUT = 1.2V/5A–25A–5A。

图4b:两相板,使用两个独立电感。瞬变负载;Ch2:输出电压;VIN = 12V;VOUT = 1.2V/5A–25A–5A。

图4:图中波形表示错相工作条件下,使用两个独立电感(4a)和使用一组耦合线圈(4b)情况下的瞬态响应。

接下来,计算输出电感值:

LIR = 电感纹波电流系数 =⊿I/IOUT = 0.2

可以求解⊿I → 0.2 x IOUT (计算输出纹波时需要)。

商用化电感中最接近的电感值是0.56μH,直流电阻为0.0017欧姆。

3.计算峰值电流

计算输入电容(CIN)

N x D = 0.235,N x D < 1

其中,IIN(RMS)为流过输入电容的纹波电流RMS值。

4.计算输出纹波电压(VRIPPLE)

假设:

ESR = (2.5/6) × 10-3 (输出电容的ESR)

ESL = (1/6) × 10-9 (输出电容的寄生电感ESL)

COUT = 600μF

计算VRIPPLE:

VRIPPLE (ESR) = ⊿I × ESR = 10 × 0.416 × 10-3 = 4.16mV

因此,总纹波电压VRIPPLE为:VRIPPLE (COUT) + VRIPPLE (ESL) + VRIPPLE (ESR)

得到:VRIPPLE = 10mV左右

耦合线圈拓扑对性能的改善

图4a和图4b给出了使用耦合线圈拓扑和两个独立电感情况下瞬态负载响应特性的对照,由于在耦合线圈架构中瞬态负载响应仅受漏感的制约,与自感无关,所以,采用耦合线圈拓扑大大提高了瞬态响应特性。设计中没有降低每相的电感。

图5a

图5b

图5:使用耦合电感(耦合线圈,5a)时的输出纹波远远低于使用两个独立电感(独立线圈,5b)情况下的纹波。

图5a和图5b所示波形是两种架构下的输出电压纹波,图6所示曲线为耦合、非耦合两相转换器的效率对照。从中可以看出耦合线圈架构对效率的改善,空载时耦合线圈架构消耗较大电流,所以,轻载时耦合线圈架构效率较低;重载时,耦合线圈拓扑能够提供更高效率。

图6:使用耦合电感时,重载下能够提供更高效率;轻载下使用两个独立电感的驱动器效率略高一些。

作者:美信集成产品公司战略应用工程师Sunil Akre

电路 电感 电流 电压 总线 电容 PWM MOSFET Vishay 电阻 相关文章:

- 基于P89C61x2/ISP1581的USB接口电路的设计(02-13)

- 行波管关断方式对应用系统可靠性的影响(06-24)

- 基于VME总线的RDC接口电路设计(06-29)

- 单芯片集成电路优化自适应转向大灯系统的设计 (07-12)

- 单片机应用系统的抗干扰技术(08-07)

- 基于FPGA的线阵CCD驱动器设计(11-26)