H.264中插补算法的VLSI设计与实现

时间:12-20

来源:互联网

点击:

H.264/AVC是由ITU和ISO/IEC的专家共同组成的联合视频小组JVT(Joint Video Team)发展和制定的新一代视频编码国际标准。在相同的视觉感知质量下,H.264的传输码率比以往的H.263、MPEG-4等降低了50%左右。

运动矢量位移的精度越高,则帧间剩余误差越小,压缩比越高。H.263中采用了半像素估计,在H.264中则进一步采用1/4像素精度的运动估计。分数运动估计和运动补偿用到的非整数像素点必须通过插补(interpolation)运算来实现,因而插补运算的硬件加速对整个H.264编解码系统性能的提高有重要意义。在H.264中采用了6抽头FIR滤波器的内插获得1/2像素位置的值,则1/4像素值可通过线性内插获得。而对于常用的4:2:0的视频格式,亮度信号的1/4像素精度对应于色度的1/8像素的运动矢量,因此需要对色度信号进行1/8像素的插补运算。在H.264的帧间预测中,4×4是最基本的处理单元,其7种模式都可以划分为4×4块来进行处理,因而基于面积和时间考虑的4×4模块的插补电路具有良好的可重用性。

文献提出了使用4抽头滤波器取代6抽头滤波器的算法来实现亮度的1/2像素插补,利于硬件实现。本文在4抽头滤波器的基础上提出了可以处理4×4块的流水线结构,可以在一个时钟内完成27个1/2像素位置的插补运算。对色度1/8像素的插补,本文提出的两级处理的结构,巧妙地利用移位器和加法器取代了乘法器,节省了硬件开支。

1 插补算法原理

插补原理示意图如图1所示。2个整数像素位置之间的1/2像素点像素如图1(a)中的a、b、aa等,是利用一个带权重的6抽头有限冲击响应(FIR)滤波器对相邻整数位置的像素值进行内插得到的,权重值是(1/32,-5/32,5/8,5/8,-5/32,1/32)。如:

a=round((A-5*B+20*C+20*D-5*E+F)/32)(1)

h=round((A-5*G+20*H+20*I-5*J+K)/32)(2)

aa=round((a-5*b+20*c+20*d-5*e+f)/32)(3)

=round((h-5*i+20*j+20*k-5*l+m)/32)

由于6抽头FIR的结构比较复杂,文献提出的权重值为(-1/8,5/8,5/8,-1/8)4抽头FIR在对图像质量和比特率影响很小的情况下,可以很大程度地节省硬件资源。如图1(b)中:

a=round((-1*B+5*C+5*D-1*E)/8)(4)

h=round((-1*G+5*H+5*I-1*J)/8)(5)

aa=round((-1*b+5*c+5*d-1*e)/8)(6)

=round((-1*i+5*j+5*k-1*l)/8)

最匹配的1/2像素位置确定以后,1/4像素位置的像素由周围的整数像素位置像素和1/2像素位置像素线性插补得到。

在常用的4:2:0采样中,亮度分量1/4像素精度的运动矢量应用到色度分量需要1/8的像素精度。在色度空间,对整数位置的像素值进行线性插补可以得到1/8像素精度的插补值。如图1(b)所示,1/8像素位置的像素a是周围整数位置像素A,B,C,D的线性组合:

a=round(8-x)*(8-y)*A+x*(8-y)*B+y*(8-x)*C+x*y*D/64 (7)

2 硬件结构

2.1 亮度1/2像素插补电路

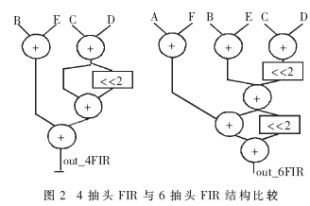

4抽头FIR与6抽头FIR结构比较如图2所示。由图2可以看出,4抽头FIR的结构比6抽头FIR易于硬件实现。实验表明前者的电路面积和关键路径延时比后者分别减少了36.2%和16.0%。

4×4块的1/2像素精度插补电路的流水线结构图如图3所示,共有16个4抽头FIR,利用一个6× 4的整数像素点阵列作为缓冲区,每次从存储器中读出8个整数像素点,分别用于5个水平4抽头FIR的输入。每个时钟所有的像素点都会向下传送一级,图中虚线框处已经计算出了整数像素点周围的所有27个1/2像素值,可以输出到并行处理单元同时计算9个半像素位置的SAD(Sum of Absolute Difference)。该架构处理一个4×4单元需要8个时钟,处理一个具有相同运动矢量的4×16块需要20个时钟。

亮度1/4像素的线性插补可以用一个加法器和一个移位器实现。图4为4×4块1/4像素插补电路的结构图,采用两级流水线,输入部分为18个像素点,利用线性插补生成所需要的1/4像素位置像素。在图中虚线框部分可以计算出最佳1/2像素点周围的所 有1/4像素点,输出给并行处理单元计算9个1/4像素位置的SAD。该架构完成一个4×4单元需要6个时钟,完成一个具有相同运动矢量的4×16块需要18个时钟。

H.264的帧间预测中,一个宏块(MB)可划分成16×16、16×8、8×16、8×8、8× 4、4×8、4×4不同模式。这7种模式都可以划分为16个4×4块分别进行处理。具有相同整像素运动矢量的纵向相邻4×4块可以连续处理以节省时钟数。表1列出了亮度为1/2像素插补和1/4像素插补时流水线处理一个宏块不同模式分别需要的时钟数。

2.3 色度1/8像素插补电路

如果利用乘法器来实现色度1/8像素精度的插补电路,对每一个点的插补运算都要用到8个乘法器,无论是面积还是时间都会有很大的开销。变换公式(7)可得公式(8),可以看出其中含有如(9)式所示的公共运算单元。

a=round{{(8-y)[(8-x)×A+x×B]+y[(8-x)×C+x×D]}/64}(8)

cf=(8-h)×M+h×N(9)

硬件设计采用两级处理的结构,采用图5所示的CU单元处理公式(9),色度1/8插补电路结构如图6所示。由于该结构的两级间比较平衡,非常容易插入寄存器以减少关键路径的延时。

运动矢量位移的精度越高,则帧间剩余误差越小,压缩比越高。H.263中采用了半像素估计,在H.264中则进一步采用1/4像素精度的运动估计。分数运动估计和运动补偿用到的非整数像素点必须通过插补(interpolation)运算来实现,因而插补运算的硬件加速对整个H.264编解码系统性能的提高有重要意义。在H.264中采用了6抽头FIR滤波器的内插获得1/2像素位置的值,则1/4像素值可通过线性内插获得。而对于常用的4:2:0的视频格式,亮度信号的1/4像素精度对应于色度的1/8像素的运动矢量,因此需要对色度信号进行1/8像素的插补运算。在H.264的帧间预测中,4×4是最基本的处理单元,其7种模式都可以划分为4×4块来进行处理,因而基于面积和时间考虑的4×4模块的插补电路具有良好的可重用性。

文献提出了使用4抽头滤波器取代6抽头滤波器的算法来实现亮度的1/2像素插补,利于硬件实现。本文在4抽头滤波器的基础上提出了可以处理4×4块的流水线结构,可以在一个时钟内完成27个1/2像素位置的插补运算。对色度1/8像素的插补,本文提出的两级处理的结构,巧妙地利用移位器和加法器取代了乘法器,节省了硬件开支。

1 插补算法原理

插补原理示意图如图1所示。2个整数像素位置之间的1/2像素点像素如图1(a)中的a、b、aa等,是利用一个带权重的6抽头有限冲击响应(FIR)滤波器对相邻整数位置的像素值进行内插得到的,权重值是(1/32,-5/32,5/8,5/8,-5/32,1/32)。如:

a=round((A-5*B+20*C+20*D-5*E+F)/32)(1)

h=round((A-5*G+20*H+20*I-5*J+K)/32)(2)

aa=round((a-5*b+20*c+20*d-5*e+f)/32)(3)

=round((h-5*i+20*j+20*k-5*l+m)/32)

由于6抽头FIR的结构比较复杂,文献提出的权重值为(-1/8,5/8,5/8,-1/8)4抽头FIR在对图像质量和比特率影响很小的情况下,可以很大程度地节省硬件资源。如图1(b)中:

a=round((-1*B+5*C+5*D-1*E)/8)(4)

h=round((-1*G+5*H+5*I-1*J)/8)(5)

aa=round((-1*b+5*c+5*d-1*e)/8)(6)

=round((-1*i+5*j+5*k-1*l)/8)

最匹配的1/2像素位置确定以后,1/4像素位置的像素由周围的整数像素位置像素和1/2像素位置像素线性插补得到。

在常用的4:2:0采样中,亮度分量1/4像素精度的运动矢量应用到色度分量需要1/8的像素精度。在色度空间,对整数位置的像素值进行线性插补可以得到1/8像素精度的插补值。如图1(b)所示,1/8像素位置的像素a是周围整数位置像素A,B,C,D的线性组合:

a=round(8-x)*(8-y)*A+x*(8-y)*B+y*(8-x)*C+x*y*D/64 (7)

2 硬件结构

2.1 亮度1/2像素插补电路

4抽头FIR与6抽头FIR结构比较如图2所示。由图2可以看出,4抽头FIR的结构比6抽头FIR易于硬件实现。实验表明前者的电路面积和关键路径延时比后者分别减少了36.2%和16.0%。

4×4块的1/2像素精度插补电路的流水线结构图如图3所示,共有16个4抽头FIR,利用一个6× 4的整数像素点阵列作为缓冲区,每次从存储器中读出8个整数像素点,分别用于5个水平4抽头FIR的输入。每个时钟所有的像素点都会向下传送一级,图中虚线框处已经计算出了整数像素点周围的所有27个1/2像素值,可以输出到并行处理单元同时计算9个半像素位置的SAD(Sum of Absolute Difference)。该架构处理一个4×4单元需要8个时钟,处理一个具有相同运动矢量的4×16块需要20个时钟。

亮度1/4像素的线性插补可以用一个加法器和一个移位器实现。图4为4×4块1/4像素插补电路的结构图,采用两级流水线,输入部分为18个像素点,利用线性插补生成所需要的1/4像素位置像素。在图中虚线框部分可以计算出最佳1/2像素点周围的所 有1/4像素点,输出给并行处理单元计算9个1/4像素位置的SAD。该架构完成一个4×4单元需要6个时钟,完成一个具有相同运动矢量的4×16块需要18个时钟。

H.264的帧间预测中,一个宏块(MB)可划分成16×16、16×8、8×16、8×8、8× 4、4×8、4×4不同模式。这7种模式都可以划分为16个4×4块分别进行处理。具有相同整像素运动矢量的纵向相邻4×4块可以连续处理以节省时钟数。表1列出了亮度为1/2像素插补和1/4像素插补时流水线处理一个宏块不同模式分别需要的时钟数。

2.3 色度1/8像素插补电路

如果利用乘法器来实现色度1/8像素精度的插补电路,对每一个点的插补运算都要用到8个乘法器,无论是面积还是时间都会有很大的开销。变换公式(7)可得公式(8),可以看出其中含有如(9)式所示的公共运算单元。

a=round{{(8-y)[(8-x)×A+x×B]+y[(8-x)×C+x×D]}/64}(8)

cf=(8-h)×M+h×N(9)

硬件设计采用两级处理的结构,采用图5所示的CU单元处理公式(9),色度1/8插补电路结构如图6所示。由于该结构的两级间比较平衡,非常容易插入寄存器以减少关键路径的延时。

- 便携产品电源芯片的应用技术(02-15)

- 如何设计用于标清视频信道的有源滤波器(04-11)

- 头戴耳机的可调串音电路(03-24)

- 基于I2C总线控制的音频处理电路设计(10-17)

- 新型低电容EMI滤波器为手机带来更强抗干扰性能(01-22)

- 面向LCD的电磁干扰滤波器设计 (02-17)