逻辑分析仪我也DIY(二)

时间:02-19

来源:互联网

点击:

昨晚睡觉时还寻思着为什么数据采集显示出来怎么问题多多,明明全低电平居然时不时的采集到高电平,后来想想也是,两块板子(被采集信号产生板子和模拟逻辑分析仪的板子)没有共地,采集到的电平高低没有一个参考点,判断错误也就在所难免了。于是今晚共地后,多次采集数据,都很稳定的采集到并正确的显示做测试的波形。

经过今晚的努力,把几个字模存储到了cyclone的M4K产生的ROM中,然后通过VGA坐标产生的控制逻辑进行地址译码。这部分设计没有仔细深入,可能浪费的M4K比较多(利用率比较低),但这是为了FPGA逻辑地址控制部分设计相对容易设计些。

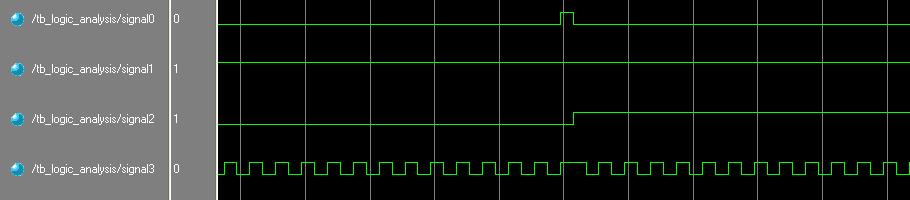

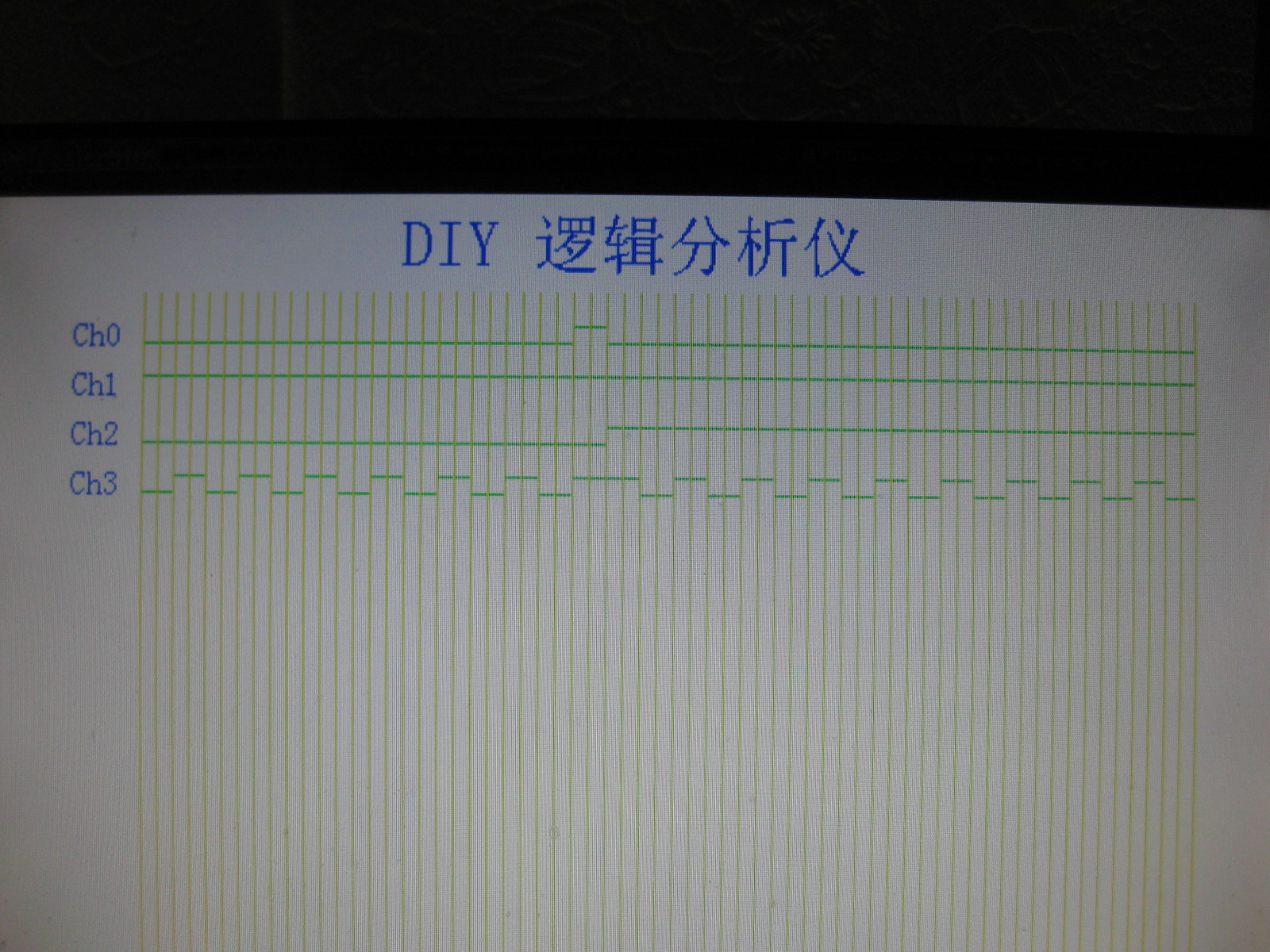

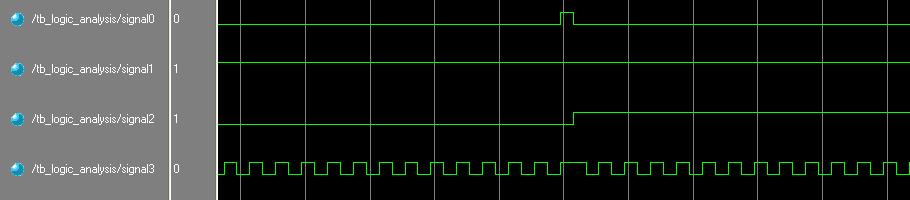

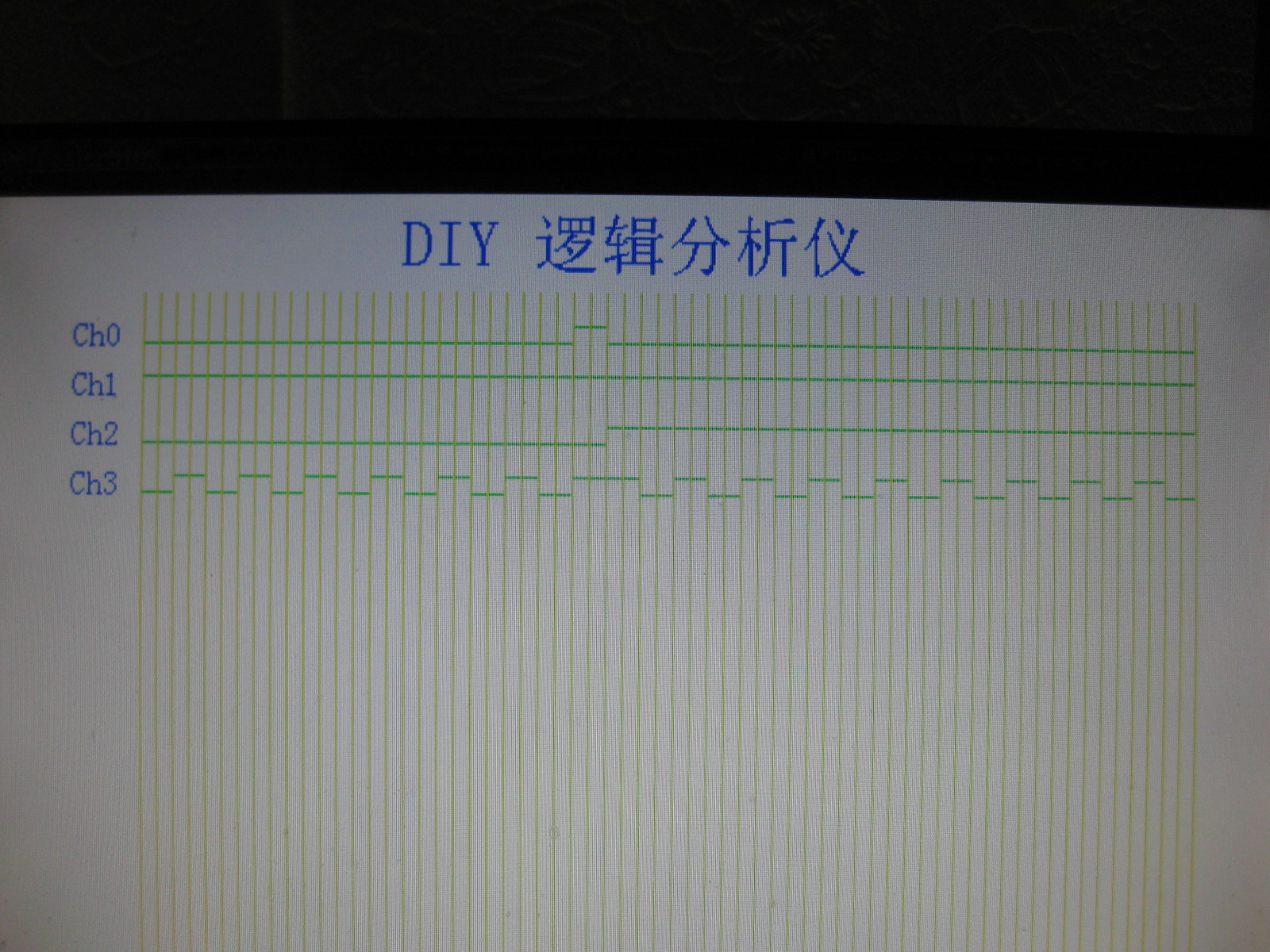

稍微对下面这个波形的采集做了测试,这个波形(被采集信号产生)是在另一块板子上做的。

三种采集模式下的波形分别如下。

1. 显示触发前采集的64次数据

2. 显示触发前采集的32次数据和触发后采集的32次数据

3. 显示触发后采集的64次数据,触发沿没有显示出来

经过今晚的努力,把几个字模存储到了cyclone的M4K产生的ROM中,然后通过VGA坐标产生的控制逻辑进行地址译码。这部分设计没有仔细深入,可能浪费的M4K比较多(利用率比较低),但这是为了FPGA逻辑地址控制部分设计相对容易设计些。

稍微对下面这个波形的采集做了测试,这个波形(被采集信号产生)是在另一块板子上做的。

三种采集模式下的波形分别如下。

1. 显示触发前采集的64次数据

2. 显示触发前采集的32次数据和触发后采集的32次数据

3. 显示触发后采集的64次数据,触发沿没有显示出来

FPGA 相关文章:

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)