决定示波器性能高度的模拟技术

时间:05-23

来源:互联网

点击:

采样率和模数转换器

在示波器三大性能指标中,模拟前端决定了带宽,那么模数转换器(ADC)则是影响采样率最重要的一环,ADC是数字示波器的核心器件,其中最关键的指标是采样率和有效的ADC位数。ADC的采样率直接决定了示波器的数字带宽,也就是多高频率的信号能够有效地采集并显示。

焦保春认为,A/D转换器的采样率不可能无限制提升,R&S拥有目前示波器市场中领先的单核10Gs/s采样率A/D转换器。为达到更高采样率,很多公司采用了交织采样技术,即用多颗低速A/D并行组合成高速多核的A/D。这种技术带来的问题是信号的相位误差。为修正此误差,大多数示波器厂商使用的DSP修正技术。但DSP修正处理需要时间,这种修正使示波器的波形捕获率降低。

示波器的采样还包括采样率的准确性,就是有效转换位数(ENOB),常见示波器的A/D转换器都是8位的。但在实际使用时,真正能够发挥作用的转换位数并不能达到8位。一些示波器在高带宽是甚至会劣化到4位左右。这意味者用户不可能使用这些示波器准确测量出信号的幅度信息。焦保春介绍R&S A/D转换器的有效转换位数可以高达7位以上。

邢飞坦承,模数转换器主要决定了示波器的实时采样率指标(例如RIGOL的DS6000,实现了最高5GSa/s的实时采样率指标),并且在一定程度上,模数转换器的采样保持电路部分的满功率带宽(Full Power Bandwidth)也影响了产品最终能够达到的最高带宽。

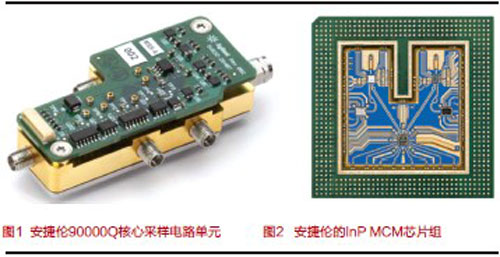

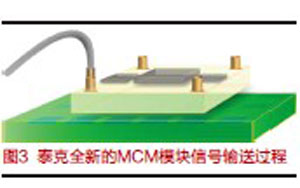

超高采样率需要多个ADC集成实现,安捷伦的90000Q示波器,160GS/s的采样率是8个20GS/s芯片实现的,而每个20GS/s又是包含80个250MS/s的单芯片,这对时钟信号的同步要求非常严格,特别是时钟分配到每个ADC后,产生的相位差解决起来挑战性很大,杜吉伟介绍,磷化铟工艺中,用波导电路设计其采样时钟,材料的特性决定其实际电路非常稳定,这是90000Q最困难的硬件设计。

研发是最大的挑战

对于高端示波器产品,商业芯片出于成本和目标应用的考虑,往往在测试信号的带宽和A/D转换速度方面不能满足高端示波器的要求。很多情况下,只有采用专用的ASIC设计才能解决这些问题。这也是高端示波器厂商不惜重金设立自己的ASIC设计团队的原因。高性能的A/D芯片也代表了示波器厂商的尖端技术研发能力。

作为本土示波器厂商的杰出代表,RIGOL的邢飞认为,到了GHz级别的示波器,行业领先公司,无一例外都是采用专用芯片实现其顶级示波器产品的需求,甚至于已经无法找到能够满足其半导体工艺需求集成电路生产线,只能够自行开发专用的集成电路工艺(例如磷化铟InP工艺)来满足其对于高带宽,高性能的要求。

安捷伦科技数字测试业务部大中国区市场经理杜吉伟介绍,安捷伦的高端示波器在模拟前端方面借鉴了很多射频微波技术,包括三维的微电路设计、波导电路等,来保证数据在传到模数转换器之前已经经过精密的信号调理。安捷伦的高端示波器采用了磷化铟工艺、快膜三维封装和氮化铝散热等技术,对示波器最后性能的领先性体现在本底噪声和采样时钟抖动在同类产品中最低。磷化铟技术在光通信中广泛应用,安捷伦将其应用到了示波器的模拟前端中,在20GHz以上的高频示波器上有一定技术优势,使用了磷化铟的包括前端放大器、触发电路、采样保持电路、探头放大器。

目前可以预见的最主要的技术挑战还是在器件电路设计方面,更进一步的,半导体工艺条件能够达到的最高特性指标也会成为仪器产品性能指标提升的一个潜在制约因素。对于模拟前端和放大器设计,调和增益、带宽和噪声特性的问题;对于模数转换器,实现超高速采样保持,优化模数转换器的转换线性度并保持合理的功耗需求;这都是目前面临的一些主要技术难点。

特别的,邢飞指出芯片工艺和材料决定了电路设计当中晶体管的最高截止频率fT,并最终从物理条件上决定了所设计出电路可能实现的最大模拟带宽。当然,模拟前端当中所用的放大器以及模数转换器的最终特性与电路设计技巧和电路实现方式也是紧密相关的,但其物理条件会最终成为器件设计的极限限制。设计方面,RIGOL就非常注重不单单从器件数据手册上标明的规格指标上,也从器件设计过程中所选用工艺的技术特点,去进行有针对性的产品选型和最终仪器产品设计。

模块化的前端设计

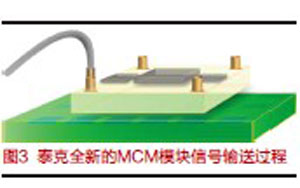

随着半导体集成工艺的进步和示波器性能的提升,单纯的模拟前端芯片已经无法满足最高性能示波器的需求,因此,各个厂商纷纷将前端模拟设计模块化,实现更高集成和更高模拟性能。安捷伦科技的90000系列产品中,采用了全新的InP技术将模拟前端部分做成6个芯片,其中的几个芯片以三维封装的形式封装成一个大的多芯片模块(MCM),包括前置放大器,采样保持和触发功能单元,成为模拟前端的核心。

传统上,高速信号采集和处理要求在示波器前端进行一系列连接和切换。信号从被测器件(DUT)输送到示波器,通过同轴电缆传送到PCB,经过球栅阵列(BGA)封装,然后到达第一个集成电路(IC),进行模拟放大或衰减。然后信号输出封装,输送到PCB上,然后发送到包含跟踪和保持(T/H)集成电路的下一个封装。只有在经过这一大串连接之后,信号才准备进行采样、模数转换和存储。遗憾的是,这一系列连接和切换及之后多次反复会在采样前劣化信号,进而损害示波器带宽和信号保真度。

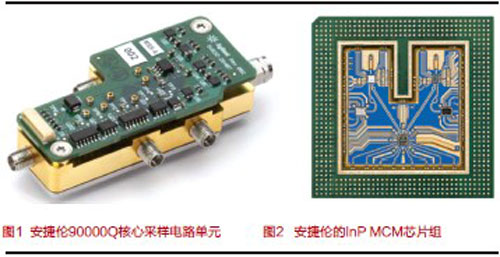

为克服这些问题,泰克在DPO/DSA70000D系列示波器采用定制设计、高度集成的前端多芯片模块(MCM)。MCM把多种前端采集和处理组件,包括同轴电缆输入连接器、前置放大器、跟踪和保持芯片及端接电阻,合并到一个封装中,因此在高速信号被采样前永远不会接触PCB。

DPO/DSA70000D系列的定制前端MCM封装把以前分散的大量组件集成在一起,包括:

● 两块前置放大器芯片;

● 一块8路跟踪和保持(T/H)芯片,带模拟滤波器;

● 50欧姆端接电阻;

● 高性能100 GHz带宽连接器;

● 到PCB的弹性接口。

由于它是一种自含式模块,MCM减少了信号流经的连接数量及可能的错误来源数量。用户不会再经过单芯片封装和PCB层而发生多个信号跳变,那样会在采样前劣化信号保真度和示波器带宽。通过使用高性能电缆,高速信号从示波器输入直接传送到MCM及内部的集成电路中。IBM的8HP技术是一种130纳米(nm) SiGe双极互补金属氧化物半导体(BiCMOS)工艺,其性能是上一代工艺的两倍。

在示波器三大性能指标中,模拟前端决定了带宽,那么模数转换器(ADC)则是影响采样率最重要的一环,ADC是数字示波器的核心器件,其中最关键的指标是采样率和有效的ADC位数。ADC的采样率直接决定了示波器的数字带宽,也就是多高频率的信号能够有效地采集并显示。

焦保春认为,A/D转换器的采样率不可能无限制提升,R&S拥有目前示波器市场中领先的单核10Gs/s采样率A/D转换器。为达到更高采样率,很多公司采用了交织采样技术,即用多颗低速A/D并行组合成高速多核的A/D。这种技术带来的问题是信号的相位误差。为修正此误差,大多数示波器厂商使用的DSP修正技术。但DSP修正处理需要时间,这种修正使示波器的波形捕获率降低。

示波器的采样还包括采样率的准确性,就是有效转换位数(ENOB),常见示波器的A/D转换器都是8位的。但在实际使用时,真正能够发挥作用的转换位数并不能达到8位。一些示波器在高带宽是甚至会劣化到4位左右。这意味者用户不可能使用这些示波器准确测量出信号的幅度信息。焦保春介绍R&S A/D转换器的有效转换位数可以高达7位以上。

邢飞坦承,模数转换器主要决定了示波器的实时采样率指标(例如RIGOL的DS6000,实现了最高5GSa/s的实时采样率指标),并且在一定程度上,模数转换器的采样保持电路部分的满功率带宽(Full Power Bandwidth)也影响了产品最终能够达到的最高带宽。

超高采样率需要多个ADC集成实现,安捷伦的90000Q示波器,160GS/s的采样率是8个20GS/s芯片实现的,而每个20GS/s又是包含80个250MS/s的单芯片,这对时钟信号的同步要求非常严格,特别是时钟分配到每个ADC后,产生的相位差解决起来挑战性很大,杜吉伟介绍,磷化铟工艺中,用波导电路设计其采样时钟,材料的特性决定其实际电路非常稳定,这是90000Q最困难的硬件设计。

研发是最大的挑战

对于高端示波器产品,商业芯片出于成本和目标应用的考虑,往往在测试信号的带宽和A/D转换速度方面不能满足高端示波器的要求。很多情况下,只有采用专用的ASIC设计才能解决这些问题。这也是高端示波器厂商不惜重金设立自己的ASIC设计团队的原因。高性能的A/D芯片也代表了示波器厂商的尖端技术研发能力。

作为本土示波器厂商的杰出代表,RIGOL的邢飞认为,到了GHz级别的示波器,行业领先公司,无一例外都是采用专用芯片实现其顶级示波器产品的需求,甚至于已经无法找到能够满足其半导体工艺需求集成电路生产线,只能够自行开发专用的集成电路工艺(例如磷化铟InP工艺)来满足其对于高带宽,高性能的要求。

安捷伦科技数字测试业务部大中国区市场经理杜吉伟介绍,安捷伦的高端示波器在模拟前端方面借鉴了很多射频微波技术,包括三维的微电路设计、波导电路等,来保证数据在传到模数转换器之前已经经过精密的信号调理。安捷伦的高端示波器采用了磷化铟工艺、快膜三维封装和氮化铝散热等技术,对示波器最后性能的领先性体现在本底噪声和采样时钟抖动在同类产品中最低。磷化铟技术在光通信中广泛应用,安捷伦将其应用到了示波器的模拟前端中,在20GHz以上的高频示波器上有一定技术优势,使用了磷化铟的包括前端放大器、触发电路、采样保持电路、探头放大器。

目前可以预见的最主要的技术挑战还是在器件电路设计方面,更进一步的,半导体工艺条件能够达到的最高特性指标也会成为仪器产品性能指标提升的一个潜在制约因素。对于模拟前端和放大器设计,调和增益、带宽和噪声特性的问题;对于模数转换器,实现超高速采样保持,优化模数转换器的转换线性度并保持合理的功耗需求;这都是目前面临的一些主要技术难点。

特别的,邢飞指出芯片工艺和材料决定了电路设计当中晶体管的最高截止频率fT,并最终从物理条件上决定了所设计出电路可能实现的最大模拟带宽。当然,模拟前端当中所用的放大器以及模数转换器的最终特性与电路设计技巧和电路实现方式也是紧密相关的,但其物理条件会最终成为器件设计的极限限制。设计方面,RIGOL就非常注重不单单从器件数据手册上标明的规格指标上,也从器件设计过程中所选用工艺的技术特点,去进行有针对性的产品选型和最终仪器产品设计。

模块化的前端设计

随着半导体集成工艺的进步和示波器性能的提升,单纯的模拟前端芯片已经无法满足最高性能示波器的需求,因此,各个厂商纷纷将前端模拟设计模块化,实现更高集成和更高模拟性能。安捷伦科技的90000系列产品中,采用了全新的InP技术将模拟前端部分做成6个芯片,其中的几个芯片以三维封装的形式封装成一个大的多芯片模块(MCM),包括前置放大器,采样保持和触发功能单元,成为模拟前端的核心。

传统上,高速信号采集和处理要求在示波器前端进行一系列连接和切换。信号从被测器件(DUT)输送到示波器,通过同轴电缆传送到PCB,经过球栅阵列(BGA)封装,然后到达第一个集成电路(IC),进行模拟放大或衰减。然后信号输出封装,输送到PCB上,然后发送到包含跟踪和保持(T/H)集成电路的下一个封装。只有在经过这一大串连接之后,信号才准备进行采样、模数转换和存储。遗憾的是,这一系列连接和切换及之后多次反复会在采样前劣化信号,进而损害示波器带宽和信号保真度。

为克服这些问题,泰克在DPO/DSA70000D系列示波器采用定制设计、高度集成的前端多芯片模块(MCM)。MCM把多种前端采集和处理组件,包括同轴电缆输入连接器、前置放大器、跟踪和保持芯片及端接电阻,合并到一个封装中,因此在高速信号被采样前永远不会接触PCB。

DPO/DSA70000D系列的定制前端MCM封装把以前分散的大量组件集成在一起,包括:

● 两块前置放大器芯片;

● 一块8路跟踪和保持(T/H)芯片,带模拟滤波器;

● 50欧姆端接电阻;

● 高性能100 GHz带宽连接器;

● 到PCB的弹性接口。

由于它是一种自含式模块,MCM减少了信号流经的连接数量及可能的错误来源数量。用户不会再经过单芯片封装和PCB层而发生多个信号跳变,那样会在采样前劣化信号保真度和示波器带宽。通过使用高性能电缆,高速信号从示波器输入直接传送到MCM及内部的集成电路中。IBM的8HP技术是一种130纳米(nm) SiGe双极互补金属氧化物半导体(BiCMOS)工艺,其性能是上一代工艺的两倍。

电子 示波器 模拟前端 安捷伦 泰克 放大器 电路 电阻 电容 射频 DSP ADC 半导体 集成电路 PCB 连接器 滤波器 CMOS 电压 相关文章:

- 技巧:电子拉力试验机的工作原理介绍(01-10)

- 表面肌电信号数字传感器的设计(01-15)

- 人体生物电阻抗的脉冲式检测方法及其应用(02-25)

- 一个新型超低功耗指纹锁控制系统(03-11)

- 数字化宽带测向系统中的相位差测量及误差分析(03-04)

- 用于胎儿心电信号测量的嵌入式数据处理系统研究(03-10)