基于CH375的智能数据采集卡设计分析

时间:10-22

来源:互联网

点击:

1 引言

数据采集是现代电子系统中不可缺少的重要组成部分,在测量、制造、自动控制等场合都需要高质量的信号采集环节,由于ADC技术和微控制器技术的相对成熟,基于PCI,ISA等接口的数据采集卡被广泛地应用在众多科研和工控领域。在测试技术日益变革的今天,测试任务更加复杂多变,需要采集和处理的信息量更加冗长,同时要求测试环节与计算机的接口更加无缝化和标准化,基于虚拟仪器技术(Virtual Instruments)和高速USB 2.0接口的数据采集有着更为广泛的应用前景和市场,是当前测试技术研究的热点之一。

以运算速度更快,位数更宽,资源更为丰富的ARM 处理器作为控制核心,配合USB 2.0数据传输和灵活的上位机软件,新一代的数据采集卡已经不再局限于单一的板卡形式,可以通过连接线独立于计算机之外,根据测试任务的需求,满足高精度、高速率、多功能的测试指标。同时由于采用了高性能的ARM处理器,控制程序容量加大,方便实现数据采集的独立化、智能化、多样化,摆脱数据采集系统对上位机运算能力的依赖,从而开发出全新的智能数据采集卡。

2 系统原理及框图

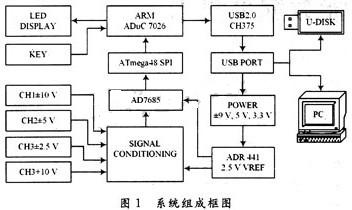

整个系统的组成框图如图1 所示。被测电压信号经过前置调理送到AD7685进行采样,由Atmega48的SPI驱动AD7685,采集到的双字节(16 b)数据由 Atmega48并口,分两次传送给ARM ADuC7026核心。当数据采集卡工作于联机状态时,由PC上位机软件设置采样频率和通道工作模式,经过处理通过USB控制芯片CH375送数据到PC端;当数据采集卡工作于离线模式时,无需PC上位机干预,数据采集卡按照预先设定的采样频率和工作模式进行采样。并将采样数据通过USB控制芯片CH375送数据到U盘端。系统采用±9 V,+5 V,+3.3 V以及模拟地数字地,并由DC/DC模块产生,经过良好的LC滤波为各个电路单元提供电力。人机接口(HMI)采用简洁的双按键和LED指示,对整个数据采集卡工作模式的选择和运行状态进行控制。

3 数据采集卡的硬件实现

3.1 ADC接口和信号调理电路

为了满足较高的采集精度和采样速率,该设计选择AD7685作为模拟/数字转换器件。AD7685是一款16位、串行输出、250 KSPS、电荷再分配、逐次逼近型 (PulSAR)ADC。ADC与处理器采用串行外围设备接口(SPI)接口进行连接,为了保证ADC的精度,采用高速光耦6N137隔离式驱动电路来隔离处理器SPI总线上的串扰。

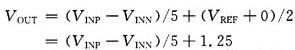

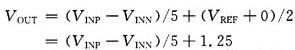

前置调理电路信号的流向参见图1系统组成框图。设计中,采用模拟开关ADG1024对输入信号进行切换,并通过可编程增益放大器(PGA)AD8251进行处理,通过增益为0.2的电平转换16位ADC驱动器 AD8275,把±5 V的信号转换成0.25~2.25 V的信号,极大地扩展了该数据采集卡的测量范围,而简化了前置调理电路的设计,其电压计算公式如下:

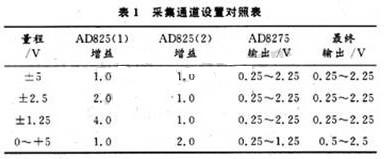

经过前置调理电路使得不同量程范围的输入信号放大或衰减到0.25~2.5 V内,最大限度地利用ADC量程,使得采集系统的4个输入通道可以有单通道、双通道、四通道3种工作模式,且每个通道皆可以设置为任意量程。前置通道的相应配置由处理器ADuC7026完成,其配置遵循表1。

3.2 EMC措施

该设计采用外置9 V开关型稳压电源或USB端口供电,由于开关电源的低成本和高功率密度,普遍被现代电子系统设计所采用,但其带来的电磁干扰(EMI)问题也不容忽视。同时,ARM7主频高达45 MHz,必须考虑其EMI问题。该设计尽量选取低噪声的放大器和ADC,遵循最短路径的布线原则,确保前置通道具有较低的噪声水平。设计中,采用数字地/模拟地分区覆铜,并一点接地的布线方式,避免电源和数字部分对模拟地电位产生浮动和干扰。同时,采集卡外壳贴装铝箔纸,以防止外界电磁辐射影响内部电路的工作。

3.3 USB接口

该设计使用USB控制芯片CH375,内置海量存储固件,既可以作为USB设备方式向PC上位机传送数据,又可以作为USB主机,将数据存入U盘中。该芯片支持USB 2.0通信协议,在并口工作模式下能同时支持主机方式和设备方式。为了保证USB高速传输数据的稳定性和完整性,采取如下措施:

(1)采用USB屏蔽线作为连接线,保证数据传输不受外界电磁干扰。

(2)保证计算机USB端口的地线与USB控制芯片CH375的地线严格等电位。

3.4 ARM系统的构建

ADuC7026是基于ARM7TDMI 内核的精密控制器,具有62 KB FLASH,8 KB RAM和4个通用定时器,内部集成UART,I2C,SPI,DAC,PWM,JTAG端口、 PLA等众多硬件资源,40个通用I/O引脚。CPU时钟高达45 MHz,采用80脚LQFP封装。在该设计中,搭建了一个包括供电电路、时钟电路、复位电路、JTAG程序下载调试接口等电路的完整ARM7应用系统。实际上由于实测ADuC7026的外部I/O取反速度只有4 MHz,因此在SPI设计中,该设计加入Atmega48单片机作为中转,保证了控制核心在处理USB通信、U盘读/写等大量信息时对采样的准确触发。

数据采集是现代电子系统中不可缺少的重要组成部分,在测量、制造、自动控制等场合都需要高质量的信号采集环节,由于ADC技术和微控制器技术的相对成熟,基于PCI,ISA等接口的数据采集卡被广泛地应用在众多科研和工控领域。在测试技术日益变革的今天,测试任务更加复杂多变,需要采集和处理的信息量更加冗长,同时要求测试环节与计算机的接口更加无缝化和标准化,基于虚拟仪器技术(Virtual Instruments)和高速USB 2.0接口的数据采集有着更为广泛的应用前景和市场,是当前测试技术研究的热点之一。

以运算速度更快,位数更宽,资源更为丰富的ARM 处理器作为控制核心,配合USB 2.0数据传输和灵活的上位机软件,新一代的数据采集卡已经不再局限于单一的板卡形式,可以通过连接线独立于计算机之外,根据测试任务的需求,满足高精度、高速率、多功能的测试指标。同时由于采用了高性能的ARM处理器,控制程序容量加大,方便实现数据采集的独立化、智能化、多样化,摆脱数据采集系统对上位机运算能力的依赖,从而开发出全新的智能数据采集卡。

2 系统原理及框图

整个系统的组成框图如图1 所示。被测电压信号经过前置调理送到AD7685进行采样,由Atmega48的SPI驱动AD7685,采集到的双字节(16 b)数据由 Atmega48并口,分两次传送给ARM ADuC7026核心。当数据采集卡工作于联机状态时,由PC上位机软件设置采样频率和通道工作模式,经过处理通过USB控制芯片CH375送数据到PC端;当数据采集卡工作于离线模式时,无需PC上位机干预,数据采集卡按照预先设定的采样频率和工作模式进行采样。并将采样数据通过USB控制芯片CH375送数据到U盘端。系统采用±9 V,+5 V,+3.3 V以及模拟地数字地,并由DC/DC模块产生,经过良好的LC滤波为各个电路单元提供电力。人机接口(HMI)采用简洁的双按键和LED指示,对整个数据采集卡工作模式的选择和运行状态进行控制。

3 数据采集卡的硬件实现

3.1 ADC接口和信号调理电路

为了满足较高的采集精度和采样速率,该设计选择AD7685作为模拟/数字转换器件。AD7685是一款16位、串行输出、250 KSPS、电荷再分配、逐次逼近型 (PulSAR)ADC。ADC与处理器采用串行外围设备接口(SPI)接口进行连接,为了保证ADC的精度,采用高速光耦6N137隔离式驱动电路来隔离处理器SPI总线上的串扰。

前置调理电路信号的流向参见图1系统组成框图。设计中,采用模拟开关ADG1024对输入信号进行切换,并通过可编程增益放大器(PGA)AD8251进行处理,通过增益为0.2的电平转换16位ADC驱动器 AD8275,把±5 V的信号转换成0.25~2.25 V的信号,极大地扩展了该数据采集卡的测量范围,而简化了前置调理电路的设计,其电压计算公式如下:

经过前置调理电路使得不同量程范围的输入信号放大或衰减到0.25~2.5 V内,最大限度地利用ADC量程,使得采集系统的4个输入通道可以有单通道、双通道、四通道3种工作模式,且每个通道皆可以设置为任意量程。前置通道的相应配置由处理器ADuC7026完成,其配置遵循表1。

3.2 EMC措施

该设计采用外置9 V开关型稳压电源或USB端口供电,由于开关电源的低成本和高功率密度,普遍被现代电子系统设计所采用,但其带来的电磁干扰(EMI)问题也不容忽视。同时,ARM7主频高达45 MHz,必须考虑其EMI问题。该设计尽量选取低噪声的放大器和ADC,遵循最短路径的布线原则,确保前置通道具有较低的噪声水平。设计中,采用数字地/模拟地分区覆铜,并一点接地的布线方式,避免电源和数字部分对模拟地电位产生浮动和干扰。同时,采集卡外壳贴装铝箔纸,以防止外界电磁辐射影响内部电路的工作。

3.3 USB接口

该设计使用USB控制芯片CH375,内置海量存储固件,既可以作为USB设备方式向PC上位机传送数据,又可以作为USB主机,将数据存入U盘中。该芯片支持USB 2.0通信协议,在并口工作模式下能同时支持主机方式和设备方式。为了保证USB高速传输数据的稳定性和完整性,采取如下措施:

(1)采用USB屏蔽线作为连接线,保证数据传输不受外界电磁干扰。

(2)保证计算机USB端口的地线与USB控制芯片CH375的地线严格等电位。

3.4 ARM系统的构建

ADuC7026是基于ARM7TDMI 内核的精密控制器,具有62 KB FLASH,8 KB RAM和4个通用定时器,内部集成UART,I2C,SPI,DAC,PWM,JTAG端口、 PLA等众多硬件资源,40个通用I/O引脚。CPU时钟高达45 MHz,采用80脚LQFP封装。在该设计中,搭建了一个包括供电电路、时钟电路、复位电路、JTAG程序下载调试接口等电路的完整ARM7应用系统。实际上由于实测ADuC7026的外部I/O取反速度只有4 MHz,因此在SPI设计中,该设计加入Atmega48单片机作为中转,保证了控制核心在处理USB通信、U盘读/写等大量信息时对采样的准确触发。

电子 ADC 虚拟仪器 USB ARM 电压 电路 LED 总线 放大器 EMC 稳压电源 开关电源 DAC PWM 单片机 相关文章:

- 技巧:电子拉力试验机的工作原理介绍(01-10)

- 表面肌电信号数字传感器的设计(01-15)

- 人体生物电阻抗的脉冲式检测方法及其应用(02-25)

- 一个新型超低功耗指纹锁控制系统(03-11)

- 数字化宽带测向系统中的相位差测量及误差分析(03-04)

- 用于胎儿心电信号测量的嵌入式数据处理系统研究(03-10)