基于扫描的DFT对芯片测试的影响

时间:09-01

来源:互联网

点击:

随着ASIC电路结构和功能的日趋复杂,与其相关的测试问题也日益突出。在芯片测试方法和测试向量生成的研究过程中,如何降低芯片的测试成本已经成为非常重要的问题。DFT(可测性设计)通过在芯片原始设计中插入各种用于提高芯片可测性的逻辑,从而使芯片变得容易测试,大大降低了芯片的测试成本。目前比较成熟的可测性设计主要有扫描设计、边界扫描设计、BIST(Built In Self Test,内建自测试)等。本文通过对一种控制芯片的测试,证明通过采用插入扫描链和自动测试向量生成(ATPG)技术,可有效地简化电路的测试,提高芯片的测试覆盖率,大大减少测试向量的数量,缩短测试时间,从而有效地降低芯片的测试成本。

基于扫描的DFT方法扫描设计的基本原理

时序电路中时序元件的输出不仅由输入信号决定,还与其原始状态有关,因此,对它的故障检测比组合电路要困难的多。扫描设计就是将时序电路转化为组合电路,然后使用已经很成熟的组合电路测试生成系统,来完成测试设计。

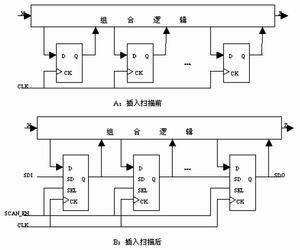

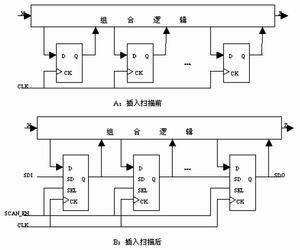

扫描设计可将电路中的时序元件替换为相应的可扫描的时序元件(也叫扫描触发器),然后把它们串起来,形成一个从输入到输出的测试串行移位寄存器(即扫描链),以实现对时序元件和组合逻辑的测试。

如图1所示,采用扫描设计技术后,通过扫描输入端,可以把需要的数据串行地移位到扫描链的相应单元中,以串行地控制各个单元;同时,也可以通过扫描输出端串行地观测它们。这样就消除了时序电路的不可控制性和不可观测性,提高了电路的可测性。需要注意的是,可测性设计的前提是不能改变原始设计的功能。

扫描设计的基本流程

扫描设计测试的实现过程是:

1) 读入电路网表文件,并实施设计规则检查(DRC),确保设计符合扫描测试的设计规则;

2) 将电路中原有的触发器或者锁存器置换为特定类型的扫描触发器或者锁存器(如多路选择D触发器),并且将这些扫描单元链接成一个或多个扫描链,这一过程称之为测试综合;

3) 测试向量自动生成(ATPG)工具根据插入的扫描电路以及形成的扫描链自动产生测试向量;

4) 故障仿真器(Fault Simulator)对这些测试向量实施评估,并确定故障覆盖率情况。

DFT对芯片的影响

DFT是为了简化芯片测试而采用的技术,对芯片的功能没有影响,但不可避免地会增加逻辑,对芯片产生一些影响。

对芯片面积的影响

DFT以增加逻辑来达到简化测试的目的,增加的逻辑势必会增加芯片面积。一般,采用DFT会增加10%"15%的芯片面积。

对芯片性能的影响

边界扫描要在每个输入输出端口处插入边界扫描寄存器(BSC),因此,在正常工作时,信号要多通过一个多路开关,这就带来了额外延时,降低了芯片原本可以达到的工作频率。

对芯片故障覆盖率的影响

芯片测试的要求就是要尽可能地将有故障的芯片检测出来,从而降低芯片的逃逸率(Escape)。DFT的目的在于方便测试,提高故障覆盖率,从而降低逃逸率。故障覆盖率并非越高越好,因为提高故障覆盖率可能会大大增加测试成本,所以应该在测试成本与取得的逃逸率之间进行折衷。

对芯片上市时间的影响

产品的上市时间对于企业至关重要,与芯片测试相关的影响上市时间的因素有:测试电路的设计时间、测试准备(ATPG,Test仿真)及工艺测试时间。

在上述因素中,测试电路设计时间的增加无疑会延迟芯片的上市时间,但DFT设计软件的不断完善能够缩短该设计时间。测试准备包括测试向量的编写和仿真,一个高效的测试向量集可以大大缩短工艺测试时间。若不采用DFT技术,就要付出相当长的时间来编写测试向量集,而且,随着VLSI的快速发展,由人工提供测试向量将越来越不现实。如果采用DFT技术,就可以缩短测试准备和工艺测试时间。因此,从总体上看,DFT是可以缩短芯片上市时间的。

两种测试方法的比较

本文针对某一种控制芯片,对采用DFT和不采用DFT的两种测试方法进行了比较,以说明DFT技术对芯片故障覆盖率及测试向量集的影响。对芯片进行“结构测试”时的测试激励来源有两种:一种是直接根据芯片的功能测试激励得到芯片的生产测试向量;另一种就是采用DFT技术,通过对设计插入扫描链,采用ATPG的方法得到测试向量。

不采用DFT技术的芯片测试测试工具与测试流程

Cadence公司的Verifault_XL工具可以统计一个测试向量集能测出多少故障,从而给出该测试向量集的故障覆盖率。采用该工具的测试流程为:

1) 用芯片功能测试激励中的部分激励对芯片的RTL级代码进行代码覆盖率的测试;

2) 在激励中调用Verifault的系统任务,实现故障的管理、注入等工作;

3) 使用Verilog_XL运行本组测试激励,得到Verifault统计结果;

4) 根据统计结果报告的故障覆盖率调整测试激励,直至达到满足要求的故障覆盖率;

5) 对达到要求的测试激励进行测试向量的提取。

需要注意的是流程中第3步,由于受机器内存的限制,Verifault能复制的设计数量有限,为了验证所有的prime故障,Verifault会重复进行多遍测试(pass),这是对Verifault仿真时间影响最大的因素。每测试完一遍,Verifault会报告一次统计结果。

基于扫描的DFT方法扫描设计的基本原理

时序电路中时序元件的输出不仅由输入信号决定,还与其原始状态有关,因此,对它的故障检测比组合电路要困难的多。扫描设计就是将时序电路转化为组合电路,然后使用已经很成熟的组合电路测试生成系统,来完成测试设计。

扫描设计可将电路中的时序元件替换为相应的可扫描的时序元件(也叫扫描触发器),然后把它们串起来,形成一个从输入到输出的测试串行移位寄存器(即扫描链),以实现对时序元件和组合逻辑的测试。

如图1所示,采用扫描设计技术后,通过扫描输入端,可以把需要的数据串行地移位到扫描链的相应单元中,以串行地控制各个单元;同时,也可以通过扫描输出端串行地观测它们。这样就消除了时序电路的不可控制性和不可观测性,提高了电路的可测性。需要注意的是,可测性设计的前提是不能改变原始设计的功能。

扫描设计的基本流程

扫描设计测试的实现过程是:

1) 读入电路网表文件,并实施设计规则检查(DRC),确保设计符合扫描测试的设计规则;

2) 将电路中原有的触发器或者锁存器置换为特定类型的扫描触发器或者锁存器(如多路选择D触发器),并且将这些扫描单元链接成一个或多个扫描链,这一过程称之为测试综合;

3) 测试向量自动生成(ATPG)工具根据插入的扫描电路以及形成的扫描链自动产生测试向量;

4) 故障仿真器(Fault Simulator)对这些测试向量实施评估,并确定故障覆盖率情况。

DFT对芯片的影响

DFT是为了简化芯片测试而采用的技术,对芯片的功能没有影响,但不可避免地会增加逻辑,对芯片产生一些影响。

对芯片面积的影响

DFT以增加逻辑来达到简化测试的目的,增加的逻辑势必会增加芯片面积。一般,采用DFT会增加10%"15%的芯片面积。

对芯片性能的影响

边界扫描要在每个输入输出端口处插入边界扫描寄存器(BSC),因此,在正常工作时,信号要多通过一个多路开关,这就带来了额外延时,降低了芯片原本可以达到的工作频率。

对芯片故障覆盖率的影响

芯片测试的要求就是要尽可能地将有故障的芯片检测出来,从而降低芯片的逃逸率(Escape)。DFT的目的在于方便测试,提高故障覆盖率,从而降低逃逸率。故障覆盖率并非越高越好,因为提高故障覆盖率可能会大大增加测试成本,所以应该在测试成本与取得的逃逸率之间进行折衷。

对芯片上市时间的影响

产品的上市时间对于企业至关重要,与芯片测试相关的影响上市时间的因素有:测试电路的设计时间、测试准备(ATPG,Test仿真)及工艺测试时间。

在上述因素中,测试电路设计时间的增加无疑会延迟芯片的上市时间,但DFT设计软件的不断完善能够缩短该设计时间。测试准备包括测试向量的编写和仿真,一个高效的测试向量集可以大大缩短工艺测试时间。若不采用DFT技术,就要付出相当长的时间来编写测试向量集,而且,随着VLSI的快速发展,由人工提供测试向量将越来越不现实。如果采用DFT技术,就可以缩短测试准备和工艺测试时间。因此,从总体上看,DFT是可以缩短芯片上市时间的。

两种测试方法的比较

本文针对某一种控制芯片,对采用DFT和不采用DFT的两种测试方法进行了比较,以说明DFT技术对芯片故障覆盖率及测试向量集的影响。对芯片进行“结构测试”时的测试激励来源有两种:一种是直接根据芯片的功能测试激励得到芯片的生产测试向量;另一种就是采用DFT技术,通过对设计插入扫描链,采用ATPG的方法得到测试向量。

不采用DFT技术的芯片测试测试工具与测试流程

Cadence公司的Verifault_XL工具可以统计一个测试向量集能测出多少故障,从而给出该测试向量集的故障覆盖率。采用该工具的测试流程为:

1) 用芯片功能测试激励中的部分激励对芯片的RTL级代码进行代码覆盖率的测试;

2) 在激励中调用Verifault的系统任务,实现故障的管理、注入等工作;

3) 使用Verilog_XL运行本组测试激励,得到Verifault统计结果;

4) 根据统计结果报告的故障覆盖率调整测试激励,直至达到满足要求的故障覆盖率;

5) 对达到要求的测试激励进行测试向量的提取。

需要注意的是流程中第3步,由于受机器内存的限制,Verifault能复制的设计数量有限,为了验证所有的prime故障,Verifault会重复进行多遍测试(pass),这是对Verifault仿真时间影响最大的因素。每测试完一遍,Verifault会报告一次统计结果。

- 集成电路的电磁兼容测试(06-06)

- 低功耗制造测试的设计-第一部分(01-29)

- 低功耗制造性测试的设计-第二部分(01-29)

- ASA测试技术在电路维修测试仪上的应用(06-28)

- 示波器前级衰减电路(06-21)

- 电调谐LC滤波器的研究与设计(11-09)