USB 3.0物理层的一致性测试(上) -- 发送端测试简介

时间:08-05

来源:互联网

点击:

如何进行通道去嵌?

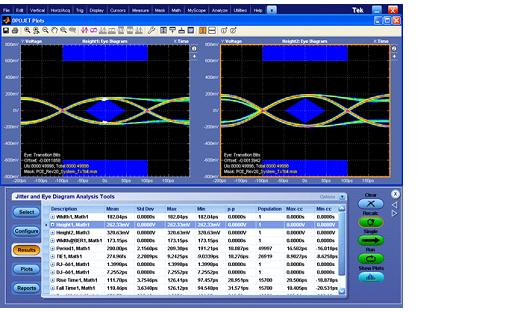

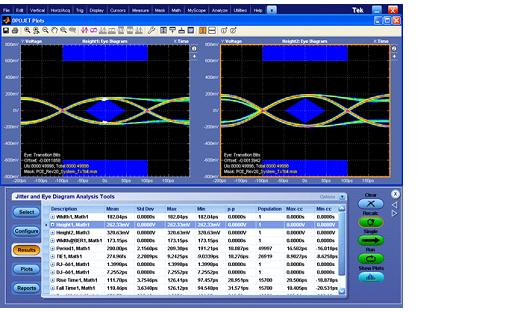

通过对夹具和通道去嵌可以真实的测出芯片引脚输出端的信号,为了达到去嵌TX通道或者夹具的目的,首先需要通过TDR刻画通道夹具特性,提取S参数,通过泰克的SDLA软件的夹具去嵌功能来生成去嵌滤波文件。如下图显示了去嵌之前与之后抓取的信号眼图,可以看出经过去嵌之后,消除了夹具和TX通道传输路径带来的影响,提高了测试眼图信号的裕量:

去嵌之前 去嵌之后

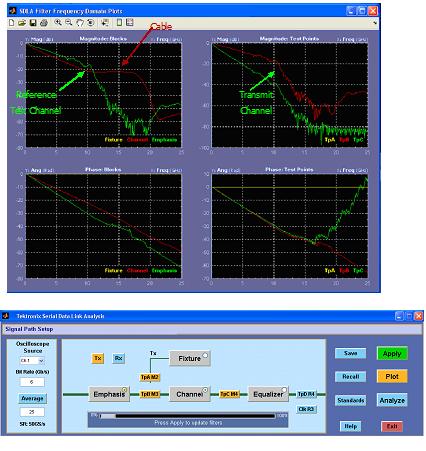

如何进行传输通道建模

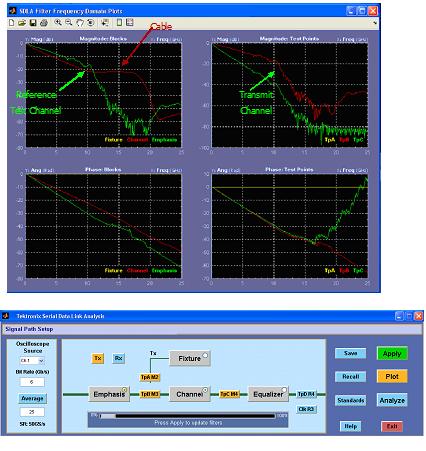

通道建模包括参考线缆和参考通道的建模。一致性测试的信号传输通道(Compliance channel)一般分为两类参考通道: 长通道和短通道。长通道类似于后背板端口,其性能主要受通道损耗影响;短通道类似与前面板端口,其性能主要受反射影响。而参考线缆则是长度为3米连接线缆。在测试的时候,因为用户大部分情况下是无法取得参考线缆和参考通道实体,为了模拟参考通道和参考线缆对信号的影响,测试客户需要使用符合USB3.0规范指定的等效模型,然后将模型参数以均衡滤波的方式作用在信号本身以达到模拟实物的效果。一致性通道的模型参数可以从USB-IF获得。为了简化测试用户操作,测试软件根据规范要求提供了丰富的滤波器模型组合来满足终端用户多样的测试需求。用户只要简单的在软件里面调用对应类型的滤波器组合就可以进行自动测试了。

TekExpress(USB-TX)使用参考通道参考线缆硬件实物,可以对不同的测试点进行选择

使用TekExpress(USB-TX)参考通道,参考线缆软件模型,选择不同的滤波器类型

对于那些想知道被测器件究竟在何种程度的连接情况下仍旧可以正常工作的客户来说,通过通道建模可以不仅仅囿于一致性测试所提供的线缆通道模型,我们可以通过SDLA软件来完成一致性测试需要模型滤波器,也可以通过该软件定制用户自己的连接配置,找到用户设计的器件在最大为何种长度的通道或者线缆下仍然可以符合规范的要求正常工作。

使用SDLA 参考测试通道和线缆组合成传输通道仿真模型来进行一致性测试

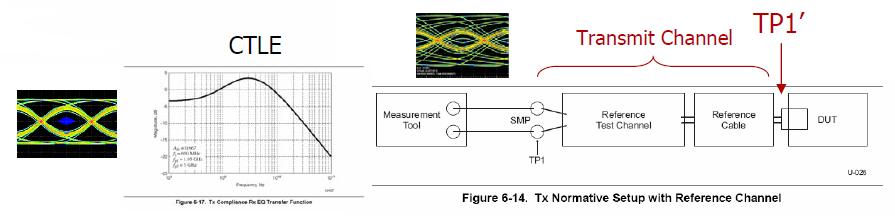

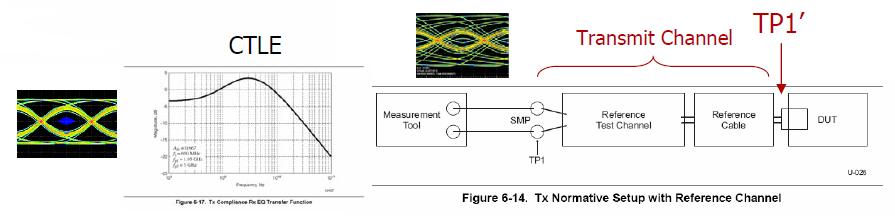

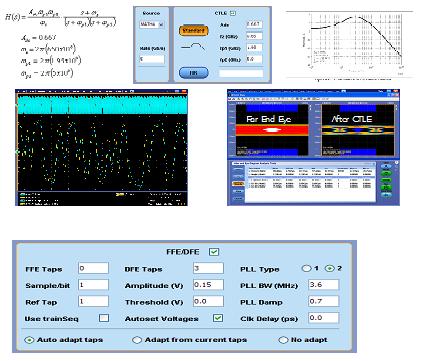

如何在USB3.0测试时使用CTLE及其它均衡?

正如前文所述,测试DUT的5Gbps的信号发出后经过参考线缆和参考通道,在TP1处探测到的波形可能因为长距离传输引起的损耗,导致接收到的信号眼图会完全闭合,USB3.0规范允许在接收端使用均衡技术后来获得张开的眼图以对系统进行时间和幅值相关的测试,使用的均衡技术为连续时间线性均衡,简称CTLE(Continuous time linear equaliztion)均衡器。

(摘自USB3.0 Electrical Compliance Methodology White paper Rev0.5)

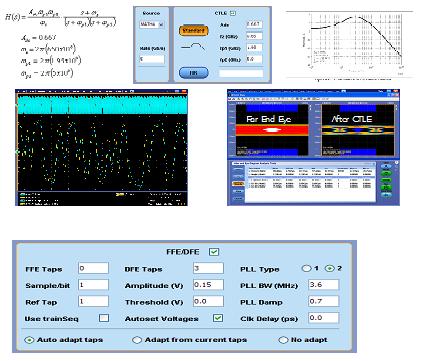

CTLE传输函数简单易于实现,容易标准化而进行一致性测试。CTLE在频域上由一些极点和零点构成,并非常容易设定所需的带宽;如果进行一致性以外的调试验证,用户会有使用自定义均衡器的需求,比如使用FFE或者DFE等等,泰克的SDLA软件都可以满足用户自定义多种类型均衡器的要求。

SDLA 软件支持用户自定义均衡:FFE,DFE及CTLE

USB3.0 发送端方案:

硬件设备部分:泰克提供了一套完整的测试夹具,可以满足发送端/接收端已及线缆的测试的多种要求。这是目前市面上唯一一种提供了A-PLUG接口的夹具,使客户可以在连接器端对器件进行测试验证,不需要引入USB3.0线缆的损耗。可以更加真实的反映测试器件的性能。测试USB3.0高达5Gbps的速率,需要带宽至少是12.5G以上的示波器,采样率为50G以保证分辨率在20ps之内。用户可以选择提供了良好的信号保真度和完整性的P7313SMA 的差分探头,也可以直接使用成本较低的SMA线缆进行信号探测。

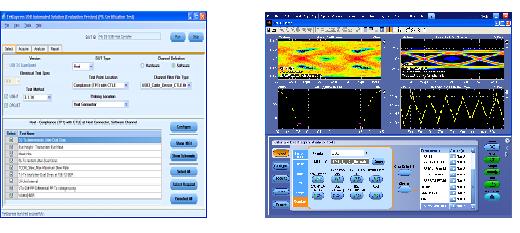

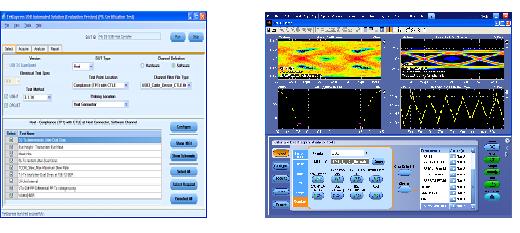

软件部分: 我们同时提供了手动测试(DPOJET带USB3选项)和自动测试(TekExpress带USB-TX选项)两种方案,并且提供了分析工具SDLA和DPOJET使客户不仅仅完成一致性测试的要求,还可以完成调试验证多种需求。

带USB-TX选项的自动测试方案 DPOJET带USB3选项的手工测试方案

TekExpress

通过对夹具和通道去嵌可以真实的测出芯片引脚输出端的信号,为了达到去嵌TX通道或者夹具的目的,首先需要通过TDR刻画通道夹具特性,提取S参数,通过泰克的SDLA软件的夹具去嵌功能来生成去嵌滤波文件。如下图显示了去嵌之前与之后抓取的信号眼图,可以看出经过去嵌之后,消除了夹具和TX通道传输路径带来的影响,提高了测试眼图信号的裕量:

去嵌之前 去嵌之后

如何进行传输通道建模

通道建模包括参考线缆和参考通道的建模。一致性测试的信号传输通道(Compliance channel)一般分为两类参考通道: 长通道和短通道。长通道类似于后背板端口,其性能主要受通道损耗影响;短通道类似与前面板端口,其性能主要受反射影响。而参考线缆则是长度为3米连接线缆。在测试的时候,因为用户大部分情况下是无法取得参考线缆和参考通道实体,为了模拟参考通道和参考线缆对信号的影响,测试客户需要使用符合USB3.0规范指定的等效模型,然后将模型参数以均衡滤波的方式作用在信号本身以达到模拟实物的效果。一致性通道的模型参数可以从USB-IF获得。为了简化测试用户操作,测试软件根据规范要求提供了丰富的滤波器模型组合来满足终端用户多样的测试需求。用户只要简单的在软件里面调用对应类型的滤波器组合就可以进行自动测试了。

TekExpress(USB-TX)使用参考通道参考线缆硬件实物,可以对不同的测试点进行选择

使用TekExpress(USB-TX)参考通道,参考线缆软件模型,选择不同的滤波器类型

对于那些想知道被测器件究竟在何种程度的连接情况下仍旧可以正常工作的客户来说,通过通道建模可以不仅仅囿于一致性测试所提供的线缆通道模型,我们可以通过SDLA软件来完成一致性测试需要模型滤波器,也可以通过该软件定制用户自己的连接配置,找到用户设计的器件在最大为何种长度的通道或者线缆下仍然可以符合规范的要求正常工作。

使用SDLA 参考测试通道和线缆组合成传输通道仿真模型来进行一致性测试

如何在USB3.0测试时使用CTLE及其它均衡?

正如前文所述,测试DUT的5Gbps的信号发出后经过参考线缆和参考通道,在TP1处探测到的波形可能因为长距离传输引起的损耗,导致接收到的信号眼图会完全闭合,USB3.0规范允许在接收端使用均衡技术后来获得张开的眼图以对系统进行时间和幅值相关的测试,使用的均衡技术为连续时间线性均衡,简称CTLE(Continuous time linear equaliztion)均衡器。

(摘自USB3.0 Electrical Compliance Methodology White paper Rev0.5)

CTLE传输函数简单易于实现,容易标准化而进行一致性测试。CTLE在频域上由一些极点和零点构成,并非常容易设定所需的带宽;如果进行一致性以外的调试验证,用户会有使用自定义均衡器的需求,比如使用FFE或者DFE等等,泰克的SDLA软件都可以满足用户自定义多种类型均衡器的要求。

SDLA 软件支持用户自定义均衡:FFE,DFE及CTLE

USB3.0 发送端方案:

硬件设备部分:泰克提供了一套完整的测试夹具,可以满足发送端/接收端已及线缆的测试的多种要求。这是目前市面上唯一一种提供了A-PLUG接口的夹具,使客户可以在连接器端对器件进行测试验证,不需要引入USB3.0线缆的损耗。可以更加真实的反映测试器件的性能。测试USB3.0高达5Gbps的速率,需要带宽至少是12.5G以上的示波器,采样率为50G以保证分辨率在20ps之内。用户可以选择提供了良好的信号保真度和完整性的P7313SMA 的差分探头,也可以直接使用成本较低的SMA线缆进行信号探测。

软件部分: 我们同时提供了手动测试(DPOJET带USB3选项)和自动测试(TekExpress带USB-TX选项)两种方案,并且提供了分析工具SDLA和DPOJET使客户不仅仅完成一致性测试的要求,还可以完成调试验证多种需求。

带USB-TX选项的自动测试方案 DPOJET带USB3选项的手工测试方案

TekExpress

USB NXP 半导体 连接器 仿真 滤波器 泰克 示波器 相关文章:

- 采用CompactDAQ平台提高USB数据采集应用的性能(01-17)

- 基于FPGA的USB2.0虚拟逻辑分析仪的设计与实现(01-18)

- 高速串行数据链路的自动化一致性测试(04-15)

- 基于LABVIEW的USB接口多路高速数据采集系统的设计(11-24)

- 基于AVR USB接口的温度测量系统下位机设计(03-01)

- 理解下一代数据采集技术(05-12)