基于LABVIEW的USB接口多路高速数据采集系统的设计

引言

在日常的测试测量中,经常使用数据采集卡采集数据。但是很多数据采集卡往往通过PCI总线完成数据的传输,它有诸多弊端,例如操作不便,受限于计算机插槽数量和中断资源,现场信号对计算机安全有威胁,计算机内部的强电磁干扰对被测信号也会造成很大的影响,最耗时最复杂的数据分析却由用户通过第三方软件(如VC,VB等) 在PC机上编写上位机软件来完成,因此用户不得不在这方面花费大量精力。这些问题都遏制了基于PCI总线的数据采集系统的进一步开发和应用,因此迫切需要设计一种更为简便通用的高速数据采集通信系统来完成数据采集以及与计算机的数据交互。

近年来通用串行总线(USB)以即插即用等技术优势得到了广泛的应用,INTEL等公司最近公布了USB 3.0主控制器规范,该标准的数据传输速率有望达5Gbps,且支持双向同时传输,完全可以满足实时数据采集的要求。LABVIEW是美国NI公司基于图形化编程语言的虚拟仪器开发环境,内置信号采集、测量分析与数据显示功能,集开发、调试、运行于一体,其交互式的Express VI 易与各种范围的I/O信号连接,可以非常容易地与各种主流的现场总线通信以及与大多数通用数据库链接,大大简化了开发进程。如果根据DSP本身的特点,把DSP集成到采集卡上,并把数据采集和部分数据处理工作留给DSP来完成,然后计算机再利用LABVIEW强大的数据处理显示功能,这无疑将大大提高测量速度和精度。

系统总体设计方案

本文提出了一种基于LABVIEW的USB接口高速数据采集系统的设计,充分利用DSP丰富的片上外设以及高性能的数字信号处理能力,将采集的数据经DSP处理后通过高速USB接口传输到PC机上,通过LABVIEW软件按照用户的特定要求来处理并显示。

TMS320F2812型DSP芯片是TI公司推出的具有高速处理能力的高精度32位定点数字信号控制器,指令速度高达150MIPS,片内集成了模数转换器(A/D转换器)、脉宽调制电路、捕获单元、光电编码器、串行外设接口等模块,为进一步拓展DSP的应用领域提供了丰富的资源。本设计采用TMS320F2812芯片(DSP)作为数据采集与控制单元,以CYPRESS公司的高速USB接口芯片CY7C68001为基础,利用DSP片上A/D转换器采集数据,经处理后把数据通过USB总线传输至PC机,PC机接收到数据后按照用户的要求通过LABVIEW处理并显示数据。该系统主要有三部分组成:4通道被测信号调理部分、数据采集控制处理部分和上位机控制面板部分,系统总体框图如图1所示。

系统硬件设计

信号调理模块

由于被测输入信号范围为-15V~+15V,而DSP片上高速A/D转换器要求输入信号必须为0~3V,所以需要对被测信号进行调理。

信号调理模块主要由高速运算放大器AD8028组成。很多运放都有这样一个特点:当输入信号接近门槛电压时,输出从一个差分对到另一个差分对变换时会产生失真,再加上信号调理模块对输入信号衰减的比例很大,如果设计不当误差会更大,因此运放的选择非常关键。AD8028是Analog Devices公司的轨到轨输入输出的高速运算放大器,工作电压2.7V-12V,共模抑制比110dB,带宽190MHz,压摆率100V/μS,它有一个突出的优点:即允许用户通过片上特定的引脚选择门槛电压,这无疑大大减小了失真,因此AD8028是一个理想的选择,其单通道信号调理模块电路图如图2所示。

数据采集模块

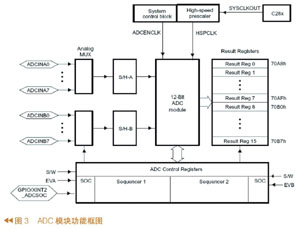

DSP片上ADC模块是可配置为2个独立的8通道模块、也可以级联构成一个16通道的带流水线的12位ADC,最高采样速率12.5MHz,流水线转换时间是80ns,单次转换时间是200ns。该模块主要由前向模拟多路复用开关、采样/保持电路、变换内核、结果寄存器、排序器、电压参考等部分组成,ADC模块的功能框图如图3所示。

USB从接口CY7C68001模块

CY7C68001集成有USB2.0收发器(物理层)、USB2.0串行接口引擎SIE(链路层)、4kB的FIFO和电压调节器、锁相环,支持高速(480Mb/s)或全速(12Mb/s)传输,3.3V操作电压,具有同步与异步的FIFO接口,支持USB2.0协议要求的全部4种传输方式(控制传输、中断传输、批量传输和同步传输),可以满足用户对各种数据传输方式的需求。片上的串行接口处理器(SIE)能完成大部分的USB协议操作,使用户可以摆脱复杂的协议细节,简化用户配置代码,加快程序开发过程。但是由于不带MCU内核,所以USB应用层协议应该由DSP编程实现,USB固件的加载必须靠DSP控制来完成。

本设计将CY7C68001映射为DSP的外设,占用DSP的外扩区域XINTF0空间,地址分配如下:FIFO2,FIFO4,FIFO6,FIFO8和命令口的地址分别为000,001,010,011,100,采用并行异步读写方式完成二者之间数据和命令的交换。当CY7C68001的地址线FIFOADR[2:0]为100时,选中CY7C68001的命令口,通过CY7C68001的命令口,可以访问其内部37个寄存器、Endpoint0缓冲器(64个字节FIFO)和描述表(500个字节FIFO)等。CY7C68001中断信号INT#和4个状态信号READY、FLAGA、FLAGB、FLAGC分别与DSP的外部中断1 (XINT1), GPIOA0,GPIOA1,GPIOA2,GPIOA3相连。在实际应用中,由于通信速度达480Mb/s,所以要对电源进行退耦处理, 另外CY7C68001最好使用24MHz有源晶振以增强系统的抗干扰能力,硬件电路图如图4所示。

- 采用CompactDAQ平台提高USB数据采集应用的性能(01-17)

- 基于FPGA的USB2.0虚拟逻辑分析仪的设计与实现(01-18)

- 高速串行数据链路的自动化一致性测试(04-15)

- 基于AVR USB接口的温度测量系统下位机设计(03-01)

- 理解下一代数据采集技术(05-12)

- 基于USB2.0的红外数据传输系统的设计与实现(07-16)