基于FPGA的PLL频率合成器设计

时间:08-12

来源:互联网

点击:

摘要:应用FPGA,采用PLL频率合成技术,结合教学实验平台的需要,设计出了一个整数/半整数频率合成器,输出范围为1 kHz~999.5 kHz,步进频率可达到0.5 kHz。与以前的教学实验装置相比,系统在性能指标、直观性等方面都有所提高,不仅可以用于教学实验,还可以用作频率源、频率计。

频率合成技术是现代通信的重要组成部分,它是将一个高稳定度和高准确度的基准频率经过四则运算,产生同样稳定度和准确度的任意频率。频率合成器是电子系统的心脏,是影响电子系统性能的关键因素之一。本文结合FPGA技术、锁相环技术、频率合成技术,设计出了一个整数/半整数频率合成器,能够方便地应用于锁相环教学中,有一定的实用价值。

1 PLL频率合成器的基本原理

频率合成器主要有直接式、锁相式、直接数字式和混合式4种。目前,锁相式和数字式容易实现系列化、小型化、模块化和工程化,性能也越来越好,已逐步成为最为典型和广泛的应用频率合成器[1]。本文主要采用集成锁相环PLLphase-Lockde Loop芯片CD4046,运用FPGA来实现PLL频率合成器。

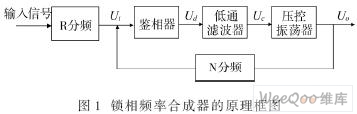

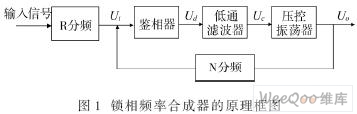

锁相频率合成器是由PLL构成的。一个典型的锁相频率合成器的原理框图如图1所示。

它的工作过程可以简单描述为:鉴相器输出电流的平均直流值乘以环路滤波器的阻抗,形成VCO的输入控制电压。VCO是一种电压—频率变换装置,具有一个比例常数。环路滤波器的控制电压调整了VCO的输出相位,除以N后,等于比较频率的相位。因为相位是频率的积分,所以这个过程同样适用于频率,输出频率可表示为:

公式1只有在PLL处于锁定状态下才成立,而在PLL重新调整到锁定状态的中间过程不成立。在实际应用中,R值是固定的,N值是可变的[2],XTAL为输入信号的频率。

2 系统设计

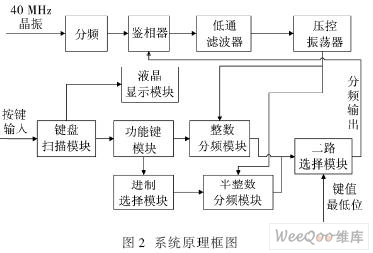

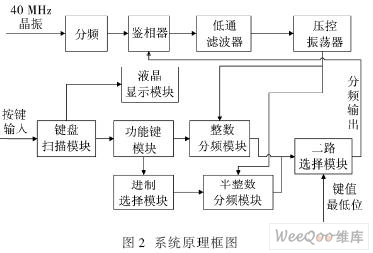

整个系统的功能主要由FPGA芯片EPF10K10 LC84-4控制相关硬件实现。本系统的原理框图如图2所示。

从图2可以看出,一方面,40 MHz有源晶振通过FPGA的控制进行分频,得到1 kHz的频率信号,作为CD4046的输入基准分频,CD4046的VCO的输出信号直接输入整数分频模块和半整数分频模块;另一方面,键盘扫描输出键值,键值送往功能模块。功能模块指示“确定”,那么键值作为分频系数,送到整数分频和半整数分频模块,分别对VCO输入的信号进行分频;功能模块指示“清除”,那么分频系数清零。键值的最后一位直接控制二路选择模块:键值的最后一位是“0”,控制二路选择模块输出整数模块结果;键值的最后一位是“5”,控制二路选择模块输出半整数模块结果。分频输出的结果与锁相环的基准频率在鉴相器中进行比较,产生一个对应于这两个信号相位差的Ud电压信号,再经过环路滤波器滤除Ud中的高频分量与噪声,输出Uc,Uc再输入VCO,使得压控振荡器的振荡频率不断向输入信号的频率靠拢,最后使得环路达到锁定,VCO输出稳定频率。

工作过程中,FPGA控制可预置的N/N+0.5的变化,当N/N+0.5变化时,输出信号频率响应跟着输入信号变化。同时FPGA也实现了键盘扫描与液晶显示的功能。

2.1 系统硬件设计

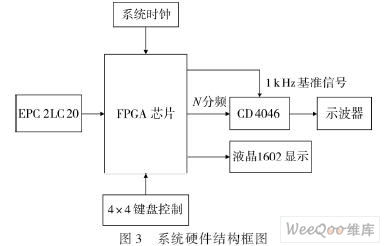

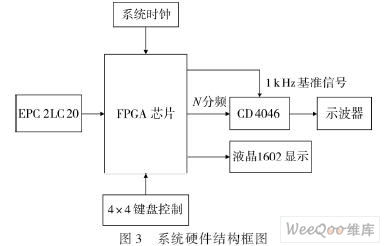

硬件上,如图3所示。该系统部分主要由7大部分组成:外部系统时钟、4×4键盘控制电路、FPGA处理芯片、EPC2LC20型EPROM芯片、PLL芯片CD4046及其外围电路、液晶1602显示模块、示波器。本设计使用FPGA专用配置芯片EPC2,通过下载电缆ByteBlaster MV,把程序多次下载到FPGA芯片中。系统使用FPGA芯片作为控制中心,按键扫描输入控制信息,液晶屏进行显示,能够方便直观地演示PLL芯片CD4046在频率合成技术中的应用,且达到了预期的指标要求。本设计中的主要硬件的具体型号是:液晶TC1602A-01T,FPGA芯片EPF10K10LC84-4,40.000 MHz有源晶振HO-12B。

2.2 系统软件设计

通过编写VHDL程序实现整数/半整数分频,并应用Quartus II和ModelSim,笔者完成了VHDL程序的设计及仿真。

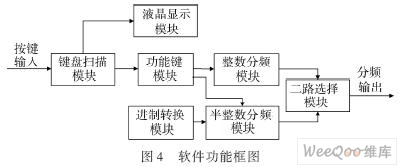

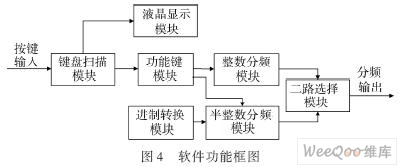

系统软件功能框图如图4所示。

系统的具体工作过程如下:

键盘扫描模块负责扫描按键,输出键值,键值输入到1602液晶模块中进行显示。同时,通过功能键模块去控制键值输入到FPGA中的分频模块中,功能模块为“确定”时,键值输入到FPGA分频模块中,分频系数N就等于输入的键值。功能模块为“清除”时,FPGA分频模块中,分频系数N就会被清零。

3 系统测试及结果

测试仪器:INSTEK GOS-620(20 MHz模拟示波器)

测试温度:室温

3.1 检测系统是否入锁

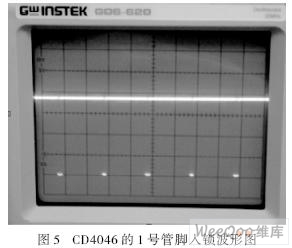

键盘输入从1~999.5时,所测CD4046的1号管脚波形如图5所示,指示PLL处于入锁状态。

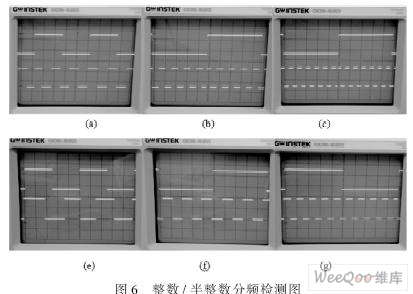

3.2 检测较低频的整数/半整数分频

当N=3、9、13、1.5、5.5、9.5,输入为1 kHz的频率时,CD4046的输出波形分别如图6(a)、(b)、(c)、(e)、(f)、(g)所示。从图中可以很明显地读到,输出分别为3 kHz、9 kHz、13 kHz、1.5 kHz、5.5 kHz和9.5 kHz。这与理论上预见的结果是一致的。

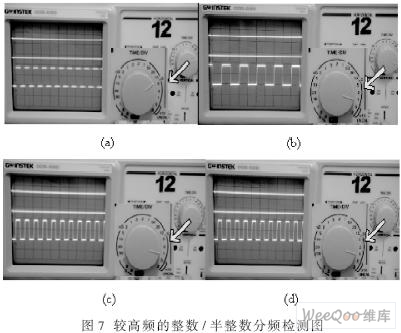

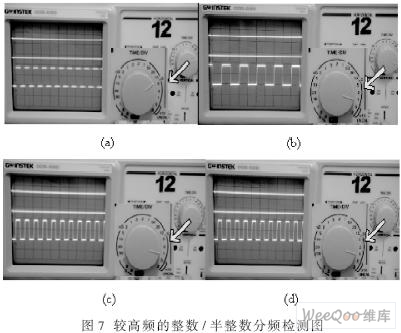

3.3 检测较高频的整数/半整数分频

当N为更高的数值时,通过比较CD4046的输入输出波形,很难直接看出来。这时输入仍采用1kHz的频率值,这时直接看输出的频率值。N=100、500、999、999.5时的波形分别如图7(a)、(b)、(c)、(d)所示。

由图7(a)得:所测频率为1/(10×10-6)Hz=100 kHz

由图7(b)得:所测频率为2/(10×10-6)Hz=500 kHz

由图7(c)得:所测频率约为1/(10×10-6)Hz=1 MHz

由图7(d)得:所测频率约为1/(10×10-6)Hz=1 MHz

可见,这时实测值与理论上预见的结果也是一致的。

3.4 误差分析

较低频时的波形之所以占空比不是标准的50%,是由于CD4046输出频率经过FPGA分频模块之后产生的反馈信号只是一个脉冲信号,这个脉冲信号要与出入CD4046的1kHz的标准信号进行相位比较,而标准信号的占空比是50%,这就造成了相位比较之后产生的信号波形占空比不是50%,而本系统测试时所采用的是模拟示波器,对较低频占空比非50%的显示不是很好,这很有可能是由于波形不是非常标准的主要原因。

在测试完成之后,又用数字示波器来专门检测CD4046的输出频率,结果与理论计算几乎吻合。

本系统结合FPGA技术、锁相环技术、频率合成技术,设计出了一个整数/半整数频率合成器,输出范围为1 kHz~999.5 kHz,步进频率可达到0.5 kHz;与以前的实验装置相比,系统在性能指标、直观性等方面都有所提高,它不仅可以用于教学实验,还可以用作频率源、频率计。

频率合成技术是现代通信的重要组成部分,它是将一个高稳定度和高准确度的基准频率经过四则运算,产生同样稳定度和准确度的任意频率。频率合成器是电子系统的心脏,是影响电子系统性能的关键因素之一。本文结合FPGA技术、锁相环技术、频率合成技术,设计出了一个整数/半整数频率合成器,能够方便地应用于锁相环教学中,有一定的实用价值。

1 PLL频率合成器的基本原理

频率合成器主要有直接式、锁相式、直接数字式和混合式4种。目前,锁相式和数字式容易实现系列化、小型化、模块化和工程化,性能也越来越好,已逐步成为最为典型和广泛的应用频率合成器[1]。本文主要采用集成锁相环PLLphase-Lockde Loop芯片CD4046,运用FPGA来实现PLL频率合成器。

锁相频率合成器是由PLL构成的。一个典型的锁相频率合成器的原理框图如图1所示。

它的工作过程可以简单描述为:鉴相器输出电流的平均直流值乘以环路滤波器的阻抗,形成VCO的输入控制电压。VCO是一种电压—频率变换装置,具有一个比例常数。环路滤波器的控制电压调整了VCO的输出相位,除以N后,等于比较频率的相位。因为相位是频率的积分,所以这个过程同样适用于频率,输出频率可表示为:

公式1只有在PLL处于锁定状态下才成立,而在PLL重新调整到锁定状态的中间过程不成立。在实际应用中,R值是固定的,N值是可变的[2],XTAL为输入信号的频率。

2 系统设计

整个系统的功能主要由FPGA芯片EPF10K10 LC84-4控制相关硬件实现。本系统的原理框图如图2所示。

从图2可以看出,一方面,40 MHz有源晶振通过FPGA的控制进行分频,得到1 kHz的频率信号,作为CD4046的输入基准分频,CD4046的VCO的输出信号直接输入整数分频模块和半整数分频模块;另一方面,键盘扫描输出键值,键值送往功能模块。功能模块指示“确定”,那么键值作为分频系数,送到整数分频和半整数分频模块,分别对VCO输入的信号进行分频;功能模块指示“清除”,那么分频系数清零。键值的最后一位直接控制二路选择模块:键值的最后一位是“0”,控制二路选择模块输出整数模块结果;键值的最后一位是“5”,控制二路选择模块输出半整数模块结果。分频输出的结果与锁相环的基准频率在鉴相器中进行比较,产生一个对应于这两个信号相位差的Ud电压信号,再经过环路滤波器滤除Ud中的高频分量与噪声,输出Uc,Uc再输入VCO,使得压控振荡器的振荡频率不断向输入信号的频率靠拢,最后使得环路达到锁定,VCO输出稳定频率。

工作过程中,FPGA控制可预置的N/N+0.5的变化,当N/N+0.5变化时,输出信号频率响应跟着输入信号变化。同时FPGA也实现了键盘扫描与液晶显示的功能。

2.1 系统硬件设计

硬件上,如图3所示。该系统部分主要由7大部分组成:外部系统时钟、4×4键盘控制电路、FPGA处理芯片、EPC2LC20型EPROM芯片、PLL芯片CD4046及其外围电路、液晶1602显示模块、示波器。本设计使用FPGA专用配置芯片EPC2,通过下载电缆ByteBlaster MV,把程序多次下载到FPGA芯片中。系统使用FPGA芯片作为控制中心,按键扫描输入控制信息,液晶屏进行显示,能够方便直观地演示PLL芯片CD4046在频率合成技术中的应用,且达到了预期的指标要求。本设计中的主要硬件的具体型号是:液晶TC1602A-01T,FPGA芯片EPF10K10LC84-4,40.000 MHz有源晶振HO-12B。

2.2 系统软件设计

通过编写VHDL程序实现整数/半整数分频,并应用Quartus II和ModelSim,笔者完成了VHDL程序的设计及仿真。

系统软件功能框图如图4所示。

系统的具体工作过程如下:

键盘扫描模块负责扫描按键,输出键值,键值输入到1602液晶模块中进行显示。同时,通过功能键模块去控制键值输入到FPGA中的分频模块中,功能模块为“确定”时,键值输入到FPGA分频模块中,分频系数N就等于输入的键值。功能模块为“清除”时,FPGA分频模块中,分频系数N就会被清零。

3 系统测试及结果

测试仪器:INSTEK GOS-620(20 MHz模拟示波器)

测试温度:室温

3.1 检测系统是否入锁

键盘输入从1~999.5时,所测CD4046的1号管脚波形如图5所示,指示PLL处于入锁状态。

3.2 检测较低频的整数/半整数分频

当N=3、9、13、1.5、5.5、9.5,输入为1 kHz的频率时,CD4046的输出波形分别如图6(a)、(b)、(c)、(e)、(f)、(g)所示。从图中可以很明显地读到,输出分别为3 kHz、9 kHz、13 kHz、1.5 kHz、5.5 kHz和9.5 kHz。这与理论上预见的结果是一致的。

3.3 检测较高频的整数/半整数分频

当N为更高的数值时,通过比较CD4046的输入输出波形,很难直接看出来。这时输入仍采用1kHz的频率值,这时直接看输出的频率值。N=100、500、999、999.5时的波形分别如图7(a)、(b)、(c)、(d)所示。

由图7(a)得:所测频率为1/(10×10-6)Hz=100 kHz

由图7(b)得:所测频率为2/(10×10-6)Hz=500 kHz

由图7(c)得:所测频率约为1/(10×10-6)Hz=1 MHz

由图7(d)得:所测频率约为1/(10×10-6)Hz=1 MHz

可见,这时实测值与理论上预见的结果也是一致的。

3.4 误差分析

较低频时的波形之所以占空比不是标准的50%,是由于CD4046输出频率经过FPGA分频模块之后产生的反馈信号只是一个脉冲信号,这个脉冲信号要与出入CD4046的1kHz的标准信号进行相位比较,而标准信号的占空比是50%,这就造成了相位比较之后产生的信号波形占空比不是50%,而本系统测试时所采用的是模拟示波器,对较低频占空比非50%的显示不是很好,这很有可能是由于波形不是非常标准的主要原因。

在测试完成之后,又用数字示波器来专门检测CD4046的输出频率,结果与理论计算几乎吻合。

本系统结合FPGA技术、锁相环技术、频率合成技术,设计出了一个整数/半整数频率合成器,输出范围为1 kHz~999.5 kHz,步进频率可达到0.5 kHz;与以前的实验装置相比,系统在性能指标、直观性等方面都有所提高,它不仅可以用于教学实验,还可以用作频率源、频率计。

FPGA 电子 电流 滤波器 电压 振荡器 电路 示波器 VHDL Quartus ModelSim 仿真 相关文章:

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)