GA的CPRI帧信号,进行相应的8B/10B编码后送给SERDES Core完成并串转换。

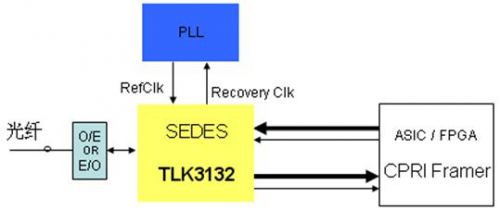

在该电路中,TLK3132恢复时钟送给PLL作为参考时钟,同时其参考时钟又来自PLL的输出时钟。为保证内部CDR可靠工作,TLK3132要求参考时钟跟输入高速串行数据的频偏控制在+/-200PPM以内,因此外围PLL在失锁情况下,必须保证本地振荡器的自由振荡频率要足够稳定,通常建议采用基于压控晶振的时钟方案。

图8 TLK3132在CPRI接口的典型应用

下面例子说明如何通过MDIO设置TLK3132相关寄存器的软件配置。假设:CH0和CH1通道串行速率分别为1228.8Mbps和2457.6Mbps、并行接口采用SDR接口并工作在NBI模式、使能内部8B/10B编解码器、差分参考输入122.888MHz时钟,内部抖动滤除锁相环关闭,则在TI的TLK3132评估板上参考软件配置如下。

START

CLAUSE 22 //选择CLAUSE 22模式

SETPHYADD(00) //选择物理地址0

WRITE(00, 8000) //软件复位芯片,即对所有寄存器进行复位

READ(11, 3590, FFFF) // 验证MDIO 功能是否正常

WRITE(1E, 9100) //把0x3FF0写入0x9100寄存器,差分参考输入作为SERDES Core的参考时钟

WRITE(1F, 3FF0)

WRITE(1E, 9000) //高频倍频器的倍频系数设为10

WRITE(1F, 1515)

WRITE(1E, 9001) //设置CH0为1/2速-1228.8Mbps、CH1为全速-2457.6Mbps

WRITE(1F, 6060)

WRITE(10, 8400) //并行接收时钟选择各自通道的恢复时钟

WRITE(11, B197) //并口为SDR且工作在NBI模式、上升沿打数据、8B/10B使能

WRITE(1E, 9002) //设置CH0通道接收为交流耦合、自适应均衡

WRITE(1F, 1005)

WRITE(1E, 9004) //设置CH1通道接收为交流耦合、自适应均衡

WRITE(1F, 1005)

WRITE(1E, 900A) //设置CH0通道串行发送端的摆幅为1000mV,去加重为9.52% (0.87dB)

WRITE(1F, 0B21)

WRITE(1E, 900C) //设置CH1通道串行发送端的摆幅为1000mV,去加重为9.52% (0.87dB)

WRITE(1F, 0B21)

WRITE(10, 8C00) //数据通道复位

PAUSE(100) //等待芯片配置生效

WRITE(1E, 901B) //检查SERDES Core内部锁相环是否锁定

READ(1F, 0011, 0011)

STOP

3.3 实验测试

由于串行口速率高达1228.8Mbps和2457.6Mbps,对PCB的layout提出较大的挑战。同时TLK3132具有非常优秀的损耗补偿能力,可以调整最佳的去加重补偿等级,以得到最佳的信号完整性性能。

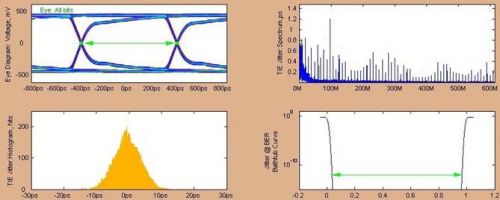

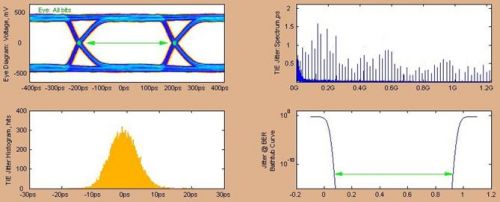

在3.2节的例子中,反复发送K28.5字节数据,实际测试到的TLK3132发送端眼图如图9和图10(分别对应的串行速率为1228.8Mbps和2457.6Mbps),抖动主要来源于随机噪声,眼宽均在0.9UI以上,具有非常优越的抖动性能(通过适当调整去加重能力补偿传输线FR4的损耗,以提高SI性能)。

图9 1228.8Mbps发送侧眼图(经5inches FR4走线,调整了最优的去加重补偿)

图10 2457.6Mbps发送侧眼图(经5inches FR4走线,调整了最优去加重补偿)

4 总结

TLK3132是一款低功耗、低抖动、低成本、高性能的多速率收发器,灵活的内部模块配置功能使其广泛地应用于高速串行通信。

为了降低无线网络的组网成本和提高覆盖范围,射频拉远技术广泛应用在3G网络建设,可把原基站内的基带单元和射频单元通过标准化接口(如CPRI等)进行分离,达到一处机房多处天线配置的网络布局,以减少运营商对固定机房的投资。作为CPRI接口实现的一个关键技术-高速串并/并串收发器,TLK3132提供非常优越的SI性能、标准的8B/10B和通道同步处理、灵活的片内时钟产生和分布等,完全能满足高可靠、多速率的CPRI接口标准要求。

|