高性能SERDES及其在CPRI接口的应用分析

义的控制信息等进行相应的处理。

目前CPRI有三种建议的链路速率,分别是614.4Mbps、1228.8Mbps、2457.6Mbp。在发送侧,把I/Q数据、控制协议信息、同步信息等复用为CPRI帧结构信息,经过物理层的8B/10B编码后,通过光纤长距离传播(几公里到几十公里);在接收侧,CPRI帧信号经过串并转换后经过8B/10解码成相应的I/Q数据和控制协议信息,交由上层数据链路处理。

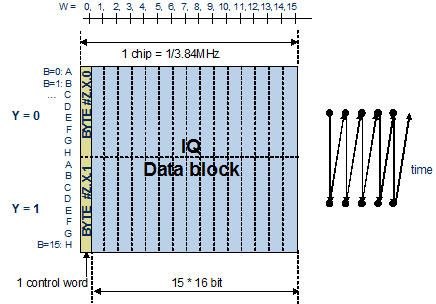

CPRI帧分成基本帧单元和超帧单元。基本帧单元的帧频是3.84MHz,包括16个字(表示为W=0…15,其中W0为控制字,后15个字为I/Q数据),根据不同的链路速率,字的长度分别为8bits、16bits(如图7所示)、32bits。超帧单元是由256个基本帧单元组成,其中,第1个基本帧单元里的控制字写入K28.5标志作为超帧的同步控制信息,其余的255个基本帧单元里的控制字包含控制和管理字(C&M)、厂商自定义控制字等,并预留一些控制字。

图7 线速率1228.8Mbps的CPRI基本帧结构

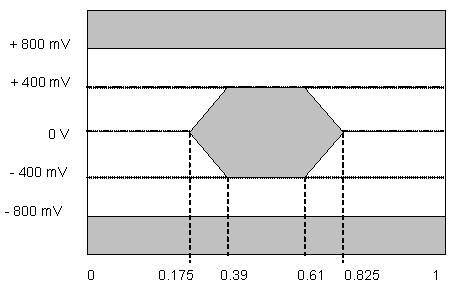

在高速数据链路通信中,抖动指标是非常关键的,CPRI接口相应推荐了高速串行信号的眼图和抖动规格。在SERDES发送侧,CPRI要求的眼图模板如图8所示。

图8 CPRI接口发送输出眼图模板(E.x.LV)

表1 E.6.LV, E.12.LV and E.24.LV发送器AC定时规格(参考资料CPRI Specification V2.0)

| 特性 | 符号 | 范围 | 单位 | 注释 | |

| Min | Max | ||||

| 输出电压 | Vo | -0.40 | 2.30 | Volts | |

| 差分输出电压 | VDIFFPP | 800 | 1600 | mV,p-p | |

| 确定性抖动 | JD |

| 0.17 | UI | |

| 总抖动 | JT |

| 0.35 | UI | |

| 单位间隔 E.6.LV | UI | 1/614.4 | 1/614.4 | ms | +/- 100 ppm |

| 单位间隔 E.12.LV | UI | 1/1228.8 | 1/1228.8 | ms | +/- 100 ppm |

| 单位间隔 E.24.LV | UI | 1/2457.6 | 1/2457.6 | ms | +/- 100 ppm 在CPRI接口的实现中,TLK3132完成高性能的串/并、并/串转换,以及CPRI帧的同步和8B/10B编解码,即CPRI接口物理层的相关功能实现。 3.2 应用例子 根据前面关于TLK3132的器件特点分析和CPRI接口介绍,TLK3132可以很好地满足CPRI接口的应用要求,图8是TLK3132在CPRI链路中的一个典型功能框图:TLK3132接收来自光电转换后的高速串行电信号,经串并转换后,提取相应控制字符和有效字符并进行8B/10B解码,送给ASIC或FPGA进行CPRI解帧处理;同时,也接收来自ASIC/FP |

- TI TRF2443宽带无线IF收发方案(07-07)

- Hittite HMC792LP4E DC-6 GHz数字衰减方案(07-26)

- Hittite HMC713LP3E 50MHz-8GHz 功率检测方案(07-26)

- 高精度宽带锁相环HMC830LP6GE(10-06)

- Multisim 10在差动放大电路分析中的应用(02-15)

- 5G--下一波人物互联的新浪潮(07-07)