分析、优化和消除带VCO的锁相环在高达13.6 GHz处的整数边界杂散

时间:10-08

来源:互联网

点击:

| fPFD (MHz) | N | ICP | fPFD × N = RFOUT (MHz) | 注释 |

| 100 | 20.01 | 2.08 | 2001 | IBS ( ± 1 MHz 时) |

| 75 | 26.68 | 1.88 | 2001 | IBS ( ± 24 MHz 时) |

其中:

ICP= 可编程电荷泵电流;

fPFD = PLL PFD频率;

N = PLL小数N分频值;

RFOUT = VCO输出频率/载波频率/目标信号

可编程电荷泵电流的变化方向与PFD频率相反——PFD频率增加则电荷泵电流下降。这是为了保持环路滤波器的动态恒定。

使用ADIsimFrequencyPlanner时,用户输入所需的输出频率范围、步进大小、PFD频率和参考频率限制条件,以及环路滤波器参数。用户还可选择可用的时钟发生器输出分频器和PLL参考输入分频器。随后,ADIsimFrequencyPlanner逐一对目标频率进行分析,并根据可用PFD频率阵列计算最优PFD频率。然后,ADIsimFrequencyPlanner将所需的分频器设置和电荷泵电流返回至用户。数据可轻松导出至查找表中,供最终应用的固件读取,然后相应编程HMC7044和PLL/VCO。ADIsimFrequencyPlanner还可生成一系列照片,向用户显示发生了什么。

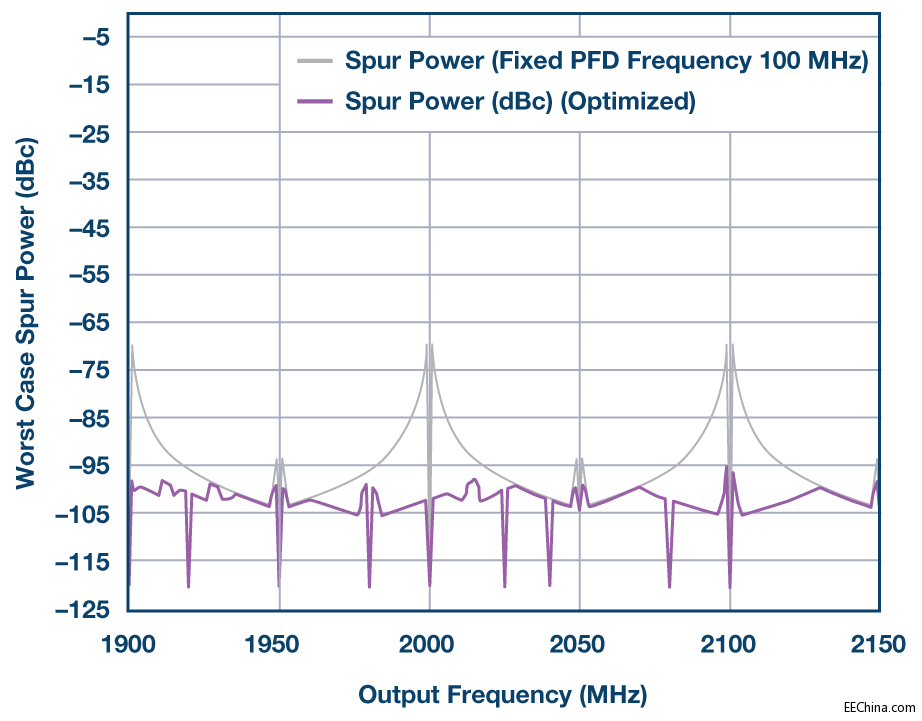

在图3中,用户使用了与图1相同的配置,不同的是这次PFD频率通过改变HMC7044输出分频器和PLL参考输入分频器而优化。未优化的仿真如图中灰色部分所示,供对比。

图3. 与图1相同的输出配置,不过这次优化了PFD频率。

由图3可见,在输出范围内(1900 MHz至2150 MHz,1 MHz步进),所有整数边界杂散现在都低于 –95 dBc。这表示性能有了大幅提升,并且目标输出有极高的百分比具有相同的高质量。

将ADIsimFrequencyPlanner应用到宽带VCO

在测量ADIsimFrequencyPlanner精度和有效性的实验中,将部分ADI高性能器件放在一起,并在实验室中进行评估。该实验需要用到下列器件:

HMC7044时钟生成和分配:

高达3.2 GHz输出。

J符合JESD204B标准。

超低噪声(抖动低于50 fs,12 kHz至20 MHz)。

–142 dBc/Hz(偏移983.04 MHz输出800 kHz)。

6个可编程输出。

集成式PLL和VCO ADF5355:

RF输入高达8 GHz。

100 MHz最大PFD频率。

–233 dBc/Hz归一化相位噪底。

超低噪声PLL HMC704:

RF输入高达8 GHz。

100 MHz最大PFD频率。

–233 dBc/Hz归一化相位噪底。

虽然ADF5355内部集成PLL,但是使用HMC704从外部锁定ADF5355 VCO。这样做有两个主要好处:

总相位噪声得益于ADF5355业界领先的VCO相位噪声性能,以及得益于HMC704业界领先的PLL相位噪声性能。

隔离VCO和PLL可减少干扰信号耦合,从而降低杂散信号的功率。

ADIsimFrequencyPlanner用来优化4800 MHz至6300 MHz范围的输出,步进为250 kHz(6000次步进)。在每个步进处,最优分频器设置(因而PFD频率也最优)和电荷泵电流编程至HMC7044、ADF5355和HMC704。一旦器件编程并产生步进,频谱分析仪便测量载波功率、一阶和二阶整数边界杂散的功率。频谱分析仪采用极为狭窄的频率范围和分辨率带宽——即便如此,在大部分通道中仅测量噪声,因为整数边界杂散功率低于仪器的噪底。

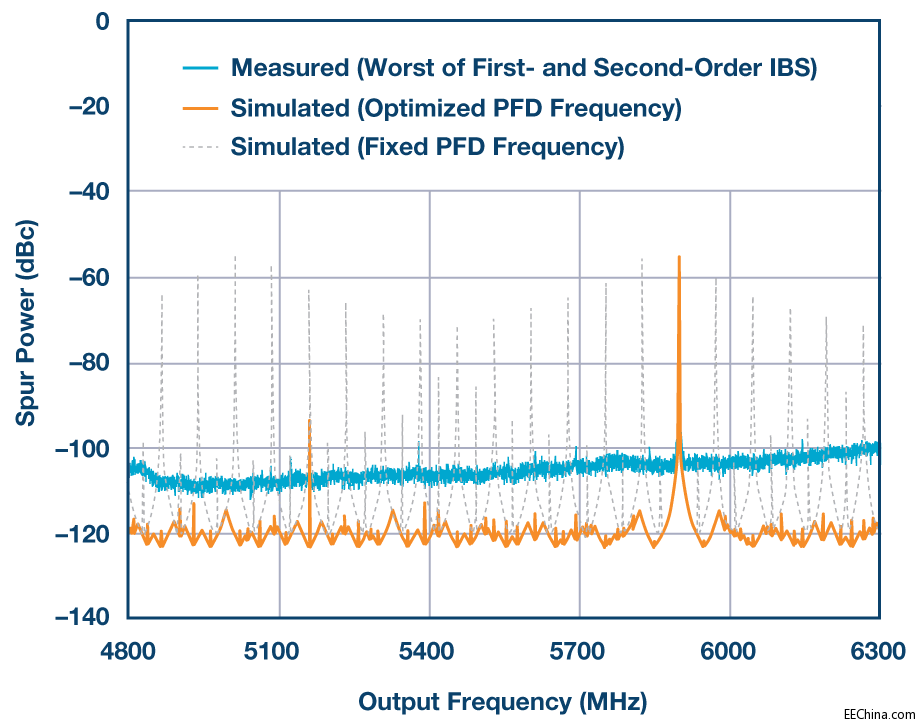

以下测量为PFD频率限制在60 MHz至100 MHz范围内的时候测得。环路带宽和相位裕量分别为17 kHz和49.6°。

图4显示了HMC7044、ADF5355和HMC704解决方案的测量和仿真结果。

仿真和测量6000个输出通道。

大部分整数边界杂散都在 –120 dBc附近仿真。这低于频谱分析仪的噪底,因而仅测量噪声。

大部分频率的杂散低于 –100 dBc!典型要求是 –70 dBc至 –80 dBc。

优化不改进IBS的唯一区域是低于2 MHz宽的部分,并且发生在2 × HMC7044主机时钟处——在该频率下,没有任何分频器组合可以改善IBS性能。下文提供替代解决方案。

图4. HMC7044、ADF5355和HMC704的测量与仿真结果。注意ADIsimFrequencyPlanner正确仿真了不可优化的较窄频率范围。在其它大部分频率处,测量受限于频谱分析仪的噪底。

只有在一个非常窄的频率范围内,优化PFD频率才无法改善IBS性能。该频率范围是系统主时钟的两倍(本例中为2949.12 MHz × 2 = 5898.24 MHz)。在此频率下,如果应用可行的话,建议将载波频率转换至附近更为干净的频率,然后将基带频率转换至数字 (NCO) 以补偿。例如,载波频率偏移2 MHz,然后将数字基带频率偏移2 MHz以补偿。此外,如果系统可行的话,可改变主机时钟频率,创造干净的输出频率。

如果采用上述较为简单的解决方案(使用HMC832或ADF4351而非HMC7044),那么就不会产生任何有问题的频率!

由图4可以看出,ADIsimFrequencyPlanner可以:

精确仿真整数边界杂散。

成功优化参考源和PLL/VCO系统,以便实现出色的整数边界杂散性能。

这样可以在某个范围内使更多通道可用,从而提升昂贵频谱的成本价值。

快速仿真宽频率范围。如进行手动处理的话,可能需要数天或数周。上文中的6000个步进在ADIsimFrequencyPlanner中处理只需花不到1分钟的时间。

ADI 振荡器 仿真 ADC DAC 电流 滤波器 频谱分析仪 电子 相关文章:

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- D类放大器原理详解及应用设计指南(三)(03-16)

- ADMC331在全数字化逆变电源中的应用(06-20)

- 雷达天线电源故障检测电路的设计(01-27)

- ADISl6300四自由度IMU在姿态测量中的应用(08-18)

- 高性能模拟器件兼顾医疗设备诊断级精度和便携化需求(04-26)