用于PLL/VCO和时钟IC供电的超低噪声线性调节器

时间:01-15

来源:互联网

点击:

宽带通信系统通常需要超低噪声调节器来为VCO和PLL供电。调节器还必须能够抑制其输入端出现的任何纹波。在一般系统中,交流输入转换为隔离式直流供电轨,例如-48 V直流。该供电轨继而转换为隔离式12 V系统轨,为通信系统中的主要元件供电。

该12 V系统轨由感应开关元件生成,该元件会在轨上引起波纹和噪声。为了获得干净的供电轨,需要超低噪声调节器来生成5 V供电轨,为宽带PLL和VCO供电。在5 V供电轨上出现的任何噪声或波纹都会使PLL或VCO性能下降。

超低噪声LDO-ADM7150/ADM7151

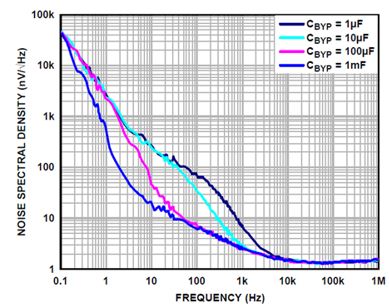

针对RF信号器件的固定输出超低噪声线性调节器ADM7150和可调输出超低噪声线性调节器ADM7151工作电压范围为4.5 V至16 V,可提供最高800 mA的输出电流,并且支持1.5至5.0 V的输出电压。该LDO可在10 kHz至1 MHz频率范围内实现1.4 nV/ Hz的输出噪声频谱密度(NSD),从而大幅降低点对点微波无线电、卫星通信、防务电子和其他宽带系统中的VCO相位噪声。此外,对于精密模拟前端测量系统,用户可调电容器可以极大减少低频噪声(100 Hz时8 nV/ Hz)。解决方案的整体尺寸仅7.62 mm × 5.21 mm。

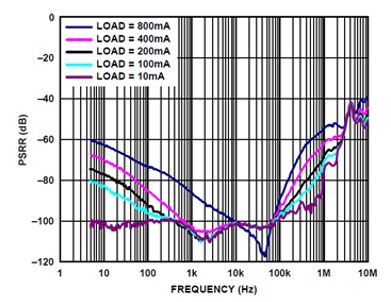

噪声频谱密度和电源抑制(PSRR)

ADM7150/ADM7151的典型输出噪声为1.0 μV rms(100 Hz至100 kHz,固定输出电压),10 kHz至1 MHz的噪声频谱密度为1.7nV/ Hz。这些调节器采用先进的专有架构,提供高电源抑制(>90 dB,从1 kHz至1 MHz)特性,利用一个10 μF陶瓷输出电容,便可实现出色的线路与负载瞬态响应性能。

各 CBYP下噪声频谱密度(NSD)与频率的关系

电源抑制比(PSRR)与频率的关系(VOUT = 5 V,VIN = 6.2 V)

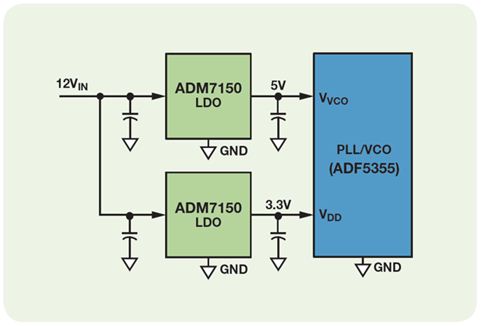

ADM7150设计示例

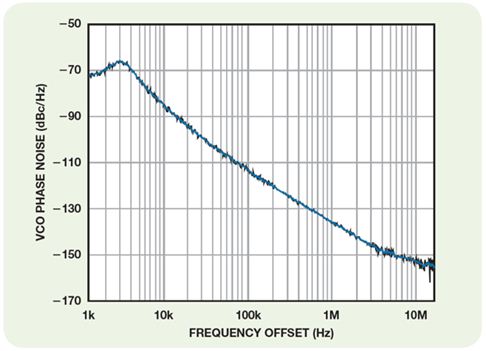

本示例显示集成VCO的微波宽带频率合成器ADF5355,由超低噪声LDO ADM7150为其供电。

PLL/VCO应用框图

ADF5355 VCO噪声,ADM7150供电

结论

宽带通信的出现对于超低功耗LDO提出了更新的要求,以满足下一代PLL/VCO和时钟器件的供电需求。 ADM7150/ADM7151 LDO使噪声频谱密度下降一半,并为VCO器件供电提供最低相位噪声,为微波系统中的时钟器件供电提供最低抖动性能。

超低噪声LDO选型表

1 噪声与固定输出电压无关

LDO 电压 电流 无线电 电子 模拟前端 电容 相关文章:

- 如何设计一个合适的系统电源(上)(11-20)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 用低压差线性稳压器优化开关电源设计(01-18)

- LDO稳压器等效串联电阻的稳定范围(01-24)

- 低电压PLD/FPGA的供电设计(01-24)

- 拥有线性稳压器特性的下一代移动DC-to-DC转换器(02-08)